Fターム[5F101BB05]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 制御装置 (5,154) | CGを有するもの (4,139) | スタックゲート(同一端部) (1,873)

Fターム[5F101BB05]に分類される特許

161 - 180 / 1,873

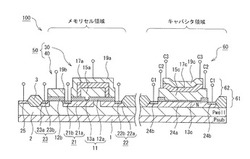

半導体装置及びその製造方法

【課題】キャパシタの高容量化と面積の低減を可能とした半導体装置及びその製造方法を提供する。

【解決手段】EEPROMメモリセル50は、シリコン基板1のメモリセル領域に設けられたN-層21aと、トンネル絶縁膜13aと、浮遊ゲート電極15aと、電極間絶縁膜

17aと、制御ゲート電極19aと、を有する。また、キャパシタ60は、シリコン基板1のキャパシタ領域に設けられた下部電極層24aと、第1の誘電体膜13cと、共通電極15cと、第2の誘電体膜17cと、上部電極19cと、を有する。下部電極層24aと第1の誘電体膜13cと共通電極15cとにより第1のキャパシタ61が構成されると共に、共通電極15cと第2の誘電体膜17cと上部電極19cとにより第2のキャパシタ62が構成されており、第1のキャパシタ61と第2のキャパシタ62とが並列に接続されている。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】3次元に積層されたメモリセルトランジスタにおける誤動作を防止する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20と、半導体基板の上方に形成された第1導電層40と、第1導電層の上方に順に積層された第2導電層43、電極間絶縁膜53’、および第3導電層43と、一対の貫通ホール49の内面上、および一対の貫通ホールの下端を連結させる連結ホール50の内面上に形成されたブロック絶縁膜53と、電荷蓄積層54と、トンネル絶縁膜55と、半導体層SPと、一対の貫通ホールの間に位置し、第2導電層、電極間絶縁膜、および第3導電層を分断するスリット46内に埋め込まれた絶縁材59と、第2導電層および第3導電層の表面上に形成されたシリサイド層58と、を具備し、スリットの内面に沿った第2導電層と第3導電層との間の距離は、積層方向に沿った第2導電層と第3導電層との距離よりも大きい。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】クラックや結晶欠陥の発生なしに高電圧トランジスタの素子領域間の耐圧を向上できるようにした不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域の第1素子分離絶縁層が当該メモリセル領域の第1素子分離溝内に第1の酸化膜を埋め込んで構成され、第1の酸化膜の上面が半導体基板の上面と第1ゲート電極の上面との間に存在するように構成されている。

周辺領域の第2素子分離絶縁層は、周辺領域の第2素子分離溝内の全体に埋込まれると共にその上面が半導体基板の上面の上方に突出した第1の酸化膜と、当該第1の酸化膜上に積層され、その上面が第1導電膜の上面より上方に突出している第2の酸化膜とで構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体集積回路内の抵抗素子の抵抗値のばらつきを抑制した半導体装置を提供する。

【解決手段】半導体装置は基板を備える。第1の絶縁膜は基板上に設けられる。第1の抵抗部は第1の絶縁膜上に設けられる。境界膜は第1の抵抗部上に設けられる。第2の抵抗部は境界膜上に設けられる。第2の絶縁膜は、第2の抵抗部上に設けられている。第1の導電部および第2の導電部は、第2の絶縁膜上に設けられ、互いに絶縁されている。第1の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第1のコネクト部を含む。第2の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第2のコネクト部を含む。第1の抵抗部は、一端において第1のコネクト部を介して第1の導電部に電気的に接続され、かつ、他端において第2のコネクト部を介して第2の導電部に電気的に接続された抵抗素子である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造工程数の削減が可能な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、第2積層体、第1、第2半導体ピラー、第1、第2メモリ膜、接続部及び分断部を備えた不揮発性半導体記憶装置が提供される。第1、第2積層体は、第1軸に沿って積層された複数の第1、第2電極膜と、第1、第2電極膜間に設けられた第1、第2電極間絶縁膜と、をそれぞれ含む。第1、第2半導体ピラーは第1、第2積層体を第1軸に沿って貫通する。第2積層体は、第1積層体と並置される。接続部は第1、第2半導体ピラーを接続する。第1メモリ膜は、第1、第2電極膜と、第1、第2半導体ピラーとの間に設けられる。分断部は、第1、第2半導体ピラー間で第1、第2電極膜を分断し、接続部に接し、第1メモリ膜に用いられる材料を含む積層膜を含む。

(もっと読む)

膜形成方法および不揮発性記憶装置

【課題】より良質な膜を形成する。

【解決手段】実施形態の膜形成方法は、下地の上に設けられた酸素及び窒素の少なくともいずれかを含む膜の表面に、酸素及び窒素の少なくともいずれかを含むイオン化されたガスクラスタを照射して、前記ガスクラスタを照射した後の前記膜の密度を前記ガスクラスタを照射する前の前記膜の密度よりも高くする。

(もっと読む)

有機分子メモリ

【課題】電荷保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、電荷蓄積型分子鎖または抵抗変化型分子鎖を含み、電荷蓄積型分子鎖または前記抵抗変化型分子鎖が縮合多環系の基を備える有機分子層と、を備えている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

不揮発性半導体記憶装置

【課題】所定のレイアウト面積内において複数の抵抗値が得られる抵抗素子を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板13上に配置された絶縁膜14と、絶縁膜14上に配置された導電層12と、導電層12上に配置された絶縁膜16と、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Aと、導電層11Aに接続されたコンタクト24Aと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Bと、導電層11Bに接続されたコンタクト24Bと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Cと、導電層11Cに接続されたコンタクト24Cとを備える。導電層12はフローティングゲート層と同じ材料から形成され、導電層11A、11B、11Cはコントロールゲート層と同じ材料から形成されている。

(もっと読む)

半導体記憶装置

【課題】メモリアレイの周辺に配置される周辺回路の専有面積を小さくすることができる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、メモリアレイと、周辺回路と、を備える。メモリアレイは、複数のメモリセルと、複数のワード線と、複数のビット線と、を有し、4つのブロックを有する。周辺回路は、第1ブロックに属するワード線に接続された第1転送トランジスタと、第2ブロックに属する前記ワード線に接続された第2転送トランジスタと、第3ブロックに属するワード線に接続された第3転送トランジスタと、を含むトランジスタグループを有する。第1〜第3転送トランジスタにおいては、それぞれのソース及びドレインのいずれか他方を共有し、ソース及びドレインのいずれか一方と他方とをむすぶ方向が隣り合う転送トランジスタどうしで互いに90°または180°異なる。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリ容量を容易に調整することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、Y方向に配列された4つのP型ウェルPWのうちの端の1つのP型ウェルPWに複数のメモリブロックMB0〜MB3を設け、残りの3つのP型ウェルPWにそれぞれ3つのメモリブロックMB10〜MB12を設ける。また、それぞれメモリブロックMB0〜MB3,MB10〜MB12のX方向に隣接してロウデコーダRD0〜RD3,RD10〜RD12を設ける。メモリブロックMB10〜MB12を削除してメモリ容量を減らす場合でも、周辺回路の再レイアウトが不要となる。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流の発生を防止でき、微細化に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、素子分離膜により分離される素子領域を有する半導体基板31と、前記素子領域上にゲート絶縁膜を介して設けられる第1導電層FGと、前記第1導電層および前記素子分離膜上に設けられ、前記第1導電層上に開口を有するゲート間絶縁膜IPDと、前記ゲート間絶縁膜を介して、前記素子領域上および前記素子分離膜上にわたって配置される第2導電層CG1と、前記第1導電層上に設けられ、周囲の溝により前記第2導電層と電気的に分離され、前記ゲート間絶縁膜の前記開口を介して前記第1導電層と接続される第3導電層CG2と、前記第1導電層を挟むように、前記素子領域中に隔離して設けられるソースまたはドレイン拡散層38とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

半導体記憶装置

【課題】集積度が高く、データ保持時間の長い半導体記憶装置。

【解決手段】基板上の半導体膜と、半導体膜を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を介して半導体膜上に設けられた第1のゲート電極と、第1のゲート絶縁膜上にあり、半導体膜と重畳しない、第1のゲート電極と同一層かつ同一材料である第1の導電膜と、第1のゲート絶縁膜上にあり、第1のゲート電極および第1の導電膜の上面を露出し、第1のゲート電極および第1の導電膜の間に溝部を有する絶縁膜と、該絶縁膜上にあり、第1のゲート電極、第1の導電膜および溝部と接する酸化物半導体膜と、酸化物半導体膜を覆う第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜および溝部上に設けられた第2のゲート電極と、第2のゲート絶縁膜および酸化物半導体膜を介して第1のゲート電極上に設けられた、第2のゲート電極と同一層かつ同一材料である第2の導電膜と、を有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルの高集積化を図ることができる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板上に設けられた複数本の第1積層体と、前記複数本の第1積層体が配置された領域の外側に配置された第2積層体と、前記第1積層体及び前記第2積層体を覆う層間絶縁膜と、を備える。前記第1積層体と前記第2積層体との距離は、隣り合う前記第1積層体間の距離よりも長く、前記層間絶縁膜における前記第1積層体の相互間には第1の空隙が形成されており、前記層間絶縁膜における前記第1積層体と前記第2積層体との間には第2の空隙が形成されている。そして、前記第2の空隙の下端は、前記第1の空隙の下端よりも上方に位置している。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な半導体装置を提供する。

【解決手段】P型の半導体基板10と、半導体基板10内に形成されるNウェル11、半導体基板10内かつNウェル11上に形成されるPウェル12、及びPウェル12上に形成されるメモリセルトランジスタMTを含むCell領域と、半導体基板10内に形成されるNウェル14、及びNウェル上14に形成されるトランジスタHVP−Trを含むHVP−Tr領域と、半導体基板10上に形成されるトランジスタHVN―Trを含むHVN―Tr領域と、半導体基板10内に形成されるNウェル22、半導体基板10内かつNウェル22上に形成されるPウェル23、およびPウェル23上に形成されるトランジスタLVNE−Trを含むLVNE−Tr領域と、を具備し、Nウェル11及びNウェル22の底面の位置はNウェル14の底面の位置よりも低く、Nウェル14の底面の位置はPウェル12及びPウェル23の底面の位置よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】実施形態によれば、十分な消去速度が得られる半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、第1の積層体と、メモリ膜と、第1のチャネルボディと、第2の積層体と、ゲート絶縁膜と、第2のチャネルボディとを備えている。前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成されている。前記段差部を被覆する部分の前記第2のチャネルボディの膜厚は、前記第2の絶縁層間に設けられた部分の膜厚よりも厚い。

(もっと読む)

半導体メモリ

【課題】 本発明の実施形態によれば、信頼性の高い半導体メモリを提供することができる。

【解決手段】 半導体メモリは、半導体基板のチャネル領域上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成された電荷蓄積膜と、前記電荷蓄積膜上に形成されたブロック絶縁膜と、ブロック絶縁膜上に形成されたゲート電極とを備え、トンネル絶縁膜内にはクーロンブロッケイド条件を満たす導電性微粒子を含む微粒子層がある。

(もっと読む)

161 - 180 / 1,873

[ Back to top ]