Fターム[5F101BB17]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 容量解析 (181)

Fターム[5F101BB17]に分類される特許

161 - 180 / 181

半導体装置およびカップリング比検出装置

【課題】 フラッシュメモリセルのカップリング比を高精度で検出する。

【解決手段】 ダミーメモリセルトランジスタ(MCT)およびフローティングゲートとコントロールゲートが短絡された参照フローティングゲートトランジスタ(DT)のゲートを充放電して、直流電流をそれぞれ検出して、これらのトランジスタ(MCT,DT)のゲート容量を算出する。この算出したゲート容量に基づいて、ゲートカップリング比αcgを算出する。

(もっと読む)

フラッシュメモリ素子のフローティングゲート電極形成方法

【課題】フローティングゲート電極間のブリッジ発生を抑制し、カップリング比を増加させるフラッシュメモリ素子のフローティングゲート電極形成方法の提供。

【解決手段】半導体基板上にフローティングゲート電極用第1シリコン膜、パッド窒化膜を形成し、トレンチを定義する段階と、前記定義されたトレンチに埋め込み絶縁膜を形成し、前記パッド窒化膜が露出するまで平坦化工程を行い、素子分離膜を形成する段階と、前記パターニングされたパッド窒化膜を除去し、前記パッド窒化膜が除去された領域にフローティングゲート電極用第2シリコン膜を形成する段階と、前記第2シリコン膜上にシリンダ型フローティングゲート電極形成用パターンを形成し、これをエッチングマスクとして前記第2シリコン膜にエッチング工程を行い、前記フローティングゲート電極用第1シリコン膜上にシリンダ型フローティングゲート電極パターンを形成する段階とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】特性劣化の抑制およびカップリング比の増大を図れる、浮遊ゲート電極および制御ゲート電極を含む不揮発性メモリセルを提供すること。

【解決手段】 不揮発性メモリセルは、アクティブエリア1AA上に設けられたトンネル絶縁膜2と、トンネル絶縁膜2上に設けられた浮遊ゲート電極3と、浮遊ゲート電極3の上方に設けられた制御ゲート電極10と、浮遊ゲート電極3と制御ゲート電極10との間に設けられた電極間絶縁膜9とを含み、チャネル幅方向の断面において、アクティブエリア1AAの上面のチャネル幅方向の寸法は、トンネル絶縁膜2の下面のチャネル幅方向の寸法よりも短く、かつ、アクティブエリア1AAと対向する部分のトンネル絶縁膜2の面積は、浮遊ゲート電極3の上面と対向する部分の電極間絶縁膜9の面積より小さい。

(もっと読む)

半導体記憶装置

【課題】 セクタ単位での消去を可能とした半導体記憶装置を提供する。

【解決手段】 セルアレイ2内のワード線を8本ごとに区分し、各ブロックに消去セクタES0〜ES15を構成する。シリコン基板に所定の負電圧を印加した状態で、消去対象の消去セクタに属する8本のワード線に所定の正電圧を印加するとともに、その他の消去対象外の消去セクタに属するワード線を接地することにより、消去対象の消去セクタに属するメモリセルには消去動作を行わせ、消去対象外の消去セクタに属するメモリセルには消去動作を行わせない。これにより上記消去セクタ単位でのセクタ消去が実現される。セルアレイ2内にはメモリセルが2次元マトリクス状に配列されている。メモリセルは、1対のフローティングゲートを有し、2ビット以上のデータを書き替え自在に保持することができる。

(もっと読む)

不揮発性メモリのプログラム電圧決定方法

【課題】

ホットキャリア注入によるプログラム後のメモリセルの閾値電圧のバラツキを抑制可能な不揮発性メモリのプログラム電圧決定方法を提供する。

【解決手段】

ドレイン電圧を所定電圧に設定する設定ステップと、ドレイン電圧と所定のゲート電圧を所定のプログラミング時間で印加するプログラムステップと、ドレイン電圧の設定電圧を変更する変更ステップと、設定電圧変更後のドレイン電圧で、該プログラムステップを実行する再プログラムステップと、プログラム後の閾値電圧を測定する測定ステップと、再プログラムステップ後の閾値電圧における、ドレイン電圧の変化量に対する閾値電圧の変化量の比で表される微分値を検出する検出ステップを有し、検出された微分値と測定された閾値電圧の両方が所定の許容範囲内にある場合に、変更されたドレイン電圧を最適値として決定する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 誤動作耐性を向上させ、ひいては書き換え耐性を向上することのできる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】 本発明のフラッシュメモリは、主表面を有する半導体基板2と、ビット線BL1と、半導体基板2の主表面上に形成された積層ゲート電極SG1,SG2と、積層ゲート電極SG1と積層ゲート電極SG2との間の半導体基板2の主表面に形成されたソース3bと、積層ゲート電極SG1を間に挟んでソース3bの反対側の半導体基板2の主表面に形成されたドレイン3aと、積層ゲート電極SG2を間に挟んでソース3bの反対側の半導体基板2の主表面に形成されたドレイン3cとを備えている。ドレイン3aとドレイン3cとが共に同一のビット線BL1に電気的に接続されている。さらに、積層ゲート電極SG1と積層ゲート電極SG2との間に形成され、かつ一定電位に固定されたシールド導電層1を備えている。

(もっと読む)

改良された浮遊ゲート絶縁と浮遊ゲートの製造方法

この発明は、互いにスリットにより分離されている複数の浮遊ゲートを形成する方法、並びに、その浮遊ゲートを用いた半導体装置に関する。この発明は、各々が浮遊ゲート(36)を有する複数半導体装置のアレイを基板(10)上に製造する方法であって、最初に、基板(10)内に複数絶縁領域(14)を形成し、その後、隣接浮遊ゲート(36)間に分離部が形成される位置において、複数絶縁領域(14)上に浮遊ゲート分離部(32)を形成し、浮遊ゲート分離部(32)形成後、浮遊ゲート分離部(32)の部分間において、基板(10)上に複数浮遊ゲート(36)を形成し、その後、隣接浮遊ゲート(36)間にスリットを得るために浮遊ゲート分離部(32)を除去する工程を備えた方法を提供する。この発明は、従来技術に対し、浮遊ゲート材料残留物が少なく、即ち、浮遊ゲート材料による隣接浮遊ゲート間の短絡が少ないという有利な点がある。さらに、従来スリット処理技術に比べてゲート特性が悪くならない。  (もっと読む)

(もっと読む)

不揮発性メモリ素子とその製造方法

【課題】不揮発性メモリ素子とその製造方法を提供する。

【解決手段】本発明の半導体素子は、半導体基板上に配置され絶縁されたフローティングゲートと、フローティングゲートの少なくとも一側面に形成された絶縁されたプログラムゲートと、フローティングゲートに隣接して配置され絶縁された消去ゲートと、を含む。これにより、より低い電圧でプログラム又は消去動作が可能であり、従来の不揮発性メモリ素子のサイズに比べて効果的に素子のサイズを縮小させることができ、消去動作電圧を減少させうる。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するメモリセル間の干渉に起因するメモリセルの誤動作を回避する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一形態の半導体装置は、複数のメモリセルを備えた半導体装置であって、半導体基板(1)上にトンネル絶縁膜(2)を挟んで設けられ、上部のチャネル幅方向の幅が下部のチャネル幅方向の幅よりも短い複数の浮遊ゲート電極(3)と、前記浮遊ゲート電極上に設けられた電極間絶縁膜(5)と、前記浮遊ゲート電極上に前記電極間絶縁膜を挟んで設けられ、互いに対向する前記浮遊ゲート電極の間に一部が埋め込まれている制御ゲート電極(6)と、を備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 フローティングゲートとコントロールゲート間の層間絶縁膜をエッチングする際に下地の絶縁膜がエッチングされることに起因するデバイス特性劣化を防止することができる不揮発性半導体記憶装置を提供する。

【解決手段】 半導体基板1と、ゲート絶縁膜2と、半導体基板1の主表面の法線と成す角度θが0度より大きく45度以下となるように傾斜する側面を含み、上方に向かうに従って幅寸法が漸次狭くなるように形成された複数のフローティングゲート8a〜8cと、フローティングゲート8a〜8c間に形成された絶縁膜30と、層間絶縁膜9と、コントロールゲートとを備え、絶縁膜30上でフローティングゲート8a〜8cが分断され、層間絶縁膜9の厚みをTとした場合に絶縁膜30の厚みが、T/sinθ以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体基板主面上の段差に起因するフローティングゲート材のエッチング不足による残渣の発生を防止する。

【解決手段】 半導体基板主面上にアシストゲート及びキャップ絶縁膜を積層した半導体装置において、前記アシストゲートのゲート長よりも小さな長さで前記キャップ絶縁膜を形成し、前記半導体基板主面上から前記アシストゲート及びキャップ絶縁膜の側面にわたってフローティングゲートを形成する。また、その製造方法では、前記アシストゲートのゲート長よりも小さな長さで前記キャップ絶縁膜を形成する工程と、前記半導体基板主面上から前記アシストゲート及びキャップ絶縁膜の側面にわたってフローティングゲートを形成する工程とを有する。

(もっと読む)

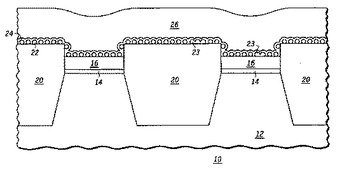

浮遊ゲート装置において結合係数が改善された自己整合シャロートレンチ分離

本発明は、表面(2)を有する基板上に浮遊ゲート型半導体装置を製造する方法、及びそれによって製造した浮遊ゲート型半導体装置を提供する。本方法は、絶縁膜(4)、浮遊ゲート材料の第1の層(6)及び犠牲材料の層(8)を備えるスタックを基板表面に形成し、スタックを通って、基板(2)中に、少なくとも1つの分離領域(18)を形成し、それによって浮遊ゲート材料の第1の層(6)が上表面及び側壁(26)を有し、犠牲材料(8)を除去し、それによって分離領域(18)及び浮遊ゲート材料の第1の層(6)の上表面によって画定される空所(20)を残し、空所(20)を浮遊ゲート材料の第2の層(22)で充填し、それによって浮遊ゲート材料の第1の層(6)及び浮遊ゲート材料の第2の層(22)が共に浮遊ゲート(24)を形成する工程を備える。  (もっと読む)

(もっと読む)

半導体装置、及びその製造方法

【課題】 単層ポリシコンゲートから成る不揮発性メモリのセル面積を低減し、かつ超低消費電力で動作させる。

【解決手段】 フローティングゲート6端下部のN型ウエル4の基板表面に、ゲート酸化膜5を介在させて設けられたP型不純物領域8と、前記N型ウエル4が構成する接合に−5Vのような逆バイアス電圧を印加して、バンド間トンネル現象によって発生するホットエレクトロンを前記フローティングゲート6へ注入して書込みを行う。書込み時間はおおよそ10μs、書込み動作時の前記接合の漏洩電流は100nA程度に設計できるため、書込みに要するエネルギーは5pJまで低減され、従来のスタックド・ゲート型メモリセルのチャンネルホットエレクトロン注入を用いた書込みのエネルギーに比較して1/100以下に低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 誘電膜の面積がさらに拡張する半導体装置及びその製造方法を提供する。

【解決手段】 基板40には第1方向へ互いに反復的に配置されるアクティブ領域42とフィールド領域43とが画定される。基板40のアクティブ領域42上にはトンネル酸化膜パターン45が形成され、トンネル酸化膜パターン45上には第1ゲートパターン48が部分的に形成される。第1ゲートパターン48の表面及び第1ゲートパターン48から露出するトンネル酸化膜パターン45の表面上に形成される第1誘電膜パターン49aと、第1方向に直交する第2方向へ第1ゲートパターン48の表面、第1ゲートパターン48に隣接するフィールド領域43の表面及びフィールド領域43に隣接する第1ゲートパターン48の表面上に連続的に形成される第2誘電膜パターン49bとを含む誘電膜パターンが形成される。これにより、誘電膜パターンが有する面積が拡張される。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

フローティングゲートなどの電荷記憶素子のアレイのうちの個々の素子が少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムを開示する。コントロールゲートラインは、好ましくはフローティングゲートの側壁と結合するようにフローティングゲート間に位置している。その結果として、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、その選択された行の両側の直ぐ近くの隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。その選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させることもできる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 メモリセルのキャパシタンス比を大きくすることができ、しかもフローティングゲート間にコントロールゲートを確実に形成することが可能な半導体装置を提供する。

【解決手段】 第1の方向及び第1の方向に垂直な第2の方向に配列した複数のメモリセルを備えた半導体装置であって、各メモリセルは、半導体基板101上に形成された第1の絶縁膜102と、第1の絶縁膜上に形成されたフローティングゲート103と、フローティングゲートの上面に形成された第1の部分と、フローティングゲートの第1の方向に平行な側面に形成された第2の部分とを含む第2の絶縁膜109と、第2の絶縁膜の第1及び第2の部分を覆うコントロールゲート110とを備え、フローティングゲートの第2の方向における幅は下部から上部に向かって増加し、第2の絶縁膜の第2の部分の第2の方向における幅は下部から上部に向かって減少している。

(もっと読む)

半導体装置

【課題】 半導体装置において、セル面積の縮小化を図ることにある。

【解決手段】 半導体装置100は、半導体基板10と、半導体基板10の内部に形成され、コントロールゲートとして機能する不純物領域22と、半導体基板10の上方に形成されたゲート絶縁層16と、ゲート絶縁層16の上方に、不純物領域22とオーバーラップして形成されたフローティングゲート18と、フローティングゲート18の上方に形成された層間絶縁層50と、層間絶縁層50の上方に、フローティングゲート18とオーバーラップして形成された遮光層52と、を含む。遮光層52は、不純物領域22と電気的に接続している。

(もっと読む)

不揮発性半導体記憶装置

【課題】 複数のスタックゲート型メモリセルを含むフラッシュメモリにおいて、消去前書込動作を不要とすることにより一括消去動作に要する時間を短縮し、データの書換動作に要する時間も短縮することである。

【解決手段】 消去時に、複数のメモリセルのソース1003からフローティングゲート1005に同時に電子を注入する。それにより、複数のメモリセルのしきい値電圧が上昇する。プログラム時に、選択されたメモリセルのフローティングゲート1005からドレイン1002に電子を放出する。それにより、選択されたメモリセルのしきい値電圧が下降する。

(もっと読む)

改良された表面形状を用いるメモリ構造の形成方法及びその構造。

半導体装置10のゲートカップリング比を増大させるため、超微細結晶等の個別素子22が浮遊ゲート16上に析出される。一実施形態において、個別素子22は、蒸気相中で予め形成され、静電気力によって半導体装置10に吸着される。一実施形態において、個別素子22は、それらが吸着されるチャンバとは異なるチャンバ内で予め形成される。更に別の実施例において、同じチャンバが全ての析出工程に使用される。界面層17は、必要に応じて、浮遊ゲート16と個別素子22との間に形成される。  (もっと読む)

(もっと読む)

High−K材料とゲート間プログラミングとを使用する不揮発性メモリ・セル

不揮発性メモリ・デバイスは、ソース/ドレイン領域の間のチャネル領域と、フローティング・ゲートと、制御ゲートと、チャネル領域とフローティング・ゲートとの間の第1の誘電体領域と、フローティング・ゲートと制御ゲートとの間の第2の誘電体領域とを有する。第1の誘電体領域はHigh−K材料を含む。不揮発性メモリ・デバイスは、フローティング・ゲートと制御ゲートとの間で第2の誘電体領域を介して電荷を移動させることによってプログラムおよび/または消去される。 (もっと読む)

161 - 180 / 181

[ Back to top ]