Fターム[5F101BC11]の内容

不揮発性半導体メモリ (42,765) | 電荷注入 (1,823) | チャンネル注入 (848)

Fターム[5F101BC11]の下位に属するFターム

不均一電界 (31)

キャリア走行方向、段差 (12)

Fターム[5F101BC11]に分類される特許

161 - 180 / 805

半導体記憶装置

【課題】メモリウィンドウが大きく信頼性の高い半導体記憶装置を提供することを課題とする。

【解決手段】表面が絶縁体からなる支持基板の上に設けられた半導体層と、前記半導体層内に設けられた、第1の導電型の2つの拡散層領域と、前記2つの拡散層領域の間の前記半導体層内に位置するチャネルと、前記チャネルの上に設けられたゲート絶縁膜と、前記ゲート絶縁膜の上に設けられたゲート電極と、を有し、前記ゲート絶縁膜は、電荷蓄積機能を有し、前記ゲート電極は、その少なくとも一部がリング状平面構造をなし、前記2つの拡散層領域の一方が、前記リング状平面構造の内側に存在し、他方が前記リング状平面構造の外側に存在することを特徴とする半導体記憶装置により上記課題を解決する。

(もっと読む)

3次元半導体装置及びその動作方法

【課題】3次元半導体装置及びその動作方法を提供する。

【解決手段】3次元半導体装置及びその動作方法が提供される。この装置は、基板上に配置される複数のワードライン構造体と、ワードライン構造体の間に介在される活性半導体パターンと、ワードライン構造体と活性半導体パターンとの間に介在される情報格納要素とを具備する。ワードライン構造体の各々は、互いに離隔されながら積層された複数のワードラインを具備するとともに、活性半導体パターンは、互いに異なる導電型を有しながら交互に配列される電極領域と、チャンネル領域とを具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】第1ゲート電極と第2ゲート電極間の寄生容量の少なく高速アクセスが可能なソースサイド注入方式のスプリットゲート型不揮発性メモリセルを備えた不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルが、書き込み・消去用の第1メモリセルユニットU1と、読み出し用の第2メモリセルユニットU2と、第3メモリセルユニットU3とを備えてなり、第1メモリセルユニットU1の第2ゲート電極7、第2メモリセルユニットU2の第3ゲート電極11、第3メモリセルユニットU3の第4ゲート電極13同士が電気的に接続してフローティングゲートFGが形成される。第4ゲート電極13上に第2の絶縁膜を介して第5ゲート電極15が形成され、第5ゲート電極15が制御端子CGと電気的に接続することにより、フローティングゲート7,11,13が制御端子CGと容量結合している。

(もっと読む)

半導体装置、及びその製造方法

【課題】ショートの発生と面積の増大とを抑止しつつ、誤書き込みの防止が可能な半導体装置、及びその製造方法を提供すること

【解決手段】本発明にかかる半導体装置は、第1メモリセル領域40a内で、Y方向にソース拡散層を挟んで隣接する第1メモリセル80a及び第2メモリセル80bと、第2メモリセル領域40b内で、第2メモリセル80bのX方向側に配置された第3メモリセル80gと、第3メモリセル領域40c内で、第1メモリセル80aのX方向側に配置された第4メモリセル80hと、第1メモリセル80aと第3メモリセル80gのワードゲートWGを接続する第1接続部91aと、第2メモリセル80bと第4メモリセル80hのワードゲートWGを接続する第2接続部91bとを備え、4つのメモリセル80a、80b、80g、80hのコントロールゲートCGが、それぞれ分離して形成されているものである。

(もっと読む)

不揮発性メモリ装置のプログラム方法

【課題】不揮発性メモリ装置のプログラム方法を提供する。

【解決手段】本発明は、プログラムされるデータによって選択されたメモリセルのチャンネルをフローティングさせる段階と、前記選択されたメモリセルと非選択されたメモリセルの間にゲート有機ドレーン漏れが発生するように前記選択された及び非選択されたメモリセルのワードラインを駆動する段階とを具備する不揮発性メモリ装置のプログラム方法を提供する。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体を設ける。電極膜14は、X方向に延びる複数本の制御ゲート電極CGに分断する。また、積層体内に、選択ゲート電極SGb、SGs、制御ゲート電極CG1〜CG4を貫き、一端がソース線SLに接続され、他端がビット線BLに接続されたU字ピラー30を設ける。そして、最上層の制御ゲート電極CG4に、他の制御ゲート電極CG1〜CG3とは異なる電位を印加する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】不揮発性メモリを備える半導体装置の歩留まりを向上させることの可能な半導体装置の製造方法および方法により得られた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、不揮発性メモリ形成領域のドレイン形成領域側において、ダミーゲート16に対向しない第2ゲート電極14の側壁に形成された第2サイドウォール43のゲート長方向の幅が、ソース形成領域側において、第2ゲート電極14の側壁に形成された第2サイドウォール43のゲート長方向の幅Xよりも長い第2サイドウォール43を得る工程を含む。

(もっと読む)

半導体集積回路装置

【課題】ラッチ型メモリセルのラッチ部のサイズを増大させることなく、データ保持特性を改善する。

【解決手段】ラッチ型メモリセルの記憶ノードを構成するゲート電極配線(21a,21c)と交差する方向に、フラッシュメモリセルトランジスタの固有の配線と同一配線層の導電線(26a,26b)を連続的に延在させて配置する。ゲート電極配線と導電線の交差部において容量を形成し、導電線を固定電位に維持する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体記憶装置(メモリ)を構成するスプリットゲート型トランジスタで発生するディスターブを抑制して、半導体装置の信頼性を向上することができる技術を提供する。

【解決手段】メモリセル領域に形成されているメモリセルには、コントロールゲート電極CGの側壁に電位障壁膜EV1、電荷蓄積膜ECおよび電位障壁膜EV2を介して、サイドウォール形状のメモリゲート電極MGが形成されている。このとき、メモリセルのコントロールゲート電極CGは矩形形状をしており、ゲート絶縁膜GOXに接する辺の端部に形成される角部が逆テーパ形状に加工されている点に特徴がある。

(もっと読む)

固体撮像素子及び撮像装置

【課題】ノイズの原因となる電荷の注入を防止することができる固体撮像素子及び撮像装置を提供する。

【解決手段】固体撮像素子は、光電変換部3と、半導体基板上に設けられた絶縁膜と、絶縁膜上に設けられた電荷蓄積部と、光電変換部3で発生した電荷を電荷蓄積部に注入するゲート電極を含むトランジスタとを有する固体撮像素子であって、トランジスタのドレイン領域の上方の絶縁膜の少なくとも一部が他の部分よりも厚く形成されている。

(もっと読む)

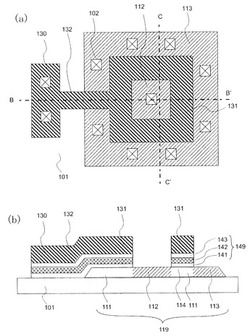

メモリ素子、半導体記憶装置、表示装置、および携帯電子機器

【課題】チャネル領域の端部に起因するリーク電流を低減し、低電圧で動作し安定したメモリ特性(書込み、消去、読出し)を有する不揮発性のメモリ素子、メモリ素子を備える半導体記憶装置、表示装置、および表示装置を備える携帯電子機器を提供する。

【解決手段】メモリ素子1は、支持基板10と、支持基板10に積層され対向するソース領域11sおよびドレイン領域11dを有する半導体層11と、ソース領域11sおよびドレイン領域11dの間で半導体層11に形成されたチャネル領域11cと、チャネル領域11cに積層され電荷蓄積機能を有する第1ゲート絶縁膜13と、第1ゲート絶縁膜13を被覆する第1ゲート電極17と、チャネル領域11cのチャネル幅方向Dcwの端部11ctを被覆し第1ゲート絶縁膜13の膜厚Tg1と異なる膜厚Tg2を有する第2ゲート絶縁膜15を備え、第1ゲート電極17は、第2ゲート絶縁膜15を被覆している。

(もっと読む)

撮像装置及び固体撮像素子の駆動方法

【課題】ノイズを抑えながら電荷蓄積部内の電荷を消去することが可能な撮像装置及び固体撮像素子の駆動方法を提供する。

【解決手段】光電変換部3を含む画素部100を多数有する撮像装置であって、画素部100は、光電変換部3で発生した電荷を蓄積するための半導体基板上方に設けられたフローティングゲートFGを含む書き込みトランジスタWTと読み出しトランジスタRTを有し、複数の画素部100からなるグループ毎に、該グループ内の画素部100の光電変換部3で発生した電荷を該画素部100内の書き込みドレインWD又は読み出しドレインRDに排出する第一の電荷排出駆動を独立に行って、各グループの露光期間の開始タイミングを制御する制御部40を備える。

(もっと読む)

不揮発性半導体装置及び不揮発性半導体装置の製造方法

【課題】ONO膜とシリサイド膜との短絡を起こさないようにし、ONO膜での電荷の不安定や電解分布の不均一、ONO膜の膜質低下などを防止する。

【解決手段】不揮発性半導体記憶装置はワードゲート22とコントロールゲート24と電荷蓄積層14とを具備する。ワードゲート22は半導体基板10のチャネル領域上方に絶縁層12を介して設けられている。コントロールゲート24はワードゲート22の側方に設けられている。電荷蓄積層14はチャネル領域とコントロールゲート24との間、及び、ワードゲート22とコントロールゲート24との間にONO膜で設けられている。コントロールゲート24は、シリサイド層24aと、非シリサイド層24b、24cとを備える。シリサイド層24aはニッケルを含むシリサイドで設けられている。非シリサイド層24b、24cはシリサイド層24aと電荷蓄積層14との間に設けられている。

(もっと読む)

電子素子の電子ブロック層

不揮発性メモリ素子などの電子素子用の方法および装置が記載される。メモリ素子は、2層または3層などの多層の制御誘電体を含む。多層制御誘電体は、酸化アルミニウム、酸化ハフニウム、および/または、酸化ハフニウムアルミニウムのハイブリッド膜などの高k誘電体材料の組み合わせを含む。多層制御誘電体により、単一または多状態(例えば、2ビット、3ビット、または4ビット)動作の実現可能性を備えながら、増大された電荷保持、向上されたメモリプログラム/消去ウィンドウ、改善された信頼性および安定性を含む向上された特性を与える。  (もっと読む)

(もっと読む)

半導体記憶装置およびその製造方法

【課題】カップリング比の増大を図ることができる、半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体基板2に形成されたトレンチ3には、埋設絶縁体4が埋設されている。埋設絶縁体4の上部は、半導体基板2の表面よりも上方に突出している。半導体基板2の表面上には、トンネル酸化膜5が形成されている。埋設絶縁体4の側方において、トンネル酸化膜5上には、フローティングゲート6が形成されている。フローティングゲート6の側部は、埋設絶縁体4の上方に迫り出し、その側面は、平面10およびその下方に連続する曲面11からなる。フローティングゲート6の上面12ならびに平面10および曲面11からなる側面上には、ONO膜13がそれらの各面に接して形成されている。そして、ONO膜13上には、コントロールゲート14が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】多結晶シリコン膜上に成膜されたシリコンナイトライド膜を除去する際に、多結晶シリコン膜にシリコンダストが付着することを防止する。

【解決手段】 本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜4、多結晶シリコン膜5、親水性を有する膜22、シリコンナイトライド膜23およびシリコン酸化膜24を積層形成し、シリコン酸化膜24とシリコンナイトライド膜23と親水性を有する膜22を加工し、シリコン酸化膜をマスクにして多結晶シリコン膜5を加工し、シリコン酸化膜をマスクにしてゲート絶縁膜4およびシリコン基板1を加工して素子分離溝20を形成し、素子分離溝20内に素子分離絶縁膜21を埋め込み、ウエットエッチングによりシリコンナイトライド膜23を除去することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】メモリセルの微細加工のばらつきを抑制することができる半導体装置の製造方法を提供する。

【解決手段】電荷蓄積層とゲート電極層とを有する積層された層SL上に、第1の開口部OP1を有し、灰化可能な材質を含有する第1の層101が形成される。第1の開口部OP1を狭める第1の側壁膜201が形成される。第1の層101が灰化される。第1の側壁膜201の平面形状に対応する平面形状を有するように、積層された層SLがパターニングされる。パターニングにおいて、第1の側壁膜201をマスクとして用いたエッチングがなされる。積層された層SLをマスクとして用いて拡散層70が形成される。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】カップリング比を減少させずにゲート電極と不純物拡散領域との位置が整合して形成される不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板に形成される複数の不純物拡散領域と、前記半導体基板上に形成される絶縁膜と、隣り合う前記不純物拡散領域を繋ぐように前記半導体基板上に前記絶縁膜を介して形成されるフローティングゲート電極と、前記フローティングゲートの上面及び側面に形成されるゲート間絶縁膜と、前記ゲート間絶縁膜を介して前記フローティングゲート電極の上面及び両側面と接するように形成されるコントロールゲート電極とを備える。

(もっと読む)

不揮発性半導体メモリセル及び不揮発性半導体メモリ装置

【課題】レイアウト面積を削減し、且つ、記憶保持の信頼性を向上する不揮発性半導体メモリ装置を提供する。

【解決手段】不揮発性半導体メモリセルは、第1の選択トランジスタ、2つのフローティングゲート型のメモリ素子及び第2の選択トランジスタの順に直列に接続し、レイアウトとしては、トランジスタ形成部220にそれぞれの素子のドレイン及びソースを直列に配置し、メモリ素子のコントロールゲート電極であるn+型拡散層219をトランジスタ形成部と平行に配置し、メモリ素子のフローティングゲートであるポリシリコン203a、203bをトランジスタ形成部220とn+型拡散層219とに垂直に交わる方向に配置し、第1の選択トランジスタ及び第2の選択トランジスタのゲート電極であるポリシリコン214a、214bをトランジスタ形成部220と垂直に交わる方向に配置する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】標準ロジックのCMOSプロセスで不揮発性メモリを実現し、メモリセルの面積を最小限にすると共に、OTPおよびMTPを実現する。

【解決手段】トランジスタ形成部3を上下方向に配置し、トランジスタ形成部3の左側にメタル配線12を配置しドレインと接続する。また、ソースに接続されるメタル配線13を左右方向に配置する。またトランジスタ形成部3の左側にn型ウェル2を配置し、このn型ウェル2の表面とトランジスタのゲート領域部(符号4で示す領域)とに対向するようにフローティングゲート9を左右方向に配置し、フローティングゲート9に電位を付与するコントロールゲート配線19も左右方向に配置する。そして、ドレインDとコントロールゲートCGとソースSに印加する信号を制御することにより、このメモリセルをOTPまたはMTPとして動作させる。

(もっと読む)

161 - 180 / 805

[ Back to top ]