Fターム[5F101BD04]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | SD領域 (1,220) | S・D平面形状 (20)

Fターム[5F101BD04]に分類される特許

1 - 20 / 20

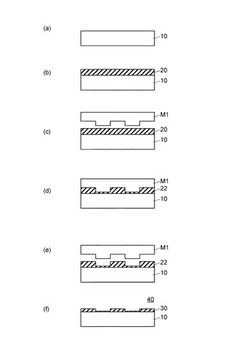

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

フィン型不揮発性メモリ素子

【課題】不揮発性メモリ素子は小型化や低消費電力化の要求がある。不揮発性メモリ素子をフィン型とすれば小型化できるが、バルク領域に正しく電位を印加できないので正しく情報の書き込みと消去とができなかった。

【解決手段】本発明のフィン型不揮発性メモリ素子は、不揮発性メモリ素子のゲート電極とは別に、バルク領域に直接電位を印加するバルク電極を設けた。これにより、バルク領域の電位を自由に印加できるようになり、正しく情報が書き込み及び消去できるようになる。また、バルク電位を自由に可変できるので、書き込みや消去にかかる電圧を低下させることもでき、低消費電力化を行える。

(もっと読む)

半導体装置

【課題】書き込みおよび消去特性が良好で、記憶情報の不揮発性が高い不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、第1不純物領域1、第2不純物領域2、並びに第1不純物領域1および第2不純物領域2のいずれとも離間して形成された一組のソース領域3およびドレイン領域4、が区画された半導体基板10と、半導体基板10の上に形成された絶縁膜と、フローティングゲート30と、を有し、フローティングゲート30は、平面視において、第1部分31は第1不純物領域1に重複し、第2部分32は第1不純物領域1および第2不純物領域2の間に位置し、第3部分33は一組のソース領域3およびドレイン領域4の間に位置し、フローティングゲート30の第3部分33と半導体基板10との間に位置する絶縁膜は、フローティングゲート30の他の部分と半導体基板10との間に位置する絶縁膜よりも厚みが大きい。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

Pチャネル型不揮発性メモリ及び半導体装置、Pチャネル型不揮発性メモリの製造方法

【課題】書き換え電圧を低くできるようにしたPチャネル型不揮発性メモリ及び半導体装置、Pチャネル型不揮発性メモリの製造方法を提供する。

【解決手段】シリコン基板1に設けられたN型ウェル領域2と、N型ウェル領域2内で互いに離れた状態で設けられた第1のP型拡散領域(ソース)及び第2のP型拡散領域(ドレイン)と、第2のP型拡散領域上に設けられたトンネル絶縁膜14bと、N型ウェル領域2のうちの第1のP型拡散領域と第2のP型拡散領域とに挟まれた領域(即ち、チャネルとなる領域)上に設けられたゲート絶縁膜14aと、ゲート絶縁膜14a上からトンネル絶縁膜14b上にかけて連続して設けられた浮遊ゲート電極15と、を備え、第2のP型拡散領域はトンネル絶縁膜14bの直下の全領域に配置されている。

(もっと読む)

不揮発性半導体記憶装置とその駆動方法および電子機器

【課題】周辺回路の増大を極力抑えつつ、データディスターブを改善する不揮発性半導体記憶装置を提供する。

【解決手段】第1ボディ領域100上に不純物拡散層104,124を、第1不純物拡散層104上に第2ボディ領域106を形成する。第1不純物拡散層104はメモリトランジスタMTのドレイン領域と選択トランジスタSTのソース領域、第1不純物拡散層124は選択トランジスタSTのドレイン領域をなす。第2ボディ領域106と第1不純物拡散層104に跨るように第2ボディ領域106上にメモリトランジスタMTのゲート部G_MTをMONOS構造で形成する。第1不純物拡散層104、第1ボディ領域100、第1不純物拡散層124に跨るように選択トランジスタSTのゲート部G_STをMOS型構造で形成する。両トランジスタMT,STは、バックゲートとなるボディ領域が電気的に分離される。

(もっと読む)

半導体記憶装置及びその製造方法と半導体記憶装置の動作方法

【課題】書込み速度の向上と、かつ読出しディスターブの抑制を両立させることが可能な半導体記憶装置を提供する。

【解決手段】半導体層上に電荷蓄積膜とゲート電極105を形成し、ゲート電極105の下部に形成されたチャネル領域の両側の半導体層に2つの第1導電型の拡散領域A及びBを形成する。チャネル領域は、一方の拡散領域Aが接する側のチャネル幅Waよりも他方の拡散領域Bが接する側のチャネル幅Wbの方が大きく形成される。記憶動作時には一方の拡散領域Aへ他方の拡散領域Bよりも高い電圧を印加し、読出し時には他方の拡散領域Bへ一方の拡散領域Aよりも高い電圧を印加する。

(もっと読む)

不揮発性ワンタイムプログラマブル及びマルチタイムプログラマブルメモリに組み込まれた集積回路

プログラム可能な不揮発性デバイスが、ソース/ドレイン領域の一部分に重なるFETゲートとして機能する浮遊ゲートを使用する。これにより、デバイス用のプログラム供給電圧が容量結合によって浮遊ゲートに付与され、デバイスの状態を変更する。本発明は、データ暗号化、リファレンス調整、製造ID、セキュリティID及び他の多くのアプリケーションなどの各環境において使用できる。  (もっと読む)

(もっと読む)

半導体素子及びこの半導体素子を用いた装置

【課題】高速な書込み及び消去動作を比較的低電圧で行い、かつ書換え劣化を抑えることで、メモリウインドウが大きく信頼性の高いメモリ素子を、低コストで提供する。

【解決手段】メモリ素子は、絶縁基板上に設けられた半導体層と、P型の導電型を有する第1の拡散層領域及び第2の拡散層領域と、第1の拡散層領域と第2の拡散層領域との間のチャネル領域を覆い、チャネル領域より電荷を注入され得る電荷蓄積膜と、電荷蓄積膜をはさんでチャネル領域とは反対側に位置するゲート電極とを有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクト抵抗の増加やリーク電流の発生のないビット線コンタクト構造を有する不揮発性半導体記憶装置を提供することにある。

【解決手段】基板100表面にビット線109、基板100上のビット線109間に電荷捕獲機能を有するゲート絶縁膜104、ゲート絶縁膜104上にビット線109に直交するワード線114、ワード線114間にワード線間埋め込み絶縁膜115が形成されている。ビット線コンタクト形成領域において、ワード線間埋め込み絶縁膜115に開口部が形成され、この開口部側面に側壁膜117が形成されており、ワード線114間に形成されたビット線コンタクト121は、開口部側面に形成された側壁膜117に対して自己整合的に形成されてビット線109と接続している。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】寄生容量を低減化,カップリング容量比を向上し、書き込み/消去電圧を低圧化できる。

【解決手段】pウェル領域2と、n+領域5と6間のウェル領域に跨ってゲート絶縁膜12を介して形成された選択ゲート電極(SG)と、n+領域6と接するドレイン電極Dとからなる選択トランジスタと、n+領域1と、n+領域5と電気的に接続し、n+領域1と離間するn+領域4と、n+領域1の上のトンネル絶縁膜8と、n+領域1からn+領域4の上面に跨って形成されたゲート絶縁膜12と、ゲート絶縁膜よりも厚い選択絶縁膜10と、トンネル絶縁膜,ゲート絶縁膜,および選択絶縁膜上のフローティングゲート電極(FG)と、選択絶縁膜上に形成され、FGと側方で対向して形成されたコントロールゲート電極(CG)とからなるメモリトランジスタと、選択絶縁膜を挟んでFGと対向するフローティングのn+領域1が形成される不揮発性半導体記憶装置および製造方法。

(もっと読む)

FLOTOX型EEPROM

【課題】FLOTOX型EEPROMにおいて、ドレイン領域の接合耐圧を低下させることなく、十分に高い書き込み電圧を印加できる構成で、かつ、セル面積が縮小されたものが望まれていた。

【解決手段】トンネルウインドウ12を有し、トンネルウインドウ12を介して電子の注入、引き抜きを行える整列配置された複数のフローティングゲート11と、複数のフローティングゲート11に個別に対応付けて設けられた複数のセレクトゲート13と、複数のフローティングゲート11に共有に設けられたコントロールゲート16と、複数のフローティングゲート11に共有に設けられたソース17と、複数のフローティングゲート11に共有に設けられたドレイン18とを含む構成とする。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】制御ゲート電極140は、半導体基板105の内部にリセスされて形成される。ゲート絶縁膜120は、半導体基板105と制御ゲート電極140との間に介在される。ストレージノード膜125は、ゲート絶縁膜120と制御ゲート電極140との間に介在される。ブロッキング絶縁膜130は、ストレージノード膜125と制御ゲート電極140との間に介在される。複数の第1不純物ドーピング領域は、制御ゲート電極140の第1側面に沿って配置され、半導体基板105に画定される。複数の第2不純物ドーピング領域は、制御ゲート電極140の第1側面の反対側の第2側面に沿って複数の第1不純物ドーピング領域と交互に配置され、半導体基板105に画定される。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法

【課題】低電圧で高効率な書き込みをすることが出来、電荷保持特性に優れた不揮発性半導体記憶装置及びその作製方法を提供することを目的とする。

【解決手段】基板上に形成された半導体層と、半導体層の上方に第1の絶縁層を介して設けられた電荷蓄積層と、電荷蓄積層の上方に第2の絶縁層を介して設けられたゲート電極とを有し、半導体層は、ゲート電極と重なる領域に設けられたチャネル形成領域と、チャネル形成領域と隣接して設けられたソース領域又はドレイン領域を形成する第1の不純物領域と、チャネル形成領域及び第1の不純物領域と隣接して設けられた第2の不純物領域とを有し、第1の不純物領域と第2の不純物領域は導電型が異なるように設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】電気的特性を向上させた半導体素子。

【解決手段】半導体装置10は、第1導電型基板20に設けられているゲート酸化層32、ゲートポリシリコン層34、ゲートシリコン窒化層36の積層体を含む略四角柱状のゲート電極30と、ゲート電極より外側の領域に設けられている第2導電型注入領域24と、ゲート電極の頂面30aを露出させており、側面を覆っている側壁マスク酸化層40、電子蓄積窒化層50及び側壁シリコン酸化層60が積層されているサイドウォール90と、ゲート電極及びサイドウォールから露出している第1導電型基板に設けられているソース/ドレイン拡散層80とを具えている。

(もっと読む)

不揮発性半導体記憶装置

【課題】SOI構造を持つNAND型フラッシュメモリにおいて、メモリ信号の一括消去を高速に実現可能な不揮発性半導体記憶装置を提供する。

【解決手段】埋め込み絶縁層2に接した第1導電型のチャネル領域411〜41nを備え、列方向に配列された複数のメモリセルトランジスタMT11〜MT1nと、メモリセルトランジスタMT11〜MT1nの配列の一端に隣接し、埋め込み絶縁層2に接した第2導電型のチャネル領域42を備える第1の選択ゲートトランジスタSTS1と、第2導電型のチャネル領域42と電気的に接続し、チャネル領域42よりも高不純物密度の第2導電型のソース線コンタクト領域46と、第1の選択ゲートトランジスタSTS1の第1導電型のソース領域43と電気的に接続し、且つソース線コンタクト領域46と電気的に接続したソース線コンタクトプラグ18とを備える。

(もっと読む)

電界効果トランジスタとその製造方法、及び半導体装置

【課題】ソフトエラーレートを向上させる電界効果トランジスタを提供すること

【解決手段】本発明による電界効果トランジスタ1は、第1の空洞51を有する基板10と、ゲート電極40と、拡散層60とを備える。ゲート電極40及び拡散層60は、基板10の表面に平行な面XYにおいて、第1の空洞51を囲むように形成される。チャネル領域70は、第1の空洞51の側面に位置し、基板10の表面に対して略垂直に形成される。

(もっと読む)

垂直なゲート電極のトランジスタを備える半導体装置及びその製造方法

【課題】垂直なゲート電極のトランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】本発明のトランジスタ構造体は、横方向で対向する第1及び第2の側面と縦方向で対向する第3及び第4の側面を有する半導体パターンと、半導体パターンの第1及び第2の側面に隣接して配置されるゲートパターンと、半導体パターンの第3及び第4の側面に直接接触しながら配置される不純物パターンと、ゲートパターンと半導体パターンとの間に介在されるゲート絶縁膜パターンと、を備える。これにより、ゲートパターンがチャネル領域の側面に配置されるので、半導体装置の集積度を増加させることと同時にトランジスタのチャネル幅を増加させうる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 高集積化を実現することができる不揮発性半導体記憶装置を提供すること。

【解決手段】 本発明の不揮発性半導体記憶装置は,半導体基板にトレンチ領域を設け,

1つのトレンチ領域の側壁の両側に,それぞれ,NAND型メモリセルユニットを三次元

的に有している。そしてこれらのNANDメモリセルユニットは,1本のビット線に接続

されている。それぞれのNAND型メモリセルユニットは,複数のメモリセルトランジス

タと選択ゲートトランジスタが直列に接続されている。これらの複数のメモリセルトラン

ジスタ及び選択ゲートトランジスタは,同一のトレンチ領域に設けられている。さらに,

本発明の不揮発性半導体記憶装置においては,メモリセルトランジスタの電荷蓄積層には

,従来のような浮遊ゲートの替わりに,酸化珪素膜,窒化珪素膜,酸化珪素膜の積層構造

,又はシリコン,金属その他の導電性物質のナノ結晶を含有する絶縁層を用いている。

(もっと読む)

1 - 20 / 20

[ Back to top ]