Fターム[5F101BD05]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | SD領域 (1,220) | S・D断面形状 (141)

Fターム[5F101BD05]に分類される特許

1 - 20 / 141

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

不揮発性半導体装置およびその製造方法

【課題】絶縁体に電荷を蓄える不揮発性メモリにおいて、データ保持特性を向上させることのできる技術を提供する。

【解決手段】メモリゲート電極MGと半導体基板1との間に介在する電荷蓄積層CSLをメモリゲート電極MGのゲート長または絶縁膜6t,6bの長さよりも短く形成して、電荷蓄積層CSLとソース領域Srmとのオーバーラップ量(Lono)を40nm未満とする。これにより、書込み状態では、書き換えを繰り返すことによって生じるソース領域Srm上の電荷蓄積層CSLに蓄積される正孔が少なくなり、電荷蓄積層CSL中に局在する電子と正孔との横方向の移動が少なくなるので、高温保持した場合のしきい値電圧の変動を小さくすることができる。また、実効チャネル長を30nm以下にすると、しきい値電圧を決定する見かけ上の正孔が少なくなり、電荷蓄積層CSL中での電子と正孔との結合が少なくなるので、室温保持した場合のしきい値電圧の変動を小さくすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 所望の深さを有し幅の狭い凹部を半導体基板に安定して形成することが可能な製造方法を提供すること。

【解決手段】 本発明は、半導体基板10の一部に酸素イオン注入を行うことで第1酸素含有領域24を形成する工程と、半導体基板10に熱処理を行い、第1酸素含有領域24に含まれる酸素を用いて第1酸素含有領域24を酸化させることで、第1酸素含有領域24を第1酸化領域26とする工程と、第1酸化領域26を除去することで半導体基板10に凹部16を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

半導体メモリの製造方法及び製造装置

【課題】自動的に処理レシピを変更することにより製造歩留を向上させることができる半導体メモリの製造方法及び製造装置を提供する。

【解決手段】計算部が、第2酸化膜厚、第1酸化膜厚、ゲート電極幅、アクティブ領域幅とを含む測定値を受け取り、半導体メモリのセル部の予測電流値を算出する工程(S3)と、プロセス処理実行部が、予測電流値が基準電流値以下であると判断されたときに第1処理レシピを選択し、予測電流値が基準電流値より大きいと判断されたときに第2処理レシピを選択し、第1及び第2処理レシピのうちの選択された処理レシピに従って浮遊ゲート電極の側壁を覆うSWを形成する工程(S4,S5,S6)とを有し、第2処理レシピに従って形成されたSWの第1方向の膜厚である第2のSW膜厚が、第1処理レシピに従って形成されたSDの第1方向の膜厚である第1のSW膜厚よりも大きい。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】ドレイン領域の一部に半球状の窪みを設けトンネル領域を形成し、フローティングゲート電極はトンネル領域の半球状の窪みに沿って入り込む形状となるように形成する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】対向する二つの記憶素子のコントロールゲートのゲート長に起因する記憶素子の特性のばらつきを抑制する。

【解決手段】上記の課題を解決するために、不揮発性半導体記憶装置(1)を以下のように構成する。第1不揮発性メモリセル(1a)は、第1チャネル領域(11a)と、第1フローティングゲート(5a)と、第1コントロールゲート(6a)とを含むものとする。また、第2不揮発性メモリセル(1b)は、第2チャネル領域(11b)と、第2フローティングゲート(5b)と、第2コントロールゲート(6b)とを含むものとする。ここにおいて、第1チャネル領域(11a)は、第1フローティングゲート側チャネル領域(13a)と、第1コントロールゲート側チャネル領域(12a)とを備え、第1コントロールゲート側チャネル領域(12a)は不純物濃度が濃い高濃度ポケット領域(10)を備える。

(もっと読む)

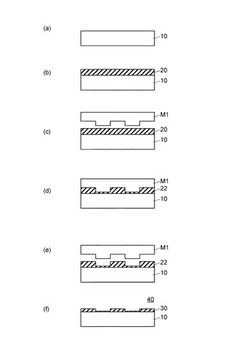

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリは、半導体基板1上に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1上に電荷蓄積部を有する絶縁膜5を介して形成されたメモリゲート電極MGとを有しており、メモリゲート電極MGは、制御ゲート電極CGの側面22上に絶縁膜5を介してサイドウォールスペーサ状に形成されている。制御ゲート電極CGは、メモリゲート電極MGに絶縁膜5を介して隣接する側とは反対側の側面21の下部21aが突出し、また、メモリゲート電極MGに絶縁膜5を介して隣接する側の側面22の下部22aが後退している。メモリゲート電極MGは、制御ゲート電極CGに絶縁膜5を介して隣接する側の側面23の下部23aが突出している。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】第2導電型のトンネル領域のフローティングゲート電極のエッジ部の下部に、第1導電型の領域からなるフローティングゲート電極エッジの電界集中防止用領域を形成する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域の表面には、薄い不純物濃度の第1導電型の領域を形成した。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択トランジスタのカットオフ特性を維持しつつ、オフセット特性の悪化を抑制する。

【解決手段】半導体基板の表層部を活性領域に分離する素子分離絶縁膜と、前記半導体基板の活性領域上のゲート絶縁膜上に形成され第1の導電層、電極間絶縁膜および第2の導電層を有するメモリゲート電極および前記メモリゲート電極の両脇に位置する前記活性領域に形成された第1のソース/ドレイン領域を備えたメモリセルトランジスタと、前記メモリセルトランジスタに隣接して配置され、前記第1のゲート絶縁膜上に導電層を積層した選択ゲート電極および前記選択ゲート電極の両脇に位置する前記活性領域に形成された第2のソース/ドレイン領域を備えた選択ゲートトランジスタとを有し、前記活性領域に形成される少なくとも前記第2のソース/ドレイン領域は、前記活性領域の表層部が掘り下げられた凹部に設けられていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】電荷蓄積層をもち、電荷のトラップを利用する記憶素子の保持特性を向上させる技術を提供する。

【解決手段】電荷蓄積層(24)の上のメモリゲート(21)と、第1サイドゲート(22)と、第2サイドゲート(23)と、第1サイドゲート(22)側の第1不純物注入領域(31)と、第2サイドゲート(23)側の第2不純物注入領域(32)と、チャネル領域(33、34、35)とを具備する不揮発性半導体記憶装置を構成する。チャネル領域(33、34、35)は、電荷蓄積層(24)の下の第1領域(33)と、第1領域(33)と第1不純物注入領域(31)との間のセレクト側領域(34)と、第1領域(33)と第2不純物注入領域(32)との間のアシスト側領域(35)とを含むことが好ましい。そして、ゲート長方向におけるセレクト側領域(34)の長さ(L1)は、アシスト側領域(35)の長さ(L2)よりも長いものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】高品質な半導体装置およびその製造方法を提供する

【解決手段】半導体基板1内に形成された一対の第1の不純物拡散領域1bと、一対の第1の不純物拡散領域1bに挟まれ、一対の第1の不純物拡散領域1bに隣接して形成され、第1の不純物拡散領域1bと同じ導電型且つ第1の不純物拡散領域1bよりも不純物濃度の低い一対の第2の不純物拡散領域1aと、一対の第2の不純物拡散領域1aに挟まれたチャネル領域と、第1の不純物拡散領域1b上に形成された周辺絶縁膜4と、第2の不純物拡散領域1a上およびチャネル領域上に形成され、周辺絶縁膜4よりも膜厚の厚いゲート絶縁膜3と、ゲート絶縁膜3上且つチャネル領域の略直上に形成されたゲート電極5とを備える。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】N+型ソース層とフローティングゲートとのカップリング比を高くしてプログラム特性を改善すると共にメモリーセルの面積の縮小化を図る。

【解決手段】N+型ソース層4の両側にトレンチ3を形成する。トレンチ3の側壁は2つの素子分離層STI2の端面と平行なトレンチ側壁2a、トレンチ側壁2bと、STI2に垂直な面からなるトレンチ側壁3a、及びトレンチ側壁3aと平行でないトレンチ側壁3bから構成される。かかる構成のトレンチ3の上部からトレンチ側壁3aに平行で、且つP型ウエル層1に垂直又は角度をもった砒素イオン等のイオン注入を行い、トレンチ3底面からトレンチ側壁3bに延在するフローティングゲートFG6と広い面積で対峙するN+型ソース層4を形成する。

(もっと読む)

1 - 20 / 141

[ Back to top ]