Fターム[5F101BE02]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 読出回路、読出方法 (1,330)

Fターム[5F101BE02]の下位に属するFターム

ダイナミック読出し

Fターム[5F101BE02]に分類される特許

201 - 220 / 1,330

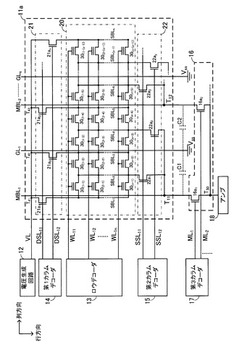

半導体メモリ

【課題】ビット線間の寄生容量による影響を低減することにより、高精度のデータの読出しを可能にする半導体メモリを提供する。

【解決手段】1つの主ビット線に互いに異なるタイミングでオン駆動するセレクタ素子及び当該セレクタ素子のそれぞれに接続された副ビット線を介して当該副ビット線のそれぞれにメモリセルが接続され、当該主ビット線に並置されるとともに固定電位に接続された固定電位線が設けられていること。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体装置の駆動方法

【課題】信頼性の高い書き込み動作を高速に行うことのできる半導体装置の駆動方法を提供する。

【解決手段】多値書き込みを行う半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに、書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。書き込みを行いながらビット線の電位を検知することによって、書き込みベリファイ動作を行うことなく、書き込みデータに対応した電位がフローティングゲートに正常に与えられたかを確認することができる。

(もっと読む)

半導体記憶装置

【課題】 本発明の実施形態によれば、プロセッサの処理速度を低下させることなく、フラッシュメモリの信頼性を維持する半導体記憶装置を提供することができる。

【解決手段】 第1の電極に第1の電位を与え、全てのバックゲート電極に第1の電位よりも低い第2の電位を与え、第1乃至第n−1のフロントゲート電極に第1の電位よりも高い第3の電位を与え、第n以上のフロントゲート電極に第2の電位と第3の電位との間の第4の電位を与えることで半導体層に情報を書き込むことを特徴とする

(もっと読む)

不揮発性半導体記憶装置

【課題】消去電圧を低減させることができる半導体記憶装置を提供することを課題とする。

【解決手段】チャネル形成領域を有する半導体膜と、半導体膜のチャネル形成領域上に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を設ける。浮遊ゲート電極材料には、半導体基板よりも仕事関数があまり大きくならない窒化チタンとすることにより、消去電圧低減を図ったものである。なお、上記窒化チタンのチタン組成比は、低消費電力化及び誤書き換え耐性の観点から56atomic%以上75atomic%以下がよい。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、選択メモリブロック内の選択セルユニットに対して第1メモリトランジスタに蓄積された電荷を放出する消去動作を実行する一方、選択メモリブロック内の非選択セルユニットに対して消去動作を禁止するように構成されている。制御回路は、消去動作時、選択セルユニットに含まれる第1メモリトランジスタのボディの電圧を第1電圧まで上げ、非選択セルユニットに含まれる第1メモリトランジスタのボディの電圧を第1電圧よりも低い第2電圧に設定すると共に、選択セルユニット及び非選択セルユニットに含まれる第1メモリトランジスタのゲートに第2電圧以下の第3電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化が進展しても読み出し動作時の電流を維持する。

【解決手段】複数のメモリサブブロックの各々は、第1ノードと第2ノードとの間に並列接続された複数のメモリトランジスタを含む。メモリサブブロックは、第1導電層と、第2導電層と、半導体層と、第3導電層とを備える。第1導電層は、層間絶縁膜を貫通して半導体基板に対し垂直な第1方向に延びるように形成され第1ノードとして機能する。第2導電層は、層間絶縁膜を貫通して半導体基板に対し第1方向に延びるように形成され第2ノードとして機能する。半導体層は、第1導電層と第2導電層とを接続するように半導体基板と平行な第2方向に延びるように形成されメモリトランジスタのチャネル層として機能する。第3導電層は、半導体層上にゲート絶縁膜を介して形成される。ゲート絶縁膜は、電荷蓄積膜を一部に含み第3導電層を囲う閉ループ状に形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルに与えられる影響を緩和し、正確にデータを書き込むことのできる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセルアレイと制御部とを備える。制御部は、選択メモリセルに書き込みパルス電圧を印加するとともに、非選択メモリセルに中間電圧を印加する書き込み動作、書き込みベリファイ動作、及び書き込みパルス電圧を上昇させるステップアップ動作を繰り返す制御を司る。制御部は、第1期間では、中間電圧を一定の値に保ち、第2期間では、中間電圧を所定のステップアップ値だけ上昇させるようにステップアップ動作を制御する。制御部は、第1期間では、書き込みパルス電圧を第1のステップアップ値で上昇させる動作を含み、第2期間では、書き込みパルス電圧を第1のステップアップ値より小さい第2のステップアップ値で上昇させる動作を含むようにステップアップ動作を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

不揮発性半導体記憶装置およびその制御方法

【課題】高速で高信頼動作できるようにした不揮発性半導体記憶装置およびその制御方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセル、および、前記第1のメモリセルに対し第1方向に隣接して配置された第2のメモリセルを備えたセル群と、書込回路とを備え、第1および第2のメモリセルの一方をデータ記憶保持に、他方を一方の閾値調整に用い、書込回路が、セル群の前記第1のメモリセルにデータを書込むときには、セル群の第2のメモリセルに電圧を印加し、セル群の第1のメモリセルの閾値電圧を所望の第1閾値電圧より高く調整する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置の高信頼性及び高集積化を図る。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1乃至第iのメモリストリング(iは、2以上の自然数)を有し、第2の方向に延び、第3の方向に隣接する第1及び第2のフィン型積層構造9−1,9−2と、第1のフィン型積層構造9−1の第2の方向の一端に接続され、第3の方向の幅が第1のフィン型積層構造9−1のそれよりも広い第1の部分7aと、第2のフィン型積層構造9−2の第2の方向の一端に接続され、第3の方向の幅が第2のフィン型積層構造9−2のそれよりも広い第2の部分7bとを備える。第1乃至第iのメモリストリングは、それぞれ、複数のメモリセルとアシストゲートトランジスタとを備える。アシストゲートトランジスタのアシストゲート電極AG1,AG2は、電気的に独立である。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置を構成する回路を高集積度化する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、半導体基板と複数のメモリセルトランジスタを有する。前記複数のメモリセルトランジスタは、前記半導体基板に設けられた深溝にトレンチゲートが埋設され、直列接続される。メモリセルの書き込み動作及び読み出し動作のとき、トレンチゲートの周囲及び間の前記半導体基板の領域に、前記半導体基板とは逆導電型の反転層が形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルから確実にデータを読み出すことのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、複数の不揮発性メモリセルに接続されるワード線と不揮発性メモリセルを選択してデータ読み出し動作を制御する制御回路とを備える。制御回路はデータ読み出し動作実行の際、選択メモリセルに接続された選択ワード線に、隣接する閾値電圧分布の中間電圧に第1の調整電圧を加えた電圧を印加し、選択ワード線に隣接する第1の非選択ワード線に、不揮発性メモリセルを導通させ得る読み出しパス電圧から第2の調整電圧を引いた電圧を印加し、第1の非選択ワード線に隣接する第2の非選択ワード線に、読み出しパス電圧に第2の調整電圧を加えた電圧を印加し、第1の非選択ワード線及び第2の非選択ワード線を除く非選択のワード線に、読み出しパス電圧を印加する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた窒化シリコン膜6bとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた空洞CAVとを有し、窒化シリコン膜6bを有していない。

(もっと読む)

半導体記憶装置

【課題】消去回数の増加を抑制し、書き込み速度の向上及びメモリセルの劣化を防止することが可能な半導体記憶装置を提供すること。

【解決手段】読み出しレベルに応じてデータを保持可能なセルMCが形成されたセルアレイ1と、前記セルMCに書き込まれた回数N(N:0以上の整数)をカウントし、その回数に応じて書込電圧Vpgm及び読出電圧Vcgrを前記セルに転送する制御部9と、前記書込電圧を用いてデータを書み込み、前記読出電圧を発生し、データを読み出す電圧発生回路とを具備し、書込要求があると、前記読出電圧を発生させ、前記データを読み出し、読み出された閾値電圧より高い閾値電圧に遷移させる前記書き込み電圧を前記電圧発生回路に発生させ、前記セルへの前記回数N回目(≧2)の書き込み要求が規定値に達していると、前記制御部は前記セルが保持する前記データを消去させる。

(もっと読む)

201 - 220 / 1,330

[ Back to top ]