Fターム[5F101BE02]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 読出回路、読出方法 (1,330)

Fターム[5F101BE02]の下位に属するFターム

ダイナミック読出し

Fターム[5F101BE02]に分類される特許

121 - 140 / 1,330

半導体記憶装置

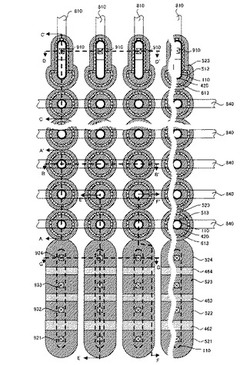

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、単位面積あたりの記憶容量を増加させる。

(もっと読む)

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、を有し、駆動回路は、

データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

ゲインセル型半導体メモリ装置およびその駆動方法

【課題】ゲインセルとして知られている2つのトランジスタと1つのキャパシタよりなるメモリセルを改良する。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極を書き込みトランジスタのドレインに接続する。また、書き込みトランジスタのソースは、ソース線に接続される。この結果、例えば、キャパシタとしてスタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線の電位と書き込みビット線の電位を設定することで、特定の書き込みトランジスタのみをオンとし、1つのメモリセルだけを書き換えることもできる。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、複数のメモリストリング、ドレイン側選択トランジスタ、ソース側選択トランジスタ、複数のワード線、複数のビット線、ソース線、ドレイン側選択ゲート線、ソース側選択ゲート線、及び制御回路を有する。制御回路は、選択したビット線に第1電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を実行する一方、非選択としたビット線に第2電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を禁止する。

(もっと読む)

半導体装置およびその駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のチャネル形成領域と、第1のゲート電極と、第1のソース領域およびドレイン領域と、を有する第1のトランジスタと、少なくとも第1のソース領域またはドレイン領域の一部と重畳するように設けられた、酸化物半導体材料からなる第2のチャネル形成領域と、第2のソース電極と、第1のゲート電極に電気的に接続される第2のドレイン電極と、第2のゲート電極と、を有する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間の絶縁層と、を含むメモリセルを有し、第2のトランジスタをオフ状態とすべき期間において、少なくとも第1のソース領域またはドレイン領域に正の電位が与えられるときに第2のゲート電極に負の電位が与えられる半導体装置。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積を削減することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に積層され、垂直方向に直列接続された複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられ、所望の電圧をメモリセルアレイに供給する電源回路とを備える。電源回路は、電圧を生成するポンプ回路と、ポンプ回路の出力端子に接続され、出力端子の電圧値が所定の値を下回った場合にポンプ回路へ制御信号を出力するリミッタ回路と、出力端子に一端が接続され、出力端子の電圧を調整するように構成されたキャパシタと、キャパシタの他端に接続され、制御信号に基づき所定の電流値の定電流を用いてキャパシタを充電するブースト回路と、ブースト回路の充電動作を停止させるスイッチとを備える。キャパシタは、メモリセルアレイの直下に設けられる。

(もっと読む)

半導体記憶装置

【課題】高性能な乱数を生成することができ、予測困難性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルMCが配置されるメモリセルアレイ11と、乱数(Random number)を発生させる乱数発生回路16と、メモリセルアレイ11および乱数発生回路16を制御するコントローラ19とを少なくとも具備する。乱数発生回路16は、生成した制御パラメータ(Read voltage parameter)によりメモリセルMCを読み出した結果にもとづく乱数パラメータ(PRESET)を生成する乱数制御回路162と、乱数パラメータ(PRESET)をシード値として用いて乱数(Random number)を発生させる擬似乱数生成回路161とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化による信頼性低下が小さい半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板上に浮遊ゲートと制御ゲートを有する複数の電気的書き換え可能な不揮発性メモリセルを備えたNANDセルユニットを有する。NANDセルユニットは、不揮発性メモリセルの互いのソース領域及びドレイン領域を共有し、不揮発性メモリセルが直列接続されている。不揮発性メモリセルのソース領域及びドレイン領域は、シリサイドを用いて形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

半導体不揮発性記憶装置およびその製造方法

【課題】高い信頼性で書き込み・消去・読み出しが可能な低コストの半導体不揮発性記憶装置およびその製造方法を提供する。

【解決手段】実施形態の半導体不揮発性記憶装置は、基体Sと、第1の電極2と、機能膜10と、第2の電極50と、を持つ。前記第1の電極2は、前記基体S上に設けられる。前記機能膜10は、前記第1の電極2上に成膜されて記憶媒体をなす。前記第2の電極50は、上面に凸の曲面を有するように、前記機能膜10上または前記機能膜10内に設けられる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

不揮発性半導体記憶装置

【課題】 BiCSメモリのような積層型メモリの書き込み動作を高速化することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 積層型のメモリセル構造を有する不揮発性半導体記憶装置であって、半導体基板上に、複数のメモリセルを積層してなるストリングを複数個配置したメモリセルアレイ11と、メモリセルアレイ11の任意のストリングをサンプルストリングとして選択し、該選択したサンプルストリングに対してデータの書き込みを行う回路12,14,16,30と、サンプルストリングの各メモリセルに対する書き込み回数をレイヤー毎に保持する書き込み回数記憶部31と、記憶部31に記憶されたレイヤー毎の書き込みパルス数を同一レイヤーの他のストリングのメモリセルの書き込み電圧の初期値に反映させる回路33とを備えている。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

熱アシスト誘電体電荷トラップメモリ

【課題】

誘電体電荷トラップメモリの動作速度及び/又は耐久性を向上させる技術を提供する。

【解決手段】

メモリデバイスは、ワードライン及びビットラインを含む誘電体電荷トラップ構造メモリセルのアレイを含む。該アレイに、読み出し、プログラム及び消去の動作を制御するように構成された制御回路が結合される。コントローラは、該アレイのメモリセル内の誘電体電荷トラップ構造を熱アニールする支援回路を備えるように構成される。熱アニールのための熱を誘起するために、ワードラインドライバ及び前記ワードライン終端回路を用いて、ワードラインに電流を誘起することができる。熱アニールは、サイクルダメージからの回復のために、通常動作とインターリーブされて適用されることが可能である。また、熱アニールは、消去のようなミッション機能中に適用されることもでき、それにより該機能の性能を向上させ得る。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

121 - 140 / 1,330

[ Back to top ]