Fターム[5F101BE02]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 読出回路、読出方法 (1,330)

Fターム[5F101BE02]の下位に属するFターム

ダイナミック読出し

Fターム[5F101BE02]に分類される特許

161 - 180 / 1,330

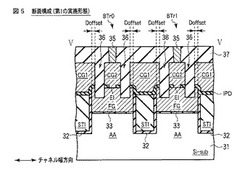

半導体装置およびその製造方法

【課題】リーク電流の発生を防止でき、微細化に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、素子分離膜により分離される素子領域を有する半導体基板31と、前記素子領域上にゲート絶縁膜を介して設けられる第1導電層FGと、前記第1導電層および前記素子分離膜上に設けられ、前記第1導電層上に開口を有するゲート間絶縁膜IPDと、前記ゲート間絶縁膜を介して、前記素子領域上および前記素子分離膜上にわたって配置される第2導電層CG1と、前記第1導電層上に設けられ、周囲の溝により前記第2導電層と電気的に分離され、前記ゲート間絶縁膜の前記開口を介して前記第1導電層と接続される第3導電層CG2と、前記第1導電層を挟むように、前記素子領域中に隔離して設けられるソースまたはドレイン拡散層38とを具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリ容量を容易に調整することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、Y方向に配列された4つのP型ウェルPWのうちの端の1つのP型ウェルPWに複数のメモリブロックMB0〜MB3を設け、残りの3つのP型ウェルPWにそれぞれ3つのメモリブロックMB10〜MB12を設ける。また、それぞれメモリブロックMB0〜MB3,MB10〜MB12のX方向に隣接してロウデコーダRD0〜RD3,RD10〜RD12を設ける。メモリブロックMB10〜MB12を削除してメモリ容量を減らす場合でも、周辺回路の再レイアウトが不要となる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な半導体装置を提供する。

【解決手段】P型の半導体基板10と、半導体基板10内に形成されるNウェル11、半導体基板10内かつNウェル11上に形成されるPウェル12、及びPウェル12上に形成されるメモリセルトランジスタMTを含むCell領域と、半導体基板10内に形成されるNウェル14、及びNウェル上14に形成されるトランジスタHVP−Trを含むHVP−Tr領域と、半導体基板10上に形成されるトランジスタHVN―Trを含むHVN―Tr領域と、半導体基板10内に形成されるNウェル22、半導体基板10内かつNウェル22上に形成されるPウェル23、およびPウェル23上に形成されるトランジスタLVNE−Trを含むLVNE−Tr領域と、を具備し、Nウェル11及びNウェル22の底面の位置はNウェル14の底面の位置よりも低く、Nウェル14の底面の位置はPウェル12及びPウェル23の底面の位置よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】実施形態によれば、十分な消去速度が得られる半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、第1の積層体と、メモリ膜と、第1のチャネルボディと、第2の積層体と、ゲート絶縁膜と、第2のチャネルボディとを備えている。前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成されている。前記段差部を被覆する部分の前記第2のチャネルボディの膜厚は、前記第2の絶縁層間に設けられた部分の膜厚よりも厚い。

(もっと読む)

チャージトラップインシュレータメモリ装置

【課題】ナノスケールチャージトラップインシュレータメモリ装置において維持特性を向上させ、多数のセル絶縁層を用いて多数のチャージトラップインシュレータセルアレイが垂直方向に積層してセル集積容量を高める技術を開示する。

【解決手段】

多数の上部ワードライン及び下部ワードラインと、多数のビットライン及びセンシングラインと、上部/下部ワードラインとビットラインの交差領域に配置される多数のメモリセルアレイと、チャージトラップインシュレータからビットラインに格納データが出力される多数のメモリセルと、メモリセルをビットライン及びセンシングラインと各々選択的に連結する第1のスイッチング素子及び第2のスイッチング素子とを含み、チャージトラップインシュレータの極性に従い抵抗変化するP型フロートチャンネルと、その両側に形成されたP型ドレイン領域及びP型ソース領域とを含む。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

不揮発性半導体記憶装置の動作方法

【課題】制御部を増加せずにブロックサイズを小さくできる不揮発性半導体記憶装置の動作方法を提供する。

【解決手段】メモリストリングを有するメモリ部と、メモリ部を制御する制御部と、を備える不揮発性半導体記憶装置110の動作方法である。メモリストリングは、直列に接続された複数のトランジスタを含み、複数のトランジスタのうちの一部である第1グループGR1と、第1グループの隣りに接続された第1調整用トランジスタTr−AJと、調整用トランジスタの第1グループとは反対側に接続されたトランジスタを含む第2グループGR2と、を有する。制御部は、第1グループのトランジスタの閾値の書き換えを行ったのち、第1調整用トランジスタに、閾値の書き換えによって生じた第2グループのトランジスタの閾値の相対的な変動分を調整する第1調整用閾値を設定する制御を行う。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

記憶装置、半導体装置、検出方法

【課題】データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を、短時間にて正確に行うことができる記憶装置の提供。

【解決手段】各メモリセルに、第1容量素子と、第2容量素子と、上記第1容量素子及び第2容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタと、を少なくとも有する。また、第1容量素子の容量値が、第2容量素子の容量値の1000倍以上、好ましくは10000倍以上となるようにする。そして、通常動作の時に、第1容量素子及び第2容量素子を用いて電荷の保持を行う。また、データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を行う時に、第2容量素子を用いて電荷の保持を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み時間の短縮及び読み出し電圧の上昇の抑制を図る不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリ部と、制御部と、を備える。メモリ部は、積層構造体と、半導体ピラーと、記憶層と、内側絶縁膜と、外側絶縁膜と、メモリセルトランジスタと、を有する。制御部は、メモリセルトランジスタの各閾値を正または負の一方に設定する制御、及び各閾値のうち0ボルトから最も離れた第n閾値の分布の幅よりも、第n閾値と同じ符号の第m(mはnよりも小さい1以上の整数)閾値の分布の幅を狭く設定する制御を行う。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

161 - 180 / 1,330

[ Back to top ]