Fターム[5F101BE02]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 読出回路、読出方法 (1,330)

Fターム[5F101BE02]の下位に属するFターム

ダイナミック読出し

Fターム[5F101BE02]に分類される特許

141 - 160 / 1,330

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

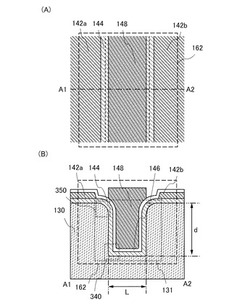

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置を工程数の増大を抑制しながら製造可能な不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板101上にスペーサ膜104とチャネル半導体膜103とを交互に複数層積層させた積層構造を形成し、積層構造に第1の方向に延在するトレンチを形成する。ついで、トレンチからチャネル半導体膜103を第2の方向にリセスして空隙を形成し、空隙内のチャネル半導体膜103上にトンネル誘電体膜108を形成し、フローティングゲート電極膜109を埋め込む。その後、第1の方向に隣接するメモリセル間でフローティングゲート電極膜109が分離され、チャネル半導体膜103が分離されないように、積層構造を第1の方向に所定の間隔で分割する。また、第2の方向に隣接するメモリセル間でチャネル半導体膜103が分離されるように、積層構造を第2の方向に所定の間隔で分割する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】トランジスタの作製工程において、酸化物半導体層、ソース電極層、ドレイン電極層、ゲート絶縁膜、ゲート電極層、酸化アルミニウム膜を順に作成した後、酸化物半導体層および酸化アルミニウム膜に対して熱処理を行うことで、水素原子を含む不純物が除去され、かつ、化学量論比を超える酸素を含む領域を有する酸化物半導体層を形成する。また、酸化アルミニウム膜を形成することにより、該トランジスタを有する半導体装置や電子機器の作製工程での熱処理でも大気から水や水素が酸化物半導体層に侵入し、拡散することを防止することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または

、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶

縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と

、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁

層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)

粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層

表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

電界効果トランジスタおよびそれを用いたメモリおよび半導体回路

【課題】微細化した半導体集積回路において用いられる、オフ電流の小さな電界効果トランジスタ(FET)を提供する。

【解決手段】絶縁表面に略垂直に形成された厚さが1nm以上30nm以下の薄片状の酸化物半導体と、前記酸化物半導体を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜を覆って形成されたストライプ状の幅10nm以上100nm以下のゲートを有する電界効果トランジスタ。この構成では、薄片状の酸化物半導体の三方の面をゲートが覆うこととなるため、ソース、ドレインから注入される電子を効率的に排除し、ソースとドレインの間をほぼ空乏化領域とでき、オフ電流を低減できる。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置

【課題】従来は、外部機器側で情報の書き込みが正常に成されたか否かを判断していた。また、半導体装置ないに大掛かりな回路を構成しなければ、正しく書き込みを判断できなかった。

【解決手段】外部機器から入力される書込パルスのうち、そのパルス長で、搭載する不揮発性記憶手段に情報が正しく書き込まれたか否かの判定を行なう判断手段を設けた。判断手段は、書込パルスのパルス長が所定の範囲にあるか否かや、書込パルスの到来と同時に時間を計測する計時手段などを用いることで、パルス長が正しいか否かを判定する。これにより、簡便な構成で、正しい情報の書き込みを判断できる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高駆動力と高信頼性を実現する選択ゲートスイッチトランジスタを備える不揮発性半導体記憶装置を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置は、選択ゲートスイッチトランジスタを備える不揮発性半導体記憶装置である。そして、この選択ゲートスイッチトランジスタが、半導体基板上に形成されるゲート絶縁膜と、ゲート絶縁膜上に形成されるゲート電極と、半導体基板中に、ゲート電極を挟むように設けられる第1のソース・ドレイン領域と第2のソース・ドレイン領域とを備えている。そして、第1のソース・ドレイン領域が、第1のn型不純物層と、第1のn型不純物層よりも不純物濃度が高く深さの浅い第2のn型不純物層を備えている。さらに、第2のソース・ドレイン領域が、第1のn型不純物層よりも不純物濃度が低く深さの浅い第3のn型不純物層と、第3のn型不純物層よりも不純物濃度が高く深さの深い第4のn型不純物層を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリブロックを縮小化可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、半導体基板、メモリストリング、複数の第1導電層、第2導電層、及び第3導電層を有する。メモリストリングは、半導体基板に対して垂直方向に直列接続された複数のメモリセル、ダミートランジスタ、及びバックゲートトランジスタを有する。複数の第1導電層は、メモリセルのゲートと電気的に接続されている。第2導電層は、ダミートランジスタのゲートと電気的に接続されている。第3導電層は、バックゲートトランジスタのゲートと電気的に接続されている。第2導電層は、第3導電層と短絡している。

(もっと読む)

不揮発性メモリ

【課題】大容量NAND Flash Memory Chipに、プロセスコストが殆ど無く、SRAMに比べセル面積が小さいDRAMメモリを混載し、CHIPコストをおさえつつ、NANDのシステム性能を向上させることを可能とする複合メモリを提供すること。

【解決手段】第1絶縁膜と、第1Floating Gateと、第2絶縁膜と、第1ゲート電極からなる第1メモリセルと、第3絶縁膜と、第2Floating Gateと、第4絶縁膜と、第2ゲート電極と、第2Floating Gateと第4ゲート電極を接続する第1コンタクトからなる第1選択トランジスタと、第1メモリセルが直列に複数接続され、ビット線に接続され、第1選択トランジスタを介してソース線に接続されたもので第1セルブロックを構成し、これを複数配列する不揮発性メモリにおいて、面積S1が、面積S2に比べて大きい。

(もっと読む)

半導体装置及びその作製方法

【課題】しきい値電圧の制御が困難な酸化物半導体を活性層に用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】一対の第1の領域、一対の第2の領域及び第3の領域を有する酸化物半導体膜と、酸化物半導体膜と接して設けられる一対の電極と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介し、一対の電極の間に設けられたゲート電極と、を有し、一対の第1の領域は一対の電極と重畳し、第3の領域はゲート電極と重畳し、一対の第2の領域は一対の第1の領域及び第3の領域の間に形成され、一対の第2の領域及び第3の領域には窒素、リン、または砒素のいずれかの元素が含まれており、該元素の濃度は、第3の領域より一対の第2の領域のほうが高い構成とする。

(もっと読む)

141 - 160 / 1,330

[ Back to top ]