Fターム[5F101BF01]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 特性ヒステリシスしきい値 (921)

Fターム[5F101BF01]の下位に属するFターム

Fターム[5F101BF01]に分類される特許

81 - 100 / 143

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置、その製造方法、その書き込み方法、その読み出し方法、記録媒体並びに半導体記憶装置

【課題】 電荷捕獲量の調節を容易且つ確実に行い、情報ばけ等の不都合の発生を防止して所望の多値情報を記憶する。

【解決手段】 ソース領域3−ドレイン領域4間のチャネル領域Cとゲート電極6との間に、ゲート酸化膜11、シリコン窒化膜12、シリコン酸化膜13、シリコン窒化膜14、シリコン酸化膜15、シリコン窒化膜16及びシリコン酸化膜17が順次積層されてなる電荷捕獲膜5が配されて半導体記憶装置が構成される。ここで、各窒化膜12,14,16とその下層の各酸化膜11,13,15,17との間に存するトラップに電荷を蓄積することで、4値("00","01","10","11")の情報が記憶される。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルのしきい値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、第1の絶縁膜、電荷保持層、第2の絶縁膜、および、制御ゲートを含み、電荷保持層に保持された電荷量に応じた情報を記憶するメモリセルが直列に複数接続されたNANDストリングと、制御ゲートおよび半導体ウェルに印加する電圧を制御する制御回路とを備え、書き込み動作後、選択メモリセルにデータが書き込まれたか否かを検証するベリファイリード動作を行う前に、制御回路は、選択メモリセルの制御ゲートに、半導体ウェルの電位と同電位または書き込み電圧と同極性である第1の電圧を印加し、書き込み対象ではない非選択メモリセルの制御ゲートには、書き込み電圧と同極性であり第1の電圧よりも絶対値として大きい第2の電圧を印加するデトラップ動作を行う。

(もっと読む)

絶縁ゲート型半導体装置の製造方法

【課題】非ヒステリシストランジスタとヒステリシストランジスタとを混載する場合において、欠陥や不純物混入リスクの少ない良好な基板界面を保ったまま、同一材料の絶縁膜を用いて、ヒステリシストランジスタと非ヒステリシストランジスタとを同一基板上に混載することができる絶縁ゲート型半導体装置の製造方法を提供する。

【解決手段】第1及び第2のトランジスタ形成領域上に第1のトランジスタにヒステリシス特性を与える絶縁膜1を形成し、これを第1のトランジスタのゲート絶縁1膜とする工程、及び、第2のトランジスタ形成領域上の絶縁膜1を部分的にエッチング除去することにより、第2のトランジスタにヒステリシス特性を与えない絶縁膜とし、これを第2のトランジスタのゲート絶縁膜とする工程を含む。

(もっと読む)

デプレッションタイプNANDフラッシュメモリ

【課題】デプレッションタイプNANDの読み出し時のセル閾値変動を防止する。

【解決手段】本発明の例に係わるデプレッションタイプNANDフラッシュメモリは、NANDストリングを構成する複数のデプレッションタイプFETの各々が、電荷蓄積層内の電荷量に応じて閾値が変化するトランジスタであり、隣接メモリセル記憶部が、選択されたデプレッションタイプFETのソース線側に隣接するソース線側デプレッションタイプFETの閾値を記憶する。制御回路は、読み出し時に、隣接メモリセル閾値記憶部に記憶された閾値に特定電位記憶部に記憶された特定電位を足した値を、ソース線側デプレッションタイプFETのゲート電位に加える。

(もっと読む)

不揮発性半導体記憶装置

【課題】 不揮発性半導体装置のデータ書き込み後のしきい値の分布幅を狭くして、メモリセルの多値化を容易にする。

【解決手段】 第1の書き込み動作の後にしきい値検証電圧を変更して第2の書き込み動作を行う。この際、第1のしきい値検証電圧Verify(b)と第2のしきい値検証電圧Verify(a)との間に、第1の書き込み動作後のしきい値の分布幅をwとして、Verify(b)=Verify(a)−w/2の関係があるので、第2の書き込み動作後のしきい値の分布幅はw/2となる。

(もっと読む)

ブースト電圧クランプを改善するためのペアビットラインプログラミング

プログラミング技法は、プログラム外乱を回避するために阻止されたチャネルのクランプブースト電位を上昇させる選択ビットラインパターンを使用してプログラミングすることによって、不揮発性記憶素子のセットでのプログラム外乱を削減する。1つの態様では、隣接するビットラインの交互のペアを第1のセット及び第2のセットにグループ化する。二重プログラミングパルスが、選択されたワードラインに印加される。ビットラインの第1のセットは、第1のパルスの間にプログラミングされ、ビットラインの第2のセットは、第2のパルスの間にプログラミングされる。次に、全てのビットラインに検証動作が実行される。ある特定のビットラインが阻止されると、その隣接ビットラインの少なくとも1つも阻止され、その特定のビットラインのチャネルが十分にブーストされる。別の態様は、2ビットラインおきに別々にプログラミングする。修正されたレイアウトによって、ビットラインの隣接するペアは、奇数−偶数検出回路を使用して検出できる。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上させる半導体記憶装置を提供すること。

【解決手段】電荷蓄積層25と制御ゲート27とを含み、閾値に応じて2値以上のデータを保持可能な複数のメモリセルと、前記メモリセルのゲート27または電流経路の一端に電気的にそれぞれ接続され、隣接する前記メモリセル間で線幅の異なる信号線と、前記信号線に印加される電圧を前記信号線の線幅に応じて制御する制御部2とを具備する。

(もっと読む)

固体撮像素子、その動作方法、その製造方法及びデジタルカメラ

【課題】受光量に十分に対応(ばらつきの少ない線形又は非線形)したデータを不揮発性メモリセルから読み出すことができる固体撮像装置を実現すること。

【解決手段】入射光を受け信号電荷を発生させる受光素子と、一端が受光素子に接続され、他端が検出ノードに接続された第1のトランジスタと、一端が検出ノードに接続された第2のトランジスタと、検出ノードに制御ゲート又は一端が接続された電荷蓄積層を有するメモリセルトランジスタと、を具備することを特徴とする固体撮像装置。

(もっと読む)

半導体装置

【課題】周辺トランジスタの駆動特性の劣化を抑制できる半導体装置を提供すること。

【解決手段】半導体基板と、前記半導体基板の素子形成領域を取り囲むよう形成された素子分離絶縁膜と、前記素子形成領域内に配置されたトランジスタと、を備え、前記トランジスタは、前記素子形成領域内に設けられた第1および第2の拡散層と、前記第1および第2の拡散層の間に設けられたチャネル領域と、前記チャネル領域の表面に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に配置されたゲート電極と、を有し、前記素子形成領域と前記素子分離絶縁膜との境界部における前記ゲート電極のゲート長が前記素子形成領域の中央部における前記ゲート電極のゲート長よりも長い。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルの結晶性の向上を図ることが可能なNAND型フラッシュメモリを提供する。

【解決手段】シリコン基板上に形成され、2つの選択ゲートトランジスタ間に直列に複数個接続されたメモリセルを備えた、NAND型フラッシュメモリであって、上面に垂直な方向が第1の結晶面方位<001>方向であるシリコン基板と、シリコン基板上に形成され、第1の溝が第2の結晶面方位<100>または<010>方向に沿って延びかつシリコン基板の上面を露出させるように貫通して形成された、埋め込み絶縁膜と、第1の溝内および埋め込み絶縁膜上に固相エピタキシャル成長により形成されシリコン基板と同じ面方位を有する結晶状のシリコン膜と、シリコン膜上に形成されたトンネル絶縁膜上に形成されメモリセルを構成する電荷蓄積層と、を備える。

(もっと読む)

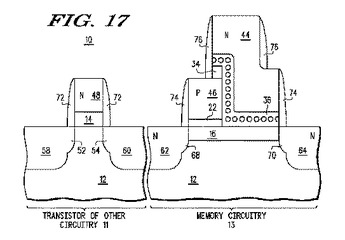

スプリット・ゲート・メモリ・デバイスの形成方法および装置

スプリット・ゲート・メモリ・デバイス(10)は、第1の仕事関数を有する選択ゲート(46)を基板(12)の第1の部分の上に有する。第2の仕事関数を有する制御ゲート(44)は、第1の部分に隣接する基板の第2の部分の上にある。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアが電子であるとき、第1の仕事関数は第2の仕事関数よりも大きい。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアがホールであるとき、第1の仕事関数は第2の仕事関数よりも小さい。基板(12)内の第1の電流電極(62)および第2の電流電極(64)は、制御ゲートおよび選択ゲートの下にあるチャネルによって分離される。制御ゲートおよび選択ゲートの異なる仕事関数は、デバイス性能を最適化するために各ゲートに対して異なる閾値電圧をもたらす。nチャネルデバイスでは、選択ゲートはp導電型であり、制御ゲートはn導電型である。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】データの消去時間を早めると共に、過剰消去が抑制された不揮発性半導体記憶装置を提供する。

【解決手段】第1制御電極に、半導体基板に対して0V以下の電圧を印加した状態で、ドレインと半導体基板との間にアバランシェ降状を起こすことによって生じるホットキャリアを浮遊ゲート電極に注入することにより消去を行う不揮発性半導体記憶装置であって、ドレインに隣接し、且つ、チャネル形成領域を除く領域に、半導体基板よりも不純物濃度が高い第1導電型の拡散領域が形成されており、該拡散領域とドレインとの界面に形成されたPN接合ダイオードのアバランシェ降状電圧の大きさが、浮遊ゲート電極直下における、消去開始時のドレインと半導体基板との間のアバランシェ降状電圧よりも大きく、消去終了時のドレインと半導体基板との間のアバランシェ降状電圧よりも小さい。

(もっと読む)

不揮発性半導体記憶装置

【課題】大容量の書き換えが必要なプログラムと小容量の頻繁な書き換えが必要なデータの記憶を1種類のメモリマットで両立させることができ、小型でソフト開発が容易な不揮発性半導体記憶装置を提供する。

【解決手段】書き換え可能な不揮発性メモリトランジスタTrが行列状に配置されてメモリマットが構成され、ワード線LG1〜LG4とビット線LD1〜LD4とで各不揮発性メモリトランジスタTrの書き込み、読み出しおよび消去が行われる不揮発性半導体記憶装置100であって、ワード線LG1〜LG4に連結される不揮発性メモリトランジスタTrが、当該不揮発性半導体記憶装置100を制御するOSの使用するワードの単位に分けられて、該ワード単位毎に半導体基板30に分割形成されたウエルからなるワード領域W1〜W4内に配置されてなる不揮発性半導体記憶装置100とする。

(もっと読む)

不揮発性半導体記憶装置の駆動方法及び不揮発性半導体記憶装置

【課題】書き込み・消去を高速化したり、或いはデータの保持特性を向上させる不揮発性半導体記憶装置の駆動方法及び不揮発性半導体記憶装置を提供する。

【解決手段】チャネルと前記チャネルの両側に設けられたソース・ドレイン領域を有する半導体層と、前記チャネルの上に設けられた第1の絶縁膜と、浮遊電極と、第2の絶縁膜と、ゲート電極と、を有する不揮発性半導体記憶装置の駆動方法であって、前記浮遊電極に第1の極性の電荷が注入された状態とするために、前記半導体層と前記ゲート電極との間に、前記第1の極性の電荷を前記第2の絶縁膜に注入する第1の電位差を与え、その後、前記第1の極性と逆極性の第2の極性の電荷を前記第2の絶縁膜に注入する第2の電位差を与え、その後、前記第1の極性の電荷を前記浮遊電極に注入する第3の電位差を与えることを特徴とする不揮発性半導体記憶装置の駆動方法。

(もっと読む)

半導体装置の荷電中心位置の評価方法、半導体装置の荷電中心位置の評価装置、及び半導体装置の荷電中心位置の評価プログラム

【課題】電荷をトラップする絶縁膜を具えた半導体装置において、前記絶縁膜中での電荷の荷電中心位置を簡易かつ正確に評価する方法、装置及びプログラムを提供する。

【解決方法】電荷をトラップする絶縁膜を具えた半導体装置の、初期C-V特性を測定し、次いで、前記半導体装置に対して電圧を印加し、前記半導体装置の前記絶縁膜中に電荷注入を行う。その後、前記半導体装置内に注入された電荷の量を測定し、さらに前記半導体装置内に前記電荷が注入された後において、前記半導体装置の終期C-V特性を測定する。そして、前記初期C-V特性、前記終期C-V特性及び測定した前記電荷の量から前記電荷の前記絶縁膜中における前記荷電中心位置を評価する。

(もっと読む)

フラッシュメモリ及びその製造方法

【課題】30nm以下の微細化に適応できるフラッシュメモリ及びその製造方法を提供する。

【解決手段】基板101に接続された上部にスペーサ絶縁膜116を有するフィン構造のビットラインから形成されたメモリセル部の最小加工寸法をFとするとき、独立に書き込み/消去可能なビットライン2本が対になって4F周期に配置されてメモリセル部が形成され、一対のフィンの上部を覆うように記憶絶縁膜が形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート絶縁膜にかかる電界を増大させるとともに、ホットエレクトロン発生数を増加させることにより、書き込み効率の向上を実現することができる。

【解決手段】 本発明の不揮発性半導体記憶装置は、第1導電型の半導体基板1内に互いに離間して形成された第2導電型のソース領域2及びドレイン領域3の間に、ソース領域2及びドレイン領域3と離間形成されるように第2導電型の半導体領域4を備える。そして、このソース領域2と半導体領域4との間、及びドレイン領域3と半導体領域4との間の半導体基板1上には、第1及び第2の浮遊ゲート6a、6bが互いに隔てられ、かつ第1のゲート絶縁膜5を介してそれぞれ形成されている。また、第1及び第2の浮遊ゲート6上、並びに第1及び第2の浮遊ゲート6a、6b間の第1のゲート絶縁膜5上に、ゲート間絶縁膜7及び第2のゲート絶縁膜8をそれぞれ介して制御ゲート9が設けられている。

(もっと読む)

不揮発性メモリ及びマイクロコンピュータ

【課題】不揮発性メモリの消去動作における基板電流の最大値を低減すること。

【解決手段】本発明の不揮発性メモリ(2)は、半導体基板(30)に形成されたソース電極(53)及びドレイン電極(54)と、ソース電極とドレイン電極間の前記半導体基板上に形成された電荷トラップ層(52)と、電荷トラップ層上に配置されたゲート電極(50)とを有する不揮発性メモリセルがアレイ状に複数配列されて成る。不揮発性メモリは、ソース電極とゲート電極とに消去に必要な電圧を印加する消去モードを有する制御回路(33)を備える。前記消去モードにおいて、ゲート電極に電圧の印加を開始してから前記ゲート電極の電圧が消去に必要な所定電圧に達するまでの期間(63)が、ソース電極に電圧の印加を開始してから前記ソース電極の電圧が前記所定電圧に達するまでの期間(64)よりも長くされる。これによって、消去動作における基板電流の最大値が抑えられる。

(もっと読む)

不揮発性半導体記憶素子および不揮発性半導体記憶装置

【課題】読み出しマージンを大きくとることができ、且つ、スタンバイ状態において記憶トランジスタに電圧ストレスが印加されない書き換え可能な不揮発性半導体記憶素子を提供する。

【解決手段】TRUE側記憶トランジスタおよびBAR側記憶トランジスタと、両記憶トランジスタのドレインと対応するビット線との間に接続された選択トランジスタと、2つの選択トランジスタのゲートに接続されたワード線と、2つのCMOSインバータをクロス接続して構成されたフリップフロップと、各記憶トランジスタのドレインとフリップフロップの対応する入出力部との間に接続された2つのゲートトランジスタとを備える。

(もっと読む)

81 - 100 / 143

[ Back to top ]