Fターム[5F101BF01]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 特性ヒステリシスしきい値 (921)

Fターム[5F101BF01]の下位に属するFターム

Fターム[5F101BF01]に分類される特許

61 - 80 / 143

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、複数のチップ間で通信する通信線を設けることなく、ピーク電流を抑制可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムによれば、電源配線81は、第1の半導体記憶装置71aと第2の半導体記憶装置71bに共通接続され、第1、第2の半導体記憶装置に電源を供給する。電圧検知回路74a,74b,74cは、第1、第2の半導体記憶装置のそれぞれに設けられ、電源配線の電源電圧を検知する。制御回路7は、第1、第2の半導体記憶装置のそれぞれに設けられ、電圧検知回路により電源電圧の低下が検知された場合、電源電圧が復帰するまで、第1、又は第2の半導体記憶装置の動作を、次の動作に遷移させない。

(もっと読む)

半導体装置の製造方法

【課題】ウィンドウ特性の向上とリテンション特性の向上とを同時に図ることのできる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上に、トンネル酸化膜、チャージトラップ膜、ブロッキング酸化膜、ゲート電極が、下側からこの順で形成された積層構造を有する半導体装置を製造する方法であって、前記ブロッキング酸化膜を形成する工程が、前記チャージトラップ膜上に結晶質膜を形成する結晶質膜形成工程と、前記結晶質膜の上層にアモルファス膜を形成するアモルファス膜形成工程とを具備し、前記結晶質膜形成工程と、前記アモルファス膜形成工程とを同一の処理容器内で連続的に行う。

(もっと読む)

半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを長期間にわたり保存する半導体メモリ装置の駆動方法を提供する。

【解決手段】書き込みトランジスタのドレインと素子トランジスタのゲート、および、容量素子の一方の電極を接続したメモリセルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に接続し、キャパシタの他方の電極を読み出しワード線に接続する。そして、容量素子に蓄えられた電荷量を、読み出しワード線の電位を変化させることにより確認し、基準以上に電荷量が減少している場合にはメモリセルのリフレッシュをおこなう。

(もっと読む)

半導体集積回路

【課題】 不揮発記憶保持用途の電界効果トランジスタと、論理演算用途の電界効果トランジスタの製造工程を別々に設けることなく前記2用途の電界効果トランジスタを同一半導体基板上に同一構造に作製できるようにする。

【解決手段】 ゲート絶縁構造体12に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタで半導体集積回路のメモリ回路とロジック回路の両方を構成し、ゲート絶縁構造体に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタのゲート-基板領域間に印加する電圧の大きさと印加タイミングを制御することによって、論理演算状態と記憶書込み状態と不揮発記憶保持状態を電気的に切り替える。

(もっと読む)

フラッシュメモリアレイのワード線構造を保護するためのワード線保護装置およびフラッシュメモリアレイのためのワード線構造

【課題】製造中に、プロセスに関連する帯電からフラッシュメモリのワード線およびメモリセルを保護するための方法と構造とを与える。

【解決手段】ドープされたポリシリコンのワード線110aの端部にドープされていないポリシリコン110bが形成され、抵抗110bが生成される。これを通じて、プロセスにより生じる電荷が、基板に結合された、ドープされたポリシリコン放電構造110cへ放電される。ワード線抵抗110b、および、放電構造110cは、単一のパターニングされたポリシリコン構造として形成される。ワード線110aおよび放電部分110cは導電性になるように選択的にドープされ、また、抵抗部分110bは、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】選択ゲート電極の側壁にメモリゲート電極を有する不揮発性記憶装置を微細化することができる技術を提供する。

【解決手段】選択ゲート電極CGをダミーパターンの側壁にサイドウォール形状で形成することで、メモリゲート電極MGが選択ゲート電極CGの両壁に形成されなくなり、フォトマスクの位置ずれを考慮する必要がなくなる。また、選択ゲート電極CGをサイドウォール状に形成することで、選択ゲート電極CGのゲート長が縮小しても、選択ゲート電極CGを構成する導電膜の膜厚により精度よく制御することを可能とする。

(もっと読む)

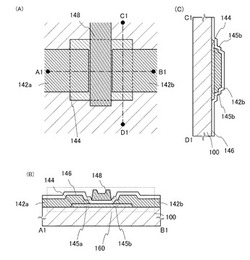

半導体不揮発性記憶素子及びその製造方法

【課題】MFMIS構造の半導体不揮発性記憶装置において、メモリセル面積を大きくすることなく、効率的に強誘電体キャパシタに分配電圧を加えることができる半導体不揮発性記憶装置及びその製造方法を提供する。

【解決手段】強誘電体不揮発性記憶素子において、チャンネル領域上に第1絶縁体層(3)、第1導電体層(4)、強誘電体層(5)、及び第2導電体層(6)が順次積層された構造を持ち、ソース領域とドレイン領域上にそれぞれ積層された第3導電体(9)と第4導電体(10)を持ち、第3導電体(9)及び第4導電体(10)が、第1導電体層(4)と第2絶縁体薄膜(11)を介して対向する構造を持つ。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】ゲート電極を形成し、ゲート電極上に第1の絶縁膜を形成し、第1の絶縁膜にハロゲンドープ処理を行って、第1の絶縁膜にハロゲン原子を供給し、第1の絶縁膜上に、ゲート電極と重畳して酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜に熱処理を行い、酸化物半導体膜上に接して、ソース電極およびドレイン電極を形成し、第2の絶縁膜を形成する半導体装置の作製方法である。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースを書き込みビット線に、読み出しトランジスタのソースとドレインとを、それぞれ、読み出しビット線及びバイアス線に接続する。さらに、キャパシタの他方の電極を読み出しワード線に接続する。配線数を減らすために、読み出しワード線を、前記書き込みトランジスタのゲートが接続していない書き込みワード線で代用する、さらに読み出しビット線を書き込みビット線で代用する。

(もっと読む)

NAND型不揮発性半導体記憶装置

【課題】セル間干渉効果によるしきい値ばらつきが抑制されたNAND型不揮発性半導体記憶装置を提供する。

【解決手段】列方向及び行方向にマトリクス状に配置される複数のメモリセルMTと、メモリセルに書込みを行う書込み回路8と、を具備し、メモリセルは、列方向において直列に接続され、行方向において共通のワード線に接続され、第1のメモリセルと、列方向において第1のメモリセルよりも寸法が小さい第2のメモリセルとを含み、書込み回路は、同一列に配置されたメモリセルのうち、所定の第1のメモリセルに書込みを行った後、別の第1のメモリセルに書込みを行い、所定の第1のメモリセルへの書込み及び別の第1のメモリセルへの書込みを行った後に、第2のメモリセルに書込みを行う。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルの信頼性を向上可能な半導体記憶装置及びその製造方法を提供する。

【解決手段】

複数のメモリセルMを備えたメモリセルアレイと、複数のメモリセルMの行方向に配列されたメモリセルMに共通に接続された複数のワード線WLと、複数のメモリセルMの列方向に配列されたメモリセルMに共通に接続された複数のビット線BLと、メモリセルMにデータの書き込みを行うとき、奇数番目のビット線BLに接続されたメモリセルMと偶数番目のビット線BLに接続されたメモリセルMとで書き込み順序を規定したヒューズデータを記憶したヒューズとを備え、奇数番目または偶数番目のビット線BLに接続されたメモリセルMの閾値分布の小さい方のメモリセルMから書き込みを行うようにヒューズデータの書き込み順序が規定されることを特徴とする半導体記憶装置。

(もっと読む)

不揮発性半導体メモリ

【課題】 従来のMONOSは、SiNに電荷を蓄積する構成であるが、電荷蓄積量が不十分であり閾値電圧変化幅を大きく取れず、またHfO2,ZrO2,TiO2中へLa系元素を導入した技術ではドーパント導入による電荷の高密度化は実現が困難である。

【解決手段】 窒化シリコン膜よりも十分に誘電率の高いZr酸化物、Hf酸化物等の窒化シリコンよりも十分に高い誘電率を有する金属酸化物を母体材料として、その中に電子の出し入れが可能なトラップレベルを発生させるために、価数が2つ上(VI価)以上の高価数物質を適量添加する構成の電荷蓄積層を有する不揮発性半導体メモリである。

(もっと読む)

半導体記憶装置

【課題】メモリセルに負の閾値電圧を設定することができ、しかも安定な動作が可能な半導体記憶装置を提供する。

【解決手段】ワード線、及びビット線に接続された複数のメモリセルがマトリックス状に配置され、前記メモリセルに負の閾値電圧を設定することが可能なメモリセルアレイと、前記ワード線、及びビット線の電位を制御する制御回路と、前記制御回路は、前記ビット線のうち第1のビット線BLoに接続されたメモリセルから負の閾値電圧の読み出し動作を行なう場合、前記第1のビット線に隣接して配置された第2のビット線BLeと、前記メモリセルアレイが形成されたウェルと、前記メモリセルアレイのソース線SRCに、正の第1の電圧Vfixを供給し、選択セルのワード線に前記第1の電圧より低い正の電圧を供給する。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

半導体記憶装置

【課題】 ベリファイ動作を高速化し、データの書き込み速度を向上する。

【解決手段】 メモリセルMCは、第1閾値電圧乃至第n閾値電圧(nは2以上の自然数)により、データを記憶する。制御回路7は、入力データに応じて前記メモリセルに前記第1乃至第n閾値電圧のいずれかを書き込む。制御回路7は、第1回目の書き込み動作により、メモリセルに第n閾値電圧、第(n−1)閾値電圧…第(n−k+1)閾値電圧のk値の閾値電圧に書き込み、第2回目の書き込み動作により、メモリセルに第(n−k)閾値電圧、第(n−k−1)閾値電圧…第(n−2k+1)閾値電圧のk値の閾値電圧に書き込み、第n/k回目の書き込み動作により、メモリセルに第k閾値電圧、第(k−1)閾値電圧…第2閾値電圧の(k−1)値の閾値電圧を書き込む。

(もっと読む)

61 - 80 / 143

[ Back to top ]