Fターム[5F101BF09]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | リーク短絡防止 (498)

Fターム[5F101BF09]に分類される特許

401 - 420 / 498

酸窒化処理装置及び方法、並びに半導体装置の製造方法

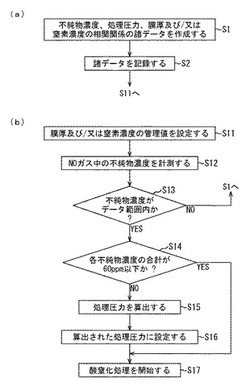

【課題】NOガスを処理ガスとして用いた酸窒化処理を行うに際して、当該酸窒化処理により所望の膜厚及び窒素濃度のシリコン酸窒化膜を得る。

【解決手段】酸窒化処理を行うに際して、処理ガスの不純物濃度を計測し、生成される酸窒化膜の膜厚又は酸窒化膜の窒素濃度が所定範囲内の値となるように、計測された不純物濃度に応じて当該酸窒化処理を行う。ここで、詳細には、処理ガス中の不純物濃度と膜厚又は窒素濃度との相関関係を予め計測し規定しておく。そして、当該相関関係に基づき、膜厚又は窒素濃度が所定範囲内の値となるように、計測された不純物濃度に応じて、具体的には酸窒化処理における処理圧力を調節設定して当該処理を行う。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ワード線間のリーク電流を低減できるようにする。

【解決手段】セルユニットUCの形成領域R1のX方向外側領域R2に各ワード線WLの分断部WLc1、WLc2が設けられており、ダミーワード線DWLがワード線WLの端部WLa、WLb(コンタクト領域RC)脇にY方向に離間して浮遊状態に設けられている。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】周辺トランジスタの駆動特性の劣化を抑制できる不揮発性半導体メモリを提供する。

【解決手段】不揮発性半導体メモリは、第1の領域を取り囲む有機物を含む第1の素子分離絶縁膜9と、第1の領域内に配置されるメモリセルと、第2の領域を取り囲む有機物を含む第2の素子分離絶縁膜9と、第2の領域内に配置される周辺トランジスタHVTrと、第2の素子分離絶縁膜9の側面に沿って、半導体基板1内に設けられる不純物層7と、素子分離絶縁膜9の底面に沿って、p型の第1の不純物層8とを備える。素子分離絶縁膜9の側面に沿って不純物層7を設けることで、有機物に起因する固定電荷トラップの影響を緩和でき、不揮発性半導体メモリに用いられる周辺トランジスタ、例えばイントリンシック領域内に設けられるnチャネル型の高耐圧系MISトランジスタの逆ナローチャネル効果を抑制できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極間絶縁膜に生じるシームなどの埋込み欠陥の露出を抑制できるようにしてゲート電極間ショートを防止できるようにする。

【解決手段】多結晶シリコン層6bを種として選択成長された選択成長部6cがシリコン酸化膜8、9上に突出して張り出して形成される。その後、多結晶シリコン層6b、6cをシリサイド化することで、金属反応領域を拡大することができ、制御ゲート電極CG(ワード線WL)を低抵抗化することができる。

(もっと読む)

不揮発性メモリトランジスタ

【課題】書き換え可能な不揮発性メモリトランジスタであって、書き換えの繰り返しによる閾値電圧特性の変化が抑制された信頼性の高い不揮発性メモリトランジスタを提供する。

【解決手段】第1導電型の半導体基板31の表層部に、第2導電型のソース領域32とドレイン領域33が形成され、トンネル酸化膜41を介して、半導体基板31上でドレイン領域33に部分的に重なるようにして、浮遊ゲート電極51が設けられてなる書き換え可能な不揮発性メモリトランジスタ100であって、ソース領域32とドレイン領域33を最短距離で結ぶ断面において、ドレイン領域33と浮遊ゲート電極51の重なり寸法Lが、0.15μm以上、0.5μm以下、である不揮発性メモリトランジスタ100とする。

(もっと読む)

不揮発性メモリデバイス用インターポリ誘電体を形成するための統合スキーム

【課題】 不揮発性メモリデバイスの漏れ電流を維持するか又は減少させつつ、デバイス寸法の減少を可能にする電子デバイス及び電子デバイスを形成する方法の提供。

【解決手段】 一実施形態において、不揮発性メモリデバイスを製造する方法は、基板上にフローティングゲート多結晶層を堆積させるステップと、フローティングゲート多結晶層上に酸化シリコン層を形成するステップと、酸化シリコン層上に第一酸窒化シリコン層を堆積させるステップと、第一酸窒化シリコン層上に高k誘電物質を堆積させるステップと、高k誘電物質上に第二酸窒化シリコンを堆積させるステップと、第二酸窒化シリコン層上に制御ゲート多結晶層を形成するステップとを含む。一実施形態において、高k誘電物質層は、酸窒化シリコンハフニウムを含む。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクト抵抗の増加やリーク電流の発生のないビット線コンタクト構造を有する不揮発性半導体記憶装置を提供することにある。

【解決手段】基板100表面にビット線109、基板100上のビット線109間に電荷捕獲機能を有するゲート絶縁膜104、ゲート絶縁膜104上にビット線109に直交するワード線114、ワード線114間にワード線間埋め込み絶縁膜115が形成されている。ビット線コンタクト形成領域において、ワード線間埋め込み絶縁膜115に開口部が形成され、この開口部側面に側壁膜117が形成されており、ワード線114間に形成されたビット線コンタクト121は、開口部側面に形成された側壁膜117に対して自己整合的に形成されてビット線109と接続している。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】コンタクトプラグ間にブリッジが発生するのを防止し、ビット線不良の防止に有効なフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板100上に形成された第1及び第2の層間絶縁膜104,114をエッチングして、セル領域の接合領域を露出させる第1及び第2のコンタクトホール106,116を形成する。このコンタクトホールの内部に第1及び第2の層間絶縁膜の界面よりも低くコンタクトプラグ110,118aを形成する。コンタクトプラグ上部のコンタクトホールの側壁にスペーサ120aを形成する。それによって、例えば導電性残留物層112及び第1及び第2の層間絶縁膜界面に発生したオープンパスのためにドレインコンタクトプラグ間で連結するブリッジを防止する。また、ドレインコンタクトプラグと接続されるビット線にて漏洩電流を誘発するなどの不良を防止し、工程の歩留まり及び素子の信頼性を向上させる。

(もっと読む)

不揮発性半導体メモリ装置

【課題】高電界領域でリーク電流が少ない高誘電率材料を提案する。

【解決手段】本発明の例に係る不揮発性半導体メモリ装置は、第1導電型の半導体領域11と、半導体領域11内で互いに離間して配置される第2導電型のソース・ドレイン領域12と、ソース・ドレイン領域12間のチャネル領域上に配置されるトンネル絶縁膜13と、トンネル絶縁膜13上に配置される浮遊ゲート電極14と、浮遊ゲート電極14上に配置される電極間絶縁膜15と、電極間絶縁膜15上に配置される制御ゲート電極16,17とを備え、電極間絶縁膜15は、ランタノイド系金属Ln、アルミニウムAl、及び、酸素Oを含み、ランタノイド系金属とアルミニウムの組成比Ln/(Al+Ln)は、0.33から0.39までの範囲内の値をとる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】補助パターンでダミーコンタクトが形成されてもゲート電極SGとの間で短絡不良が発生するのを防止できるNAND型フラッシュメモリ装置等の半導体記憶装置を提供する。

【解決手段】ビット線コンタクト4a(CB)の形成時にマスクパターンに補助パターン4b、4cを形成する場合に、メモリセル領域MAから延長して形成される補助パターン4bの端部に位置する補助パターン4cの対応領域について、ビット線コンタクト4a(CB)を形成する領域のスペーサを除去するのと同時にその部分のスペーサを除去する。ゲート電極SLG−SLGの間のパターンニングに余裕を持たせることができ(オフセットを確保することができ)、解像した補助パターン4cの部分でダミーコンタクトホールが形成された場合でも、両脇のゲート電極SLGとの間で短絡不良が発生するのを防止することが出来る。

(もっと読む)

半導体装置

【課題】高電圧転送時におけるトランジスタの閾値電圧を低減する。

【解決手段】半導体装置は、素子分離絶縁層22により囲まれた素子領域AAを有する半導体基板21と、素子領域AA上にゲート絶縁膜25を介して設けられたゲート電極26と、素子領域AA内にゲート電極26を挟むように離間して設けられたソース領域23及びドレイン領域24とを有するトランジスタTRと、素子分離絶縁層22上にトランジスタTRを挟むように設けられ、かつチャネル長方向に延在する第1及び第2の補助配線層29、30と、トランジスタTRがオン状態である間、第1及び第2の補助配線層29、30をゲート電圧と同じ極性の電圧に設定する制御回路19とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1及び第2のゲート絶縁膜と第1及び第2のゲート電極とを具備する半導体装置に関し、第1のゲート電極と第2のゲート電極との間のリーク電流を抑制する。

【解決手段】第1及び第2のゲート絶縁膜と第1及び第2のゲート電極とを具備する半導体装置であって、前記第2のゲート絶縁膜の膜厚は、前記第1のゲート電極のワード線方向の第1エッジ部上における膜厚と、前記第1のゲート電極のワード線方向の第2エッジ部上における膜厚とがそれぞれ、前記第1のゲート電極の上面上における膜厚、前記第1のゲート電極のワード線方向の第1側面上における膜厚、前記第1のゲート電極のワード線方向の第2側面上における膜厚、前記第1のゲート電極のビット線方向の第1エッジ部上における膜厚、及び前記第1のゲート電極のビット線方向の第2エッジ部上における膜厚よりも厚い半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】 フローティングゲート電極の膜厚を厚くすることなく高いカップリング比の実現が可能で、且つ、データ保持特性に優れ、高集積化に適した半導体装置の製造方法を提供する。

【解決手段】 半導体基板1上の一部領域に第1絶縁膜6を形成し、第1絶縁膜6の形成領域と非形成領域の間で上面の高さ位置を異ならせた後、ゲート酸化膜7と第1ゲート電極膜8を、第1絶縁膜6の成膜表面の高さ位置より低くなるように前記非形成領域に形成する。そして第2絶縁膜9を堆積後、第1ゲート電極膜8の一部上面が露出するように第2絶縁膜9に対してエッチバックを施す。その後露出された第1ゲート電極膜8に対してエッチバックを施し、第1ゲート電極膜の一部領域に凹部領域15を形成する。その後、第2絶縁膜9及び第1絶縁膜6をエッチングし、凹部領域15を完全には充填しない範囲内の膜厚で全面に第3絶縁膜10を堆積し、第2ゲート電極膜11を堆積する。

(もっと読む)

半導体メモリ装置

【課題】制御ゲート線間のショートを抑制できる。

【解決手段】本発明の例に関わる半導体メモリ装置は、メモリセルアレイ領域100及びこのメモリセルアレイ領域100に隣接した引き出し配線領域150を有する半導体基板1と、メモリセルアレイ領域100に設けられたメモリセルMCと、引き出し配線領域150に設けられたコンタクトプラグCPと、引き出し配線領域150内からメモリセルアレイ領域100内にわたり設けられ、コンタクトプラグCPとメモリセルMCとを接続する制御ゲート線CGLとを具備し、メモリセルアレイ領域100内に設けられる制御ゲート線CGLは、金属シリサイド6Aを含み、引き出し配線領域内に設けられる制御ゲート線CGLは、引き出し配線領域内のいずれか一部分で、金属シリサイドを含まない。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜中に電荷蓄積部を含む不揮発性メモリセルを有する半導体装置において、不揮発性メモリ領域の面積を縮小する。

【解決手段】メモリゲート電極11Aに、局所的に電界が集中するコーナー部11cnを設け、メモリゲート電極11A中の電荷をFNトンネル動作によりゲート絶縁膜2a中の電荷蓄積部に注入する消去方式を用いる。FNトンネルにより消去時の消費電流を低減できるため、メモリモジュールの電源回路面積を低減できる。また、書込みディスターブ耐性を向上できるために、より簡易なメモリアレイ構成を採用してメモリアレイ面積を低減できる。両者の効果を併せてメモリモジュールの面積を大幅に低減し製造コストを低減できる。また、書込み消去の注入電荷中心が一致するため書換え耐性が向上する。

(もっと読む)

半導体装置およびその駆動方法、表示装置およびその駆動方法

【課題】スイッチングトランジスタおよび不揮発性のメモリトランジスタとして複数のTFTを同一の基板に形成する際において、効率的に、その製造をする。

【解決手段】第1ゲート電極311と第2ゲート電極332とが、半導体層321のチャネル形成領域321cを介して対面しているデュアルゲート構造にて、薄膜トランジスタ300を形成する。ここでは、第1ゲート絶縁膜の側の面よりも、第2ゲート絶縁膜の側の面において、凹凸が大きくなるように、半導体層321を形成する。そして、その半導体層321に対面するように、順次、第2ボトム絶縁層331b、電荷蓄積層331m、第2トップ絶縁層331tを積層することによって、第2ゲート絶縁膜331を形成する。

(もっと読む)

半導体装置

【課題】 電極間絶縁膜のリーク電流や絶縁耐圧に関する問題を防止することが可能な半導体装置を提供する。

【解決手段】 素子形成領域11を有する半導体基板10と、素子形成領域上に形成されたトンネル絶縁膜12と、トンネル絶縁膜上に形成された浮遊ゲート電極18と、素子形成領域の側面、トンネル絶縁膜の側面及び浮遊ゲート電極の下部分の側面を覆う素子分離絶縁膜16と、浮遊ゲート電極の上部分の上面及び側面を覆う電極間絶縁膜20と、電極間絶縁膜上に形成された制御ゲート電極とを備え、浮遊ゲート電極の上部分の上面及び側面に平行な方向から見て、浮遊ゲート電極の上コーナー部は丸められている。

(もっと読む)

非揮発性メモリ素子及び製造方法

【課題】データ保有時間、動作速度及び信頼性を一層改善できる非揮発性メモリ素子及び製造方法を提供する。

【解決手段】半導体基板上に金属シリケート層を含むトンネル層を形成する工程と、前記金属シリケート層上に電荷トラップ層を形成する工程と、前記電荷トラップ層上に電荷ブロック層を形成する工程と、前記電荷ブロック層上にゲート層を形成する工程とを含んで非揮発性メモリ素子製造方法を構成する。

(もっと読む)

不揮発性半導体記憶素子

【課題】データ消去動作によりメモリセルにホールトラップやゲート酸化膜の欠陥を生じさせにくく、素子特性の変動を抑制して動作の安定化を図った不揮発性半導体記憶素子を提供する。

【解決手段】単層のポリシリコン層を有する断面構造を有する不揮発性半導体記憶素子は、互いに絶縁分離されるメモリセル部a、データ消去部b、及びコントロールゲート部cを含む。メモリセル部a及びデータ消去部bはMOSトランジスタで構成され、コントロールゲート部cは、MOSキャパシタで構成される。これら3つの部位は、前記単一のポリシリコン層で構成される共通のフローティングゲートを有する。フローティングゲート6cの電位を制御してメモリセルaをオンにすることにより、フローティングゲート6aにデータを書き込み、フローティングゲート6cの電位を制御してデータ消去部bをオンにすることにより、フローティングゲート6bを通じてデータを消去する。

(もっと読む)

不揮発性メモリ素子の製造方法

【課題】ウエハ全域において、EFH(Effective Field oxide Height)の不均一性を最小化し、しきい値電圧均一性を確保可能な不揮発性メモリ素子の製造方法を提供すること。

【解決手段】基板200上に、ゲート絶縁膜201、第1ゲート導電膜202、第1犠牲膜204及び第2犠牲膜206を形成するステップと、第1犠牲膜及び第2犠牲膜、第1ゲート導電膜、ゲート絶縁膜、及び基板をエッチングし、トレンチを形成するステップと、トレンチが埋め込まれるように、第1絶縁膜を形成するステップと、第2犠牲膜を停止膜として第1絶縁膜を研磨するステップと、第2犠牲膜を除去するステップと、第1絶縁膜をトレンチの内部で一定の深さに後退させるステップと、トレンチ内の空間が埋め込まれるように、第2絶縁膜を形成するステップと、第1犠牲膜を研磨停止膜として第2絶縁膜を研磨するステップとを含む。

(もっと読む)

401 - 420 / 498

[ Back to top ]