Fターム[5F101BF09]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | リーク短絡防止 (498)

Fターム[5F101BF09]に分類される特許

441 - 460 / 498

半導体装置およびその製造方法

【課題】層間絶縁膜による埋め込み時にボイドが発生するのを効果的に抑制でき、したがってコンタクトプラグ間の短絡を解消できる半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面で活性領域30Aを仕切るように、素子分離領域7を定める凹溝を形成する。凹溝内に第1の絶縁膜7を埋め込む。第1の絶縁膜7の表面を平坦化する。第1の絶縁膜7を所定の厚さ分だけエッチングする。第1の絶縁膜7をエッチングすることにより生じた帯状の窪みを、第2の絶縁膜9で埋め込む。この第2の絶縁膜9の表面は基板表面よりも高いレベルにある。半導体基板1上にポリシリコン膜11wを堆積する。フォトリソグラフィおよび第2の絶縁膜9に対して選択的なエッチングを行って、ポリシリコン膜11wを、素子分離領域7に対して垂直に互いに平行に帯状に延びるゲート電極配線に加工する。それから、層間絶縁膜19を堆積する。

(もっと読む)

半導体装置

【課題】金属または金属シリサイドを含む制御電極と蓄積電荷層との間に設けられる絶縁膜の薄膜化に伴う絶縁耐圧不足およびリーク電流の増加を抑制できる半導体装置を提供すること。

【解決手段】複数のメモリセルが並んだメモリセルアレイを含む半導体装置であって、前記メモリセルは、半導体基板上に設けられた第1の絶縁膜11と、第1の絶縁膜11上に設けられた蓄積電荷層12,18と、蓄積電荷層12,18上に設けられた第2の絶縁膜19−23と、蓄積電荷層12,18上に第2の絶縁膜19−23を介して設けられ、金属シリサイドを含む制御電極29とを具備してなり、前記メモリセルのチャネル幅方向において、制御電極29の下部角部24は、半導体で構成され、かつ、前記金属を含まないことを特徴とする。

(もっと読む)

不揮発性半導体メモリ装置及びその製造方法

【課題】

本発明の課題は、希土類元素を含む希土類酸化物、希土類窒化物、または、希土類酸窒化物を電極間絶縁膜やブロック絶縁膜として用いる場合、後熱工程に起因する膜質劣化を抑制し結晶化や誘電率低下を回避して、セル動作特性の良好な不揮発性半導体メモリ装置およびその製造方法を提供することにある。

【解決手段】

本発明では、1種類以上の希土類第1の元素、及び、Al、Ti、Zr、Hf、Ta、Mg、Ca、Sr、Baから選ばれた1種類以上の第2の元素を含む電極間絶縁膜やブロック絶縁膜を用いる場合に、第1の元素と第2の元素の組成比(第1の元素の原子数/第2の元素の原子数)を浮遊ゲート電極や電荷蓄積層に接する側では低く、制御ゲート電極に接する側では高く、かつ連続的に変化するように設定する。

(もっと読む)

半導体装置

【課題】製造工程の増大を最小限に抑制しつつ、ソース拡散層の低抵抗化を実現できるメモリセルアレイ構造を備えた半導体装置を提供する。

【解決手段】縞状に配置された、直線形状を有するドレイン拡散層10およびソース拡散層12と、縞状に配置された、直線形状を有する素子分離領域14と、拡散層10,12、素子分離領域14に直交し、縞状に配置された、直線形状を有する制御ゲート18と、制御ゲート18と平行に、かつ、縞状に配置された、直線形状を有するソース配線用金属配線層20aと、ドレイン拡散層10それぞれと接続する、孤立する島形状を有するドレイン接続用金属配線層20bとから成るメモリセルアレイ構造を備えた不揮発性半導体メモリである。金属配線層20aと20bは、同一の金属配線層から構成される。

(もっと読む)

半導体素子のキャパシタ形成方法

【課題】キャパシタ内の揮発性副産物を除去して電極の伝導性を向上させ、より高い静電容量が得られる半導体素子のキャパシタ形成方法を提供する。

【解決手段】半導体基板上にストレージノード電極を形成する工程と、ストレージノード電極上に、高誘電定数を持つ誘電体膜を形成する工程と、誘電体膜上にプレート電極を蒸着する工程と、プレート電極上にキャッピング膜を蒸着しながら当該半導体基板上に水素原子(H)を含有するガスを供給して、当該電極内に残留する反応不純物を排出させる工程と、を含む構成とした。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明では、酸素欠損を低減させ、信頼性を改善した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】第1の発明の半導体装置は、基板と、基板に形成された半導体領域と、半導体領域上に形成され、1種以上の第1金属元素の酸化物で形成された絶縁膜と、絶縁膜上に形成され、酸化物の生成自由エネルギーについて第1金属元素よりも大でありかつ金属状態である第2金属元素、および第1金属元素の酸化物で形成された遷移層と、遷移層上に形成された電極と、電極をゲート長方向に挟む半導体領域に形成されたソース・ドレイン領域とを備えたことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ワード線間のリークの発生を抑制することが可能な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、基板100内に列方向に延伸する拡散層ビット線110と、拡散層ビット線110の上に形成され、列方向に延伸するビット線上絶縁膜112と、基板100のうち平面的に見て拡散層ビット線110の間に位置する領域の上に形成された電荷捕獲層104と、電荷捕獲層104上に形成された第1のゲート電極膜105と、第1のゲート電極膜105およびビット線上絶縁膜112の上に形成され、行方向に延伸する第2のゲート電極膜113とを備えている。ビット線上絶縁膜112はテーパ形状で形成され、行方向における中央部に設けられた埋め込み酸化膜111の膜厚が、両端部に設けられた注入オフセット膜109の膜厚よりも大きい。

(もっと読む)

不揮発性記憶装置及びその動作方法

【課題】不揮発性記憶装置及びその動作方法を提供する。

【解決手段】本発明の装置は、n番目のビットラインに連結された第1トランジスターと、n+1番目のビットラインに連結された第2トランジスターとを含む。前記第1トランジスター及び前記第2トランジスターは、n番目のビットラインとn+1番目のビットラインとの間に直列に連結される。記憶セルのソース領域及びドレーン領域の構造が同一または類似の2トランジスター1ビット単位セルを有する不揮発性記憶装置を形成できる。また、2トランジスター2ビット単位セルを有することができるために記憶容量が2倍に増加できる。

(もっと読む)

垂直配向ナノロッドを持つ低リークDRAMメモリセルとその製造方法

半導体メモリストレージセルにおいてリーク電流を減らすための方法と構造が記載される。垂直配向ナノロッド(403)が、アクセストランジスタ(400)のチャネル領域で使用され得る。ナノロッドの直径は、アクセストランジスタのチャネル領域内の電子バンドギャップエネルギーの増加を引き起こすために十分小さくすることができ、これはオフ状態でのチャネルリーク電流を制限するように機能し得る。様々な実施形態では、アクセストランジスタは両面キャパシタ(425)に電気的に結合し得る。本発明の実施形態に従うメモリデバイス、およびそのようなデバイスを含むシステムもまた開示される。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置

【課題】フローティングゲートの端部付近でのバーズビークが抑制できると共に、製造コストを安くすることができる不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板1に分離部2を形成する分離工程と、シリコン基板1の主表面にゲート絶縁膜3を形成する絶縁膜形成工程と、ゲート絶縁膜3の表面にフローティングゲート4をなすポリシリコンを形成するポリシリコン形成工程と、そのポリシリコンの表面に第1酸化膜5を形成する第1酸化膜形成工程と、第1酸化膜の表面に窒化膜6を形成する窒化膜形成工程と、不揮発性メモリ部における窒化膜6の表面にレジスト30を形成し、ポリシリコン、第1酸化膜5、窒化膜6、ゲート絶縁膜3をエッチングするエッチング工程と、レジストを除去し、全面にゲート間絶縁膜及び、CMOSのゲート酸化膜をなす第2酸化膜7を形成する第2酸化膜形成工程とを備える。

(もっと読む)

半導体装置

【課題】不揮発性メモリの書き込み・消去特性、電荷保持特性、ディスターブ抑制特性を向上させる。

【解決手段】トンネル絶縁膜20を酸化シリコン膜(第2絶縁膜22)と、酸化シリコン膜以外の絶縁膜(第1絶縁膜21、第3絶縁膜23)との積層膜で構成した不揮発性メモリにおいて、0V印加時の制御ゲートのリーク電流が減少し、半選択モードにおけるディスターブ時に流れるリーク電流が減少し、書き込み終了時に流れる電流が多くなるための条件を、各種動作電圧、層間膜容量、書き込み終了時閾値、消去終了時閾値、初期閾値、積層膜の比誘電率とバリアの高さ、膜厚をパラメータとして限定する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊ゲート間の電荷移動によるデータ破壊を防止して信頼性向上を図った不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板1にストライブ状の素子形成領域2を区画する素子分離絶縁膜4が埋め込まれる。この基板1に第1のゲート絶縁膜5を介して浮遊ゲート6が形成され、更に第2のゲート絶縁膜7を介して制御ゲート8が形成される。制御ゲート8に自己整合的にソース、ドレイン拡散層12が形成される。浮遊ゲート6上の第2のゲート絶縁膜7は、浮遊ゲート6と共に、素子分離絶縁膜4上でスリット13により隣接するメモリセル間で分離される。

(もっと読む)

フラッシュメモリ素子の製造方法{Methodofmanufacturingaflashmemorydevice}

【課題】フラッシュメモリ素子の製造方法に関するものであり、窒化膜を用いて周辺領域のトランジスタの特性の低下を防止する方法を提供する。

【解決手段】半導体基板101の表面にトンネル酸化膜103を形成する前に周辺領域で保護用パターン102aを形成し、ゲートエッチング工程時に周辺領域のトランジスタの側壁をプラズマエッチングから保護する。

(もっと読む)

不揮発性半導体メモリ

【課題】IPDリークの抑制によりメモリセルの微細化を実現する。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、半導体基板11と、半導体基板上11の第1絶縁層13と、第1絶縁層13上のフローティングゲート電極FGと、フローティングゲート電極FG上の第2絶縁層15と、第2絶縁層15上のコントロールゲート電極CGとを備え、フローティングゲート電極FGは、第1絶縁層13に接触する第1金属層14aと、第2絶縁層15に接触する第2金属層14bと、第1及び第2金属層14a,14bの間の半導体層14cとから構成される。

(もっと読む)

半導体装置の作製方法及び不揮発性半導体記憶装置の作製方法

【課題】絶縁耐圧の良好な絶縁層を製造する技術を提供することを目的とする。また、絶縁耐圧の良好な絶縁層を有する半導体装置を製造する技術を提供することを目的とする。

【解決手段】シリコンを主成分とする半導体層若しくは半導体基板に対して高密度プラズマ処理を行うことにより、半導体層の表面若しくは半導体基板の上面に絶縁層を形成する。このとき、供給ガスを希ガス、酸素及び水素を含むガスから希ガス及び酸素を含むガスに途中で切り替えて高密度プラズマ処理を行う。

(もっと読む)

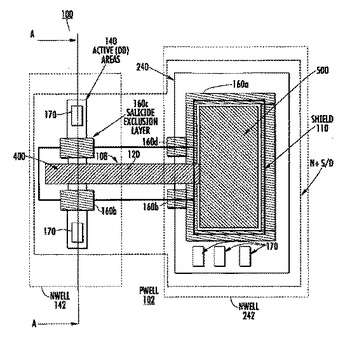

フローティングゲートトンネリング素子構造体のシールド

フローティングゲートトンネリング素子をシールドする方法とその構造体。標準的なCMOSプロセスを用いて、電界酸化物に囲まれた基板内に形成された第1および第2のドープウェル領域により定義される2つの活性領域内のゲート酸化物上にフローティングゲートを配置する工程と、前記フローティングゲートを囲むようにフローティングゲートシールド層を形成する工程を含む方法。前記フローティングゲートは、前記第1のドープウェル領域内の活性領域上の第1のフローティングゲート部および前記第2のドープウェル領域内の活性領域上の第2のフローティングゲート部を含む。前記第1のドープウェル領域と前記第1のフローティングゲート部との間にファウラーノルドハイムトンネリングのための適当な電圧カップリングが発生しうるよう、前記第1のフローティングゲート部は第2のフローティングゲート部より実質的に小さくなっている。トンネリングの方向は、前記ドープウェル領域の1つに高電圧を印加することにより決定される。  (もっと読む)

(もっと読む)

半導体素子の金属配線とその形成方法

【課題】奇数番(odd)の列と偶数番(even)の列に位置するビット線間のローディングキャパシタンスを減少させ、ビット線どうしが接触するビットラインブリッジの発生を防止できる半導体素子の金属配線とその形成を提供する。

【解決手段】第1金属配線と第2金属配線とを異なる層に段差をもって形成する。そうすることで第1,第2金属配線どうしの間隔が拡大し、配線間のロードキャパシタンスを減少させ、配線どうしの接触による相互干渉でいわゆるブリッジが発生するのを有効に防止できる。たとえば、第1金属配線が奇数番の列に位置するオードビット線115であり、第2金属配線が偶数番の列に位置するイーブンビット線121であるような場合、オードビット線115とイーブンビット線121を異なる層に段差をもって形成する。それによって、オードビット線115とイーブンビット線121との距離が拡大されるので、ビットラインブリッジの発生を防げる。

(もっと読む)

浮遊ゲートメモリデバイスと製造

互いに分離されたゲート間誘電領域を持つトランジスタを含む浮遊ゲートメモリアレイと、それを製造する方法。浮遊ゲートトランジスタは、アレイ内の浮遊ゲートトランジスタの各々が、浮遊ゲートと、制御ゲートと、その間にゲート間誘電層を持つように形成される。各トランジスタのゲート間誘電層は、アレイ内の他のトランジスタの各々のゲート間誘電体から分離される。そのような構造を製造する方法も提供される。  (もっと読む)

(もっと読む)

強誘電体メモリセル及び強誘電体メモリセルの製造方法

【課題】配向性制御に優れ、高耐圧で低リーク電流特性の強誘電体膜を備えるメモリセルを実現する。

【解決手段】素子分離領域13に挟まれたソース/ドレイン領域12と、ゲート絶縁膜14と、ゲート電極15と、第1層間絶縁膜21と、第1層間絶縁膜21中に配置され,ソース/ドレイン領域12に接続されるコンタクトプラグ31と、コンタクトプラグ31に接続される下部電極42と、下部電極42上に配置される強誘電体膜43と、強誘電体膜43上に配置される上部電極44と、第2層間絶縁膜61と、上部電極44と接続されるキャパシタコンタクトプラグ71と、ソース/ドレイン領域に接続される基板コンタクトプラグ72と、キャパシタコンタクトプラグ71,及び基板コンタクトプラグ72に接続される配線層80,81とを備え、強誘電体膜43は、強誘電体の微小結晶を含むゾルゲル液を堆積して形成する強誘電体メモリセル及びその製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 制御電極と電荷蓄積層との間の絶縁膜を改善することにより、優れた半導体装置を提供する。

【解決手段】 半導体基板11と、半導体基板上に形成された第1の絶縁膜12と、第1の絶縁膜上に形成された電荷蓄積層13と、電荷蓄積層上に形成された第2の絶縁膜20と、第2の絶縁膜上に形成された制御電極21とを備えた半導体装置であって、第2の絶縁膜は、下層シリコン窒化膜204と、下層シリコン窒化膜上に形成された下層シリコン酸化膜201と、下層シリコン酸化膜上に形成され且つ金属元素を含有した7よりも高い比誘電率を有する中間絶縁膜202と、中間絶縁膜上に形成された上層シリコン酸化膜203と、上層シリコン酸化膜上に形成された上層シリコン窒化膜205とを含む。

(もっと読む)

441 - 460 / 498

[ Back to top ]