Fターム[5F101BF09]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | リーク短絡防止 (498)

Fターム[5F101BF09]に分類される特許

361 - 380 / 498

不揮発性半導体記憶装置及びその製造方法

【課題】コントロールゲート電極を低抵抗化し、高速動作が可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板10のチャネル領域上に形成された電荷蓄積層11と、電荷蓄積層11上に形成されたコントロールゲート電極30と、コントロールゲート電極30上に形成されたシリサイド層63と、コントロールゲート電極30の側方に絶縁層15を介して形成されたワードゲート電極20とを具備する。シリサイド層63の上面は平坦である。

(もっと読む)

半導体装置の製造方法

【課題】一体型構造をしたゲート電極を有する半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体基板10上に電荷蓄積層14を含む積層膜18を形成する工程と、積層膜上に延伸して形成されたマスク層20の側壁に第1スペーサー層36を形成する工程と、マスク層と第1スペーサー層とをマスクに積層膜を除去して第1開口部38を形成する工程と、第1スペーサー層を除去した後、第1開口部にゲート酸化膜22を形成する工程と、マスク層間であって、積層膜上とゲート酸化膜上とにゲート電極28を形成する工程と、マスク層を除去した後、ゲート電極をマスクに積層膜を除去して第2開口部40を形成する工程と、第2開口部で画定され、半導体基板内を延伸するビットライン30を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

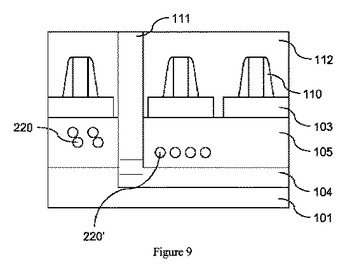

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】電荷蓄積層をチャネル方向で分離させた場合でも、半導体基板にシリサイド層が形成されることを抑制すること。

【解決課題】本発明は、半導体基板10内に延伸して設けられたビットライン12と、ビットライン12間中央部の半導体基板10上に、ビットライン12延伸方向に延伸して設けられたゲート絶縁膜20と、半導体基板10上に、ビットライン12幅方向でゲート絶縁膜20を挟むように、ビットライン12延伸方向に延伸して設けられた電荷蓄積層26と、ゲート絶縁膜20上に設けられた、ゲート絶縁膜20と異なる材料からなる第1絶縁膜42と、電荷蓄積層26上と第1絶縁膜42上とに設けられた、ビットライン12に交差して延伸するワードライン14と、ワードライン14上部に設けられたシリサイド層22と、を具備する半導体装置及びその製造方法である。

(もっと読む)

フラッシュメモリ及びその製造方法

【課題】30nm以下の微細化に適応できるフラッシュメモリ及びその製造方法を提供する。

【解決手段】基板101に接続された上部にスペーサ絶縁膜116を有するフィン構造のビットラインから形成されたメモリセル部の最小加工寸法をFとするとき、独立に書き込み/消去可能なビットライン2本が対になって4F周期に配置されてメモリセル部が形成され、一対のフィンの上部を覆うように記憶絶縁膜が形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】リテンション耐性の良好な不揮発性半導体記憶装置を提供する。

【解決手段】1つのメモリセルMCが導電性電荷蓄積層と絶縁性電荷蓄積層ECSとを有している。導電性電荷蓄積層はフローティング電位を有する第1のゲート電極層GE1であり、1対のソース/ドレイン領域SDに挟まれる半導体基板SUBの主表面上に第1のゲート絶縁層GI1を介して形成されている。絶縁性電荷蓄積層ECSは第2のゲート絶縁層GI2に含まれ、1対のソース/ドレイン領域SDに挟まれる半導体基板SUBの主表面上に形成されている。第1のゲート電極層GE1上のコントロールゲート部分CGと第2のゲート絶縁層GI2上のメモリゲート部分MGとは電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】欠陥が生成されにくい高品質な絶縁膜を得ることを可能にするとともにリーク電流を低減することを可能にする。

【解決手段】絶縁層2上にアモルファスシリコン層を形成するステップと、アモルファスシリコン層に酸素を導入するステップと、酸素が導入されたアモルファスシリコン層を窒化し、シリコン酸窒化層3を形成するステップと、を備えている。

(もっと読む)

不揮発性半導体メモリ装置

【課題】フローティングゲート電極とコントロールゲート電極を積層したスタックゲート構成において、トンネル絶縁膜と電極間絶縁膜を改良した不揮発性半導体メモリ装置を提供する。

【解決手段】第1導電型の半導体基板10の主面上にトンネル絶縁膜11を介して選択的に形成されたフローティングゲート電極12と、フローティングゲート電極12上に電極間絶縁膜13を介して形成されたコントロールゲート電極14と、各ゲート電極12,14に対応して基板10の主面に形成された第2導電型のソース・ドレイン領域15とを備えた不揮発性半導体メモリであって、トンネル絶縁膜11は、少なくとも2種の金属元素(Al,Hf)と酸素(O)を含む高誘電体膜であり、膜の厚さ方向に対して金属元素の組成が連続的に変化し、かつ対称的な分布を有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】トランジスタの動作時に半導体基板から制御ゲート電極に抜けるリーク電流を低減して閾値のばらつきを低減させる

【解決手段】シリコン基板1は、トレンチ1aに素子分離用絶縁膜2aを埋め込んでSTI2を形成し、活性領域3を分離形成している。シリコン基板1の活性領域3の表面には第1のゲート絶縁膜5、浮遊ゲート電極6、第2のゲート絶縁膜7、制御ゲート電極8が積層形成されたゲート電極MGが設けられている。STI2のトレンチ1aの内壁面には素子分離用絶縁膜2aとの間に5Åの膜厚のアルミナ膜からなる絶縁薄膜4が設けられている。これにより、素子分離用絶縁膜2aがポリシラザンのような塗布型酸化膜を用いた場合でも、不純物に起因した固定電荷を中和してリーク電流の低減を図れる。

(もっと読む)

半導体装置の製造方法

【課題】隣接するメモリセル間の干渉に起因するメモリセルの誤動作を回避する半導体装置の製造方法を提供する。

【解決手段】本発明の例に関わる半導体装置の製造方法は、半導体基板上に、トンネル絶縁膜を挟んで、上部及びチャネル幅方向の側部の一部が露出する複数の浮遊ゲート電極10aを形成する工程と、浮遊ゲート電極103aの露出表層部を化学反応させて、電極間絶縁膜の最下層となる第1の絶縁膜109aを浮遊ゲート電極103a上に形成するのと同時に、浮遊ゲート電極103aの上部のチャネル幅方向の幅を、浮遊ゲート電極103aの下部のチャネル幅方向の幅よりも狭くする工程と、電極間絶縁膜109a上に互いに対向する浮遊ゲート電極103aの間に一部が埋め込まれている制御ゲート電極を形成する工程と、を具備する。

(もっと読む)

不揮発性半導体メモリ

【課題】メモリセルの駆動電圧及びリーク電流を低減ができ、さらに、カップリング比を向上できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、半導体基板内の素子分離領域によって分離される素子領域と、前記素子領域上に設けられるゲート絶縁膜2Aと、前記ゲート絶縁膜上に設けられる電荷蓄積層3Aと、電荷蓄積層3A上に設けられる多層絶縁体4Aと、多層絶縁体4A上に設けられるコントロールゲート電極5Aとを具備し、ゲート絶縁膜2Aは、第1トンネル膜21と、第1トンネル膜21よりも誘電率が高い第1高誘電率膜22と、第1トンネル膜21と同一構成の第2トンネル膜22を含み、多層絶縁体4Aは、第1絶縁膜41と、第1絶縁膜41よりも誘電率が高い第2高誘電率膜42と、第1絶縁膜41と同一構成の第2絶縁膜42とを含んでいることを備える。

(もっと読む)

半導体記憶装置及びその製造方法と駆動方法

【課題】寄生抵抗の増大なく、ホットキャリアによる特性劣化を抑制できる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】ガラス基板1上に形成した半導体層3と、半導体層3上に形成したONO膜による電荷保持膜21と、電荷保持膜21上に設けたゲート電極22とを備える。更に半導体層3にゲーート電極22とオーバーラップするように設けられたニッケルシリサイド等の半導体と金属の化合物からなるソース・ドレイン領域23を有する。

(もっと読む)

半導体記憶装置及びその製造方法と半導体記憶装置の動作方法

【課題】書込み速度の向上と、かつ読出しディスターブの抑制を両立させることが可能な半導体記憶装置を提供する。

【解決手段】半導体層上に電荷蓄積膜とゲート電極105を形成し、ゲート電極105の下部に形成されたチャネル領域の両側の半導体層に2つの第1導電型の拡散領域A及びBを形成する。チャネル領域は、一方の拡散領域Aが接する側のチャネル幅Waよりも他方の拡散領域Bが接する側のチャネル幅Wbの方が大きく形成される。記憶動作時には一方の拡散領域Aへ他方の拡散領域Bよりも高い電圧を印加し、読出し時には他方の拡散領域Bへ一方の拡散領域Aよりも高い電圧を印加する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】Fin型構造を採用した半導体記憶装置においてカップリング比の各メモリセル間のバラつきを抑制する。また複数のアクティブエリア間のリーク電流を抑制する。

【解決手段】シリコン基板2の主表面高さは均一に形成されていると共にシリコン酸化膜3の上面高さは均一に形成されている。シリコン酸化膜3がSIMOX法により形成され、アクティブエリアSaがシリコン酸化膜3の上面上まで達する素子分離溝2gによって複数に分断されている。したがって、素子分離溝2gの深さおよびアクティブエリアSaの高さを各メモリセル間でほぼ等しい高さに調整でき、隣り合うアクティブエリアSa−Sa間がシリコン酸化膜3によって互いに電気的に絶縁状態に保たれる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安価に高集積化された不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、電気的に書き換え可能な複数のメモリトランジスタが直列に接続された複数のメモリストリングスを有する。メモリストリングスは、半導体基板Baに対して垂直方向に延び且つ上端から下方に延びる中空を有するメモリ柱状半導体層37と、メモリ柱状半導体層37の外壁に接して形成されたトンネル絶縁層36cと、中空に面するメモリ柱状半導体層37の内壁に形成されたメモリホール第1の絶縁層38aと、メモリ柱状半導体層37と共にトンネル絶縁層36cを挟むように形成された第1〜第4ワード線導電層32a〜32dとを備える。第1〜第4ワード線導電層32a〜32dは、メモリトランジスタの制御電極として機能する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】不揮発性半導体記憶装置を高集積化および高信頼度化する方法を提供する。

【解決手段】複数のメモリセルが、ウェル(p型半導体領域102)よりも深く、Y方向に延在した複数の素子分離(シリコン酸化膜103)によって区画された複数のアクティブ領域に形成されている。各メモリセルでは、ソース拡散層(n+型半導体領域115)を貫通するようにウェル(p型半導体領域102)にコンタクト116が設けられており、ビット線(メタル配線117)とソース拡散層(n+型半導体領域115)とを電気的に接続するコンタクト116がウェル(p型半導体領域102)とも電気的に接続されている。

(もっと読む)

半導体素子及びその製造方法

【課題】金属配線を電気的に連結させるビアプラグを形成する工程過程で発生する素子の信頼性を低下させる問題を解消すること。

【解決手段】半導体基板上に多数の金属配線を形成する段階;ビアホールが形成される領域の前記金属配線上に反応防止膜を形成する段階;前記反応防止膜を含む前記半導体基板上に層間絶縁膜を形成する段階;前記反応防止膜の上部の前記層間絶縁膜をエッチングしてビアホールを形成する段階;前記ビアホール内部にビアプラグを形成する段階を含む半導体素子の製造方法。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】デバイス間バラツキや誤動作が起こりにくく信頼性の高い、かつ消費電力が抑えられた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、絶縁体上に形成された第1導電型の半導体層100と、半導体層100上に形成された電荷蓄積機能を有する電荷蓄積膜103及び電荷蓄積膜103上に形成されたゲート電極105aと、ゲート電極105aの下方の半導体層100に形成されたチャネル領域108と、チャネル領域108の両側に、半導体層100内に形成された第2導電型の拡散領域106,107と、半導体層100を延長して形成した第1導電型のボディコンタクト領域109と、延長した半導体層100上にゲート電極105aを延長し、ボディコンタクト領域109と、チャネル領域108の両側の拡散領域106,107を分離するゲート電極引き出し部105bとを備える。

(もっと読む)

高κキャップ阻止誘電体‐バンドギャップ操作SONOS及びMONOS

【課題】阻止誘電体操作電荷トラップメモリーセルを提供する。

【解決手段】この阻止誘電体操作電荷トラップメモリーセルは、阻止誘電体によってゲートから分離された電荷トラップ要素を備える。該阻止誘電体は該電荷トラップ要素に接し高品質に作ることができる二酸化シリコン等のバッファ層(第1層)と、該ゲートに接するキャップ層(第2層)とを含む。該キャップ層は第1層より高い誘電率を有し、高κ材料でできているのが好ましい。第2層は相対的に高い伝導帯オフセットも有している。チャネルと該電荷トラップ要素の間にバンドギャップ操作トンネル層が設けられ、該多層阻止誘電体と組合わされて正孔トンネル現象による高速消去動作を可能にする。或いは、単一層からなるトンネル層が使用されてもよい。

(もっと読む)

不揮発性半導体メモリ及びデータプログラム/消去方法

【課題】電荷トラップ型の不揮発性半導体メモリにおいて、消費電流を低減すること。

【解決手段】不揮発性半導体メモリは、半導体基板1、第1ゲート電極WG、第2ゲート電極CG、電荷トラップ膜22、及びトンネル絶縁膜23を備える。第1ゲート電極WGは、半導体基板1の表面上に第1ゲート絶縁膜10を介して形成される。第2ゲート電極CGは、半導体基板1の表面上に第2ゲート絶縁膜20を介して形成され、第1ゲート電極WGと絶縁膜20を介して隣接する。電荷トラップ膜22は、半導体基板1と第1ゲート電極WGと第2ゲート電極CGとに囲まれたトラップ領域RT中に少なくとも形成される。トンネル絶縁膜23は、電荷トラップ膜22と第2ゲート電極CGとの間に形成される。プログラムあるいは消去において、FNトンネル方式により、第2ゲート電極CGから電荷トラップ膜22へトンネル絶縁膜23を通して電子が注入される

(もっと読む)

361 - 380 / 498

[ Back to top ]