Fターム[5F101BF09]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | リーク短絡防止 (498)

Fターム[5F101BF09]に分類される特許

341 - 360 / 498

半導体記憶装置

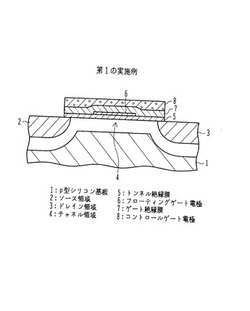

【課題】大容量化、低電圧化を図ることが可能な半導体記憶装置を提供する。

【解決手段】半導体基板1の表面層のチャネル領域4の両側に、ソース2及びドレイン3が形成されている。半導体基板1のチャネル領域4上に、トンネル絶縁膜5が形成されている。トンネル絶縁膜5の上に、フローティングゲート電極6が、ソース2及びドレイン3のいずれにも重ならないように配置されている。フローティングゲート電極6を覆うように、チャネル領域4の上方にゲート絶縁膜7が形成されている。ゲート絶縁膜7の上に、ソース2及びドレイン3に接するかまたは部分的に重なるようにコントロールゲート電極8が配置されている。フローティングゲート電極6に電荷が注入された状態において、チャネル領域4とコントロールゲート電極8との間に外部から電圧を印加しない状態のときに、フローティングゲート電極6のフェルミ準位がチャネル領域の禁制帯の中に位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路部のLV系トランジスタでの結晶欠陥の発生を抑制しつつ、HV系トランジスタでの反転リークなどの増加を抑制できるようにするNAND型フラッシュメモリの半導体装置と製造方法を提供する。

【解決手段】LV系トランジスタ領域103のSTI304の上面を、EB加工により、セル領域104のSTI404の上面と同時にエッチングする。こうして、HV系トランジスタ領域102のSTI204の上面の高さはそのままに、LV系トランジスタ領域103のSTI304の上面のみを、第1の電極膜12の上面の高さよりも下げる。上面の高さを下げた分だけ、LV系トランジスタ領域103のSTI304での素子分離用絶縁膜の膜厚を削減して、塗布膜の収縮応力を緩和させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】電荷蓄積層における蓄積電荷の拡散を防ぐ半導体記憶装置及びその製造方法を提供する。

【解決手段】本発明の半導体記憶装置は、半導体基板と、半導体基板上に設けられ、複数の電極層WLと複数の絶縁層14とが交互に積層された積層体と、この積層体を貫通して形成されたホールの内部に設けられ、電極層WLと絶縁層14との積層方向に延びる半導体層SPと、電極層WLと半導体層14との間にのみ設けられ、電極層WLと絶縁層14との積層方向に分断された電荷蓄積層26とを備える。

(もっと読む)

半導体デバイスの製造方法及び基板処理装置

【課題】金属製のゲート電極(メタル電極)のダメージを熱酸化により修復する際の高誘電率ゲート絶縁膜の結晶化を抑制する。

【解決手段】エッチングにより側壁が露出した高誘電率ゲート絶縁膜とメタル電極とを有する基板を処理室内に搬入する工程と、処理室内で、基板を高誘電率ゲート絶縁膜が結晶化しない温度に加熱した状態で、基板に対してプラズマで励起した水素含有ガスと酸素含有ガスとを供給して酸化処理を施す工程と、処理後の基板を処理室内から搬出する工程と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】面積の増大を抑制しつつ、高速な動作が可能な不揮発性半導体記憶装置を提供する。

【解決手段】トレンチを有する半導体基板(2)と、トレンチ内に形成された電荷蓄積層(7)と、トレンチの一側面及び底面の一部に、第1絶縁層(8)を介して形成された第1ゲート(5)と、電荷蓄積層(7)上に形成され、第1ゲート(5)の側方に第2絶縁層(7)を介して形成された第2ゲート(6)とを備えている不揮発性半導体記憶装置を攻勢する。ここにおいて、その不揮発性半導体記憶装置は、トレンチ内の半導体基板(2)中に形成された第1拡散層(3)と、トレンチ外の半導体基板中に形成された第2拡散層(4)とを備えることが好ましい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線コンタクト部のトラップ膜の完全な除去とメモリセル部のゲート電極間の埋め込み充填絶縁膜の十分な残存量確保とを両立する。

【解決手段】複数のビット線拡散層と、複数のワード線と、一対のビット線拡散層、ゲート絶縁膜、及びゲート電極によって構成された複数のメモリ素子と、を含むメモリ領域を有する半導体記憶装置であって、各列における複数に分割された複数のビット線拡散層同士は、ビット線コンタクト拡散層を介して電気的に接続されており、ビット線コンタクト拡散層に隣り合って配置されたワード線に形成されたビット線コンタクト拡散層側の側壁絶縁膜の幅は、ビット線コンタクト拡散層側と反対側に形成された側壁絶縁膜の幅よりも狭い。

(もっと読む)

半導体記憶装置

【課題】複数の半導体メモリチップと半導体キャッシュメモリチップとを具える半導体記憶装置において、その小型化を図るとともに、動作速度及び放熱特性を向上させる。

【解決手段】配線基板の第1の主面上に、複数の半導体メモリチップを積層するとともに、前記複数の半導体メモリチップ上にインターポーザチップを積層し、さらに前記インターポーザチップ上に半導体コントローラチップを積層する。前記複数の半導体メモリチップは、それぞれ前記配線基板の内部接続用端子と配線を介して互いに独立に電気的に接続されてなり、前記インタポーザチップを介して前記配線基板の他の内部接続用端子と電気的に接続されてなる前記半導体コントローラチップによって、互いに独立に制御される。

(もっと読む)

半導体記憶装置

【課題】高耐圧トランジスタのオフ時のリーク電流を抑制し、周辺回路内部の電圧を安定化することが可能な、NAND型フラッシュメモリ等に適用される半導体記憶装置を提供する。

【解決手段】周辺回路領域PRにおいて、シリコン基板11の一部にシリコンよりバンドギャップの広いSiCやGaN等の半導体層14が形成されている。メモリセル13は、シリコン基板11内に形成されている。周辺回路を構成するトランジスタ15は半導体層14内に形成されている。半導体層14のバンドギャップは、シリコンのバンドギャップより広いため、トランジスタ15がオフ状態において、トンネル電子が発生しない。このため、GIDLの発生を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜を介して隣接し、それぞれ低い抵抗値を有する複数のシリサイド層を備え、かつ複数のシリサイド層間の耐電圧特性の劣化および短絡を抑えた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、絶縁膜を介して前記半導体基板の表面に略平行な方向に隣接する複数のSi系パターン部を形成する工程と、前記複数のSi系パターン部および前記絶縁膜上に、前記複数のSi系パターン部に接するように金属膜を形成する工程と、熱処理により前記複数のSi系パターン部と前記金属膜とをシリサイド反応させ、前記複数のSi系パターン部の全部または上側の一部をそれぞれシリサイド層に加工する工程と、前記複数のシリサイド層に平坦化処理を施し、前記絶縁膜上に形成されたシリサイド層を除去する工程と、を含む。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】電界集中を避けるためのフローティングゲート電極の上面の丸め加工で、ゲート高さのバラツキを低減する、積層ゲート構造を有する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】シリコン基板1にゲート絶縁膜5、多結晶シリコン膜6、加工用絶縁膜を積層して、RIE法によりエッチングをして溝1a、1bを形成し、溝内にシリコン酸化膜を埋め込んでCMP処理をする。メモリセル領域のみシリコン酸化膜をエッチングして落とし込み、この後、下層レジストを塗布してメモリセル領域のエッチングをする。下層レジストがエッチングされて多結晶シリコン膜6が露出すると上面端部6aが丸み加工される。これにより、多結晶シリコン膜6の上部のみを露出させて丸み加工ができ、高さのバラツキを低減できる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】リーク電流を抑制することでデータの書込/消去の速度を向上する。

【解決手段】積層膜Sが、シリコン酸化膜7、シリコン窒化膜8、金属酸化物膜9の積層構造によって構成されており、当該積層膜Sが制御ゲート電極CGとシリコン窒化膜6との間に介在して形成されている。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】ドレインディスターブ特性が満足できる半導体記憶装置を提供する。

【解決手段】溝24を有するP型半導体基板2と、前記P型半導体基板2の溝24を有しない部分の表面に形成されたN+拡散層4S、4Dと、ボトム酸化膜6、電荷蓄積窒化膜8およびトップ酸化膜10がこの順に形成され、前記溝24の側壁部および底部並びに前記N+拡散層4S、4Dの表面を覆うゲート膜12と、前記ゲート膜12のP型半導体基板2方向とは反対側の表面に形成されると共に、前記溝24を埋め込むように形成され、且つ前記溝24が連続する方向において格子状に形成されたゲート電極14と、を備える半導体記憶装置。

(もっと読む)

メモリセル構造、該メモリセル構造を用いたメモリデバイス、及び該メモリデバイスを具備した集積回路

【課題】従来のメモリセルよりも小型かつ長寿命なメモリセルのデザインを提供する。

【解決手段】メモリデバイス用メモリセル構造は、フローティングゲートノードFGを有したリードトランジスタ120と、第1プログラミング端子160を有したトンネリングコンデンサ130と、第2プログラミング端子150を有したカップリングコンデンサスタック200とを具備する。トンネリングコンデンサ130及びカップリングコンデンサスタック200は、FGに接続されている。カップリングコンデンサスタック200は、FGと第2プログラミング端子150との間に直列に接続された少なくとも2つのカップリングコンデンサから成り、トンネリングコンデンサ130よりも大きい静電容量を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】大容量の書き換えが必要なプログラムと小容量の頻繁な書き換えが必要なデータの記憶を1種類のメモリマットで両立させることができ、小型でソフト開発が容易な不揮発性半導体記憶装置を提供する。

【解決手段】書き換え可能な不揮発性メモリトランジスタTrが行列状に配置されてメモリマットが構成され、ワード線LG1〜LG4とビット線LD1〜LD4とで各不揮発性メモリトランジスタTrの書き込み、読み出しおよび消去が行われる不揮発性半導体記憶装置100であって、ワード線LG1〜LG4に連結される不揮発性メモリトランジスタTrが、当該不揮発性半導体記憶装置100を制御するOSの使用するワードの単位に分けられて、該ワード単位毎に半導体基板30に分割形成されたウエルからなるワード領域W1〜W4内に配置されてなる不揮発性半導体記憶装置100とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】製造コストを低減し且つチップサイズを大きくすることなく容量素子部の容量を大きくする。

【解決手段】半導体装置は、フローティングゲート及びコントロールゲートを備える。半導体装置は、容量素子部において、半導体基板上に形成されたゲート絶縁膜101と、ゲート絶縁膜101上に形成された下部電極102cと、下部電極102c上に形成された、下部電極102cを露出する開口部を有するキャップ絶縁膜103と、キャップ絶縁膜103の側面上及び開口部により露出された下部電極102c上に形成されたゲート間絶縁膜106と、ゲート間絶縁膜106上に形成された上部電極108と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離領域の深さを抑制しながら耐圧の低下を抑制できるNAND型フラッシュメモリ等の半導体装置を提供する。

【解決手段】ゲート電極PGが、隣り合う素子分離膜間のアクティブエリアAA上にゲート絶縁膜11を介してゲート長方向に離間して並設されている。ゲート電極PGを構成する多結晶シリコン層14は、アクティブエリアAAの片脇に位置する素子分離膜の上面上に張り出す一端部14aと、アクティブエリアAAの逆脇に位置する素子分離膜の上面上に張り出す他端部14bとを備えており、一端部14aの長さL1と一端部14bの長さL2が互いに異なっている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】浮遊ゲート電極形成時に素子分離絶縁膜の側壁に残渣が発生しないようにする。

【解決手段】シリコン基板1に第1ゲート絶縁膜4、浮遊ゲート電極5用の導電層、加工用のシリコン窒化膜、シリコン酸化膜を形成し、この後トレンチ1aを形成する。続いて活性領域3に沿った導電層を分離する加工を行って浮遊ゲート電極5を形成する。この後、制御ゲート電極9を積層形成する。浮遊ゲート電極5を先に形成するので、エッチング残りを防止でき、しかも、制御ゲート電極9の加工時のアスペクト比を低減できる。また、加工用シリコン窒化膜を除去する際のリン酸処理で、浮遊ゲート電極5に凸状部5aを形成するので、カップリング比の向上も図れる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】2つの異なったゲート電極を有するトランジスタを備えた不揮発性半導体記憶装置およびその製造方を提供する。

【解決手段】半導体基板11の第1領域11aに第1ゲート絶縁膜14を介して形成された第1ゲート電極15、第2ゲート絶縁膜16、第2ゲート電極17を有するセルトランジスタと、第1ゲート電極15側へ突出した状態に埋め込まれた第1絶縁分離層12とを備えたメモリセルを形成する工程と、第2領域11bに第1ゲート絶縁膜14を介して形成され、高さL2が第1ゲート電極15の高さL3より大きい第1導電膜20と、高さL4が第2ゲート電極17の高さL5と等しい第2導電膜21とを有するゲート電極を備えたトランジスタと、高さL6が第1絶縁分離層12の高さL1より大きく第1導電膜20側へ突出した状態に埋め込まれた第2絶縁分離層13を形成する工程と、を具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】EOTを薄くしても低電界におけるリーク電流を抑制することができるとともに高電界におけるリーク電流を高くすることができるトンネル絶縁膜を有する不揮発性半導体記憶装置を得ることを可能にする。

【解決手段】半導体基板1と、半導体基板に離間して形成されたソース領域2aおよびドレイン領域2bと、ソース領域とドレイン領域との間の半導体基板上に形成され、母材と異なる元素が添加されることにより形成される、電子の捕獲および放出するサイトを有し、異なる誘電率の絶縁層8,9を含み、電子の捕獲および放出するサイトは半導体基板を構成する材料のフェルミレベルよりも高いレベルにある第1の絶縁膜3と、第1の絶縁膜上に形成された電荷蓄積膜4と、電荷蓄積膜上に形成された第2の絶縁膜5と、第2の絶縁膜上に形成された制御ゲート電極6と、を有する記憶素子を備えている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 不揮発性半導体記憶装置の書き込み特性を向上させることができる。また、不揮発性半導体記憶装置の隣接素子間の干渉を抑制することができる。

【解決手段】本発明の不揮発性半導体記憶装置は、半導体基板と、前記半導体基板の表面内に、チャネル領域を挟んで互いに離間して設けられたソース領域及びドレイン領域と、前記チャネル領域上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた絶縁性電荷蓄積層と、前記絶縁性電荷蓄積層上に設けられた両側部に絶縁層が設けられた導電性電荷蓄積層と、前記導電性電荷蓄積層上に設けられた層間絶縁膜と、前記層間絶縁膜上に設けられた制御ゲートとを備えている。

(もっと読む)

341 - 360 / 498

[ Back to top ]