Fターム[5F101BF09]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | リーク短絡防止 (498)

Fターム[5F101BF09]に分類される特許

261 - 280 / 498

半導体装置および半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置

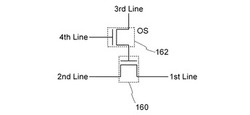

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成される。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、チャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、不純物領域と電気的に接続する第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の第2のゲート電極と、第2のゲート電極上の第2のゲート絶縁層と、第2のゲート絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続する第2のソース電極および第2のドレイン電極と、を有する第2のトランジスタと、を有する半導体装置である。

(もっと読む)

半導体装置

【課題】素子特性の劣化を可及的に防止することのできる半導体装置を提供する。

【解決手段】半導体基板51と、半導体基板上に設けられたゲート絶縁膜53と、ゲート絶縁膜上に設けられた第1ゲート電極54aと、第1ゲート電極上に設けられ金属および酸素を含む電極間絶縁膜55と、電極間絶縁膜上に設けられた第2ゲート電極54bと、第1および第2ゲート電極の両側の半導体基板に設けられたソース/ドレイン領域58a、58bと、を備え、電極間絶縁膜55は、リン、砒素、アンチモン、ビスマスのうちから選択された少なくとも1つの添加元素を含み、その含有量が0.1at%以上3at%以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】階段状に加工された複数の導電層と、各導電層に達し深さの異なる複数のコンタクトホールとの接続構造の信頼性を高めた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板10の第2のコンタクト領域5上に設けられ、第2のコンタクト領域5と第1のコンタクト領域4との間に段差を形成する下地層45bと、下地層45bを覆って基板10上に設けられ、下地層45b上に積層された上段部81が階段状に加工された下層側積層体91と、下層側積層体91における第1のコンタクト領域4上に積層された下段部82の上に設けられ、階段状に加工された上層側積層体92と、階段状に加工された部分を覆う層間絶縁層62と、層間絶縁層62を貫通し階段状に加工された部分の各々の導電層WLに達して形成されたコンタクトホール内に設けられたコンタクト電極51と、を備えた。

(もっと読む)

半導体メモリ装置

【課題】いわゆるMNOS構造において、ゲート絶縁膜を介した漏れ電流の発生を大幅に抑制させた半導体メモリ装置の提供。

【解決手段】ゲート絶縁膜は、半導体層側に半導体酸化膜、ゲート電極側に半導体窒化膜の積層膜からなる半導体メモリ装置であって、

横軸にゲート電圧をとり縦軸にドレイン電流をとったヒステリシス特性が、ゲート電圧を負側から正側への掃引によって得られる特性を第1特性とし、ゲート電圧を正側から負側への掃引によって得られる特性を第2特性とした場合、前記第1特性は、前記第2特性に対して、ゲート電圧が大きくなる側に位置づけられる特性となっている。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置100は、ビット線BLと、ソース線SLと、複数のメモリトランジスタMTrを直列に接続されたメモリストリングMSと、ドレイン側選択トランジスタSDTrと、ソース選択トランジスタSSTrと、読出動作を制御する制御回路15とを備える。制御回路15は、非選択メモリストリングMS(unselO1)、MS(unselO2)に接続されたドレイン選択トランジスタSDTr(unsel)、SDTr(unselMB)を導通状態とし、、非選択メモリストリングMS(unselO1)、MS(unselO2)に接続されたソース選択トランジスタSSTr(unsel)、SSTr(unselMB)を非導通状態とする。

(もっと読む)

電荷を非対称に捕獲する多値メモリセル

【課題】高メモリ密度、低電力消費、及び高信頼性を達成可能なNAND型多値メモリセルを提供する。

【解決手段】NAND型多値メモリセルは、2つのドレイン/ソース領域を基板に有する。2つのドレイン/ソース領域の間における基板の上方には、酸化物−窒化物−酸化物構造体が形成される。このうち窒化物層は、電荷を非対称に捕獲する層として機能する。酸化物−窒化物−酸化物構造体の上方には、制御ゲートが配置される。ドレイン/ソース領域に非対称のバイアスをかけることで、ドレイン/ソース領域に高い電圧が生じ、これによってドレイン/ソース領域の略近傍における電荷捕獲層にGIDL(ゲートに起因するドレインでの電流漏れ)正孔注入処理を行い、正孔を非対称な分布で注入する。

(もっと読む)

不揮発性半導体記憶装置

【課題】リーク電流を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングMSは、直列接続されたメモリトランジスタMTr1〜MTr8を含む。制御回路AR2は、メモリトランジスタMTr1〜8からデータを読み出す。メモリストリングMSは、メモリトランジスタMTr1〜8のボディとして機能するU字状半導体層34と、U字状半導体層34を取り囲むように形成され、電荷を蓄積することによりデータを保持する電荷蓄積層33bと、電荷蓄積層33bを介してU字状半導体層34を取り囲むワード線導電層31a〜31dとを備える。制御回路AR2は、読み出し動作の際、非選択メモリストリングMSの中の少なくとも一つのメモリトランジスタMTr1〜MTr8のゲートに読み出しパス電圧Vreadを印加し、別のメモリトランジスタMTrのゲートには接地電位Vssを印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積の増大を抑制しつつ、不良ブロックの非選択処理が可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリマット10〜60を含むメモリアレイをコの字型に配置し、メモリアレイが配置されていない空き領域にロジック回路92およびアナログ回路91を配置している。これにより、アナログ回路91およびロジック回路92などの周辺回路と電源パッド101およびデータパッド100などのパッド帯との間で電源電圧および信号のやりとりが容易となる。また、アナログ回路91については電源パッド101に近くなるため、電源配線抵抗による電圧降下を抑制でき、かつ電源パッド101付近でチャージポンプ用電源配線102と周辺回路用電源配線103とを分離することが可能となる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】ワードゲートとコントロールゲートの間の高低差を大きくすることなく、シリサイドショートを防止することが可能な不揮発性半導体記憶装置、及びその製造方法を提供すること。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、半導体基板1上にゲート絶縁膜2を介して形成され、一定の幅を有する部分が上に突出した突出部3bが設けられているワードゲート3と、ワードゲート3の側壁面にONO膜4を介して設けられたコントロールゲート5と、コントロールゲート5の側壁面と、ワードゲート3の突出部3bの側壁面とに形成された絶縁性のサイドウォール7と、ワードゲート3の突出部3bの上面と、コントロールゲート5の表面の一部とに形成されたシリサイド層9と、を備え、突出部3bの幅は、突出部3bよりも下側の部分のワードゲート3の幅よりも狭いものである。

(もっと読む)

絶縁膜およびその製造方法、半導体装置、ならびにデータ処理システム

【課題】誘電率が大きく、電極間に挟んで用いてもリーク電流値の小さい絶縁膜を提供する。

【解決手段】結晶化した酸化ジルコニウムからなる酸化ジルコニウム膜の2つと、非晶質であって、前記結晶化した酸化ジルコニウムよりも大きい誘電率を有する材料からなる結晶粒界分断膜とを有し、前記結晶粒界分断膜が、前記2つの酸化ジルコニウム膜に挟まれている絶縁膜を形成する。例えば、上部電極と下部電極の間に容量絶縁膜を有するキャパシタ素子で構成されたメモリセルを備える半導体装置における容量絶縁膜や、コントロールゲート電極とフローティングゲート電極の間にインターゲート絶縁膜を有する不揮発性メモリ素子を備えた半導体装置におけるインターゲート絶縁膜として好適である。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】階段部に欠陥を生じさせることなく歩留まりを向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリ領域AR1及び周辺領域AR2に亘って積層されたワード線導電層41a〜41dと、メモリ領域AR1にてワード線導電層41a〜41dに取り囲まれ、基板に対して垂直方向に延びる柱状部45Aを含むU字状半導体層45と、柱状部45Aの側面とワード線導電層41a〜41dとの間に形成されたメモリゲート絶縁層44とを備える。ワード線導電層41a〜41dは、メモリ領域AR1にてカラム方向に第1ピッチP1をもって配列されて、ロウ方向を長手方向とするストライプ状に形成された溝T1B、周辺領域AR2にてカラムに第2ピッチP2をもって配列されて、ロウ方向を長手方向とするストライプ状に形成された溝T2を備える。

(もっと読む)

不揮発性メモリセル及びその製造方法

【課題】同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備える透明不揮発性メモリセル及びその製造方法を提供する。

【解決手段】本発明による不揮発性メモリセルは、基板上に形成された半導体膜、バッファー膜、有機強誘電体膜及びゲート電極を含むメモリトランジスタと;前記基板上に形成された前記半導体膜、前記バッファー膜、ゲート絶縁膜及び前記ゲート電極を含む駆動トランジスタと;を備える。本発明によれば、同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備え、可視光領域で透明な不揮発性メモリセルを提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】浮遊ゲート電極を有するメモリセルの高集積化を実現する半導体装置の製造方法を提供する。

【解決手段】半導体層11の表面にトンネル絶縁膜12を介してシリコンを含む第1の導電体層を形成する工程と、第1の導電体層の表面から半導体層11に至る分離溝9を形成し、第1の導電体層が所定幅で分離された、浮遊ゲート電極となる複数の導電板13bを形成する工程と、導電板13b側面の中間部まで、分離溝9を素子間絶縁膜15で埋め込む工程と、複数の導電板13bの間隔を所定幅と同等以上の幅に維持しながら、導電板13bの露出面にシリコン窒化膜16aを形成する工程と、制御ゲート電極19aとなる第2の導電体層を形成して分離溝9の上部を埋め込む工程と、を備え、シリコン窒化膜16aは、窒素元素を含む原料ガスを励起させて生成する窒素ラジカルによって、導電板13bに含まれるシリコンを窒化して形成される。

(もっと読む)

半導体装置

【課題】MONOS型不揮発性メモリの信頼性を向上させる。

【解決手段】メモリセルは、選択ゲート6とその一方の側面に配置されたメモリゲート8とを有している。メモリゲート8は、一部が選択ゲート6の一方の側面に形成され、他部がメモリゲート8の下部に形成されたONO膜7を介して選択ゲート6およびp型ウエル2と電気的に分離されている。選択ゲート6の側面にはサイドウォール状の酸化シリコン膜12が形成されており、メモリゲートの側面にはサイドウォール状の酸化シリコン膜9と酸化シリコン膜12とが形成されている。メモリゲート8の下部に形成されたONO膜7は、酸化シリコン膜9の下部で終端し、酸化シリコン膜12の堆積時にメモリゲート8の端部近傍の酸化シリコン膜12中に低破壊耐圧領域が生じるのを防いでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルアレイ領域と周辺回路領域との間に生じる層間絶縁膜の段差を解消し、歩留まりの向上を図ることができる半導体装置を提供すること。

【解決手段】半導体基板1上で素子分離用絶縁膜2a、2bによって素子分離された複数の第1の素子10が形成された第1の領域4と、半導体基板1上で第1の領域4に隣接して配されるとともに、素子分離用絶縁膜2b、2cによって素子分離された複数の第2の素子20が形成され、第2の素子20の高さが第1の素子10の高さよりも低い第2の領域5と、第2の領域5にある素子分離用絶縁膜2b、2cの少なくとも一部の領域上に配設されたダミー絶縁膜6c、6dと、第1の領域4及び第2の領域5にわたって形成された層間絶縁膜7と、を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】セルトランジスタの微細化に適した構造の選択トランジスタを有するNAND型不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、基板101と、基板内に形成された拡散層121により互いに直列接続されている複数のセルトランジスタ141と、複数のセルトランジスタ141と直列接続されている選択トランジスタ142とを備え、選択トランジスタ142は、第1の絶縁膜161と、第1の電極層162A、B、第2の絶縁膜163A,B、及び第2の電極層164A,Bを含む第1及び第2の積層体171A,Bと、第1の積層体と第2の積層体との間に形成され、第1の積層体171Aの第1及び第2の電極層と第2の積層体171Bの第1及び第2の電極層とを電気的に接続する第3の電極層181とを備え、第3の電極層181は、第1及び第2の積層体171A,Bの上面よりも上方に突出した突出部191を有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリコンをエピタキシャル成長させて得られた単結晶シリコン層の結晶欠陥の部分にメモリセルを形成することなくメモリセルの積層を実現する不揮発性半導体記憶装置を提供する。

【解決手段】層間絶縁膜16上にシリコンをエピタキシャル成長させて得られた単結晶シリコン層200、204の結晶欠陥26bの部分にソース線コンタクトホールを形成する。これによって、結晶欠陥26bの部分に、接合リークにより特性の劣化したメモリセルを形成することなく、メモリセルを二層以上積層することができる。

(もっと読む)

半導体装置の製造方法

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部20の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

261 - 280 / 498

[ Back to top ]