Fターム[5F101BF09]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | リーク短絡防止 (498)

Fターム[5F101BF09]に分類される特許

221 - 240 / 498

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極(またはドレイン電極)と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタとして、しきい値電圧を正に制御したトランジスタを用いることで、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、前記ゲート電極と一部が重畳するように第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上にサイドウォール絶縁層を有し、サイドウォール絶縁層は異なる複数の材料層が積層される半導体装置である。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法および半導体装置の作製方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースを書き込みビット線に、読み出しトランジスタのソースとドレインとを、それぞれ、読み出しビット線及びバイアス線に接続する。さらに、キャパシタの他方の電極を読み出しワード線に接続する。配線数を減らすために、読み出しビット線を書き込みビット線で代用する。そして、読み出しビット線を、基板上に形成された溝状の開口部に埋め込むように形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】過消去ビットの発生を抑制してエンデュランス特性等を向上させることができる不揮発性記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え及び消去可能な複数の不揮発性メモリーセルM11〜M44を有するメモリーセルアレイと、複数の不揮発性メモリーセルのうちの消去対象メモリーセルに対する消去動作の制御を行う消去制御回路ERCNとを含む。消去制御回路ERCNは、消去対象メモリーセルが多い場合には、消去対象メモリーセルに対応するビット線BL1〜BL4がフローティング状態に設定される第1の消去動作制御を行う。消去対象メモリーセルが少ない場合には、消去対象メモリーセルに対応するビット線BL1〜BL4が低電位電源電圧VSSに設定される第2の消去動作制御を行う。

(もっと読む)

半導体装置

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタは、半導体特性を示す金属酸化物により設けられ、下部のトランジスタが有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、該ゲート電極層と同一の層の一部を上部のトランジスタのバックゲートとして機能させる。下部のトランジスタは、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタのソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位変換回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタと、酸化物半導体以外の半導体材料を用いたトランジスタとを積層して、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第1のトランジスタ上に絶縁層と、絶縁層上に第2のトランジスタと、を有し、第1のトランジスタは、第1のチャネル形成領域を含み、第2のトランジスタは、第2のチャネル形成領域を含み、第1のチャネル形成領域は、第2のチャネル形成領域と異なる半導体材料を含んで構成され、絶縁層は、二乗平均平方根粗さが1nm以下の表面を有する半導体装置。

(もっと読む)

フラッシュメモリの製造方法

【課題】フラッシュメモリの製造工程において、エッチングによるSTI膜の膜減りを抑制することができる製造方法と、それを可能にするスプリットゲートタイプのMONOS型フラシュメモリ構造を提供する。

【解決手段】ワードゲートとコントロールゲートを含むスプリットゲートタイプのMONOS型フラシュメモリの製造方法であって、STIによって分離された半導体基板の不純物拡散層上に、酸化膜を挟んだワードゲートを形成する工程と、該STIとワードゲートが形成された半導体基板の表面全体に酸化膜、窒化膜、酸化膜の順に成膜されるONO層を形成する工程と、該ONO層の上にコントロールゲート用導電膜(10)を形成する工程と、該コントロールゲート用導電膜の表面全体にマスク用絶縁膜(26)を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】シリコン含有膜の露出面に形成する酸化膜中や、既に基板上に成膜済みの誘電膜中等に水素が混入することを抑制させ、半導体装置の性能を向上させる。

【解決手段】 水素ガスより分子サイズの大きい還元性ガスを処理室内に供給し、処理室内に供給された還元性ガスをプラズマ放電して生成した還元性ガスプラズマを基板の表面に供給する還元工程と、酸化性ガスを処理室内に供給し、処理室内に供給された酸化性ガスをプラズマ放電して生成した酸化性ガスプラズマを基板の表面に供給する酸化工程と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高効率的に書き込みを行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】直列接続された複数のメモリセルトランジスタMTと、メモリセルトランジスタの一端とソース線との間に接続された選択ゲートトランジスタST2と、メモリセルトランジスタの他端とビット線との間に接続された選択ゲートトランジスタST1と、ソース線に第1の電圧を印加し、ビット線に第1の電圧よりも高く且つ第1の電圧との差がトンネル絶縁膜のバリアハイトに対応する電圧よりも小さい第2の電圧を印加し、書き込み対象のメモリセルトランジスタMTとソース線との間に位置し、且つ書き込み対象のメモリセルトランジスタに隣接する隣接メモリセルトランジスタMTの導通状態を、他のメモリセルトランジスタMTの導通状態よりも弱くすることで書き込み対象のメモリセルトランジスタに書き込みを行う制御回路と、を具備する。

(もっと読む)

半導体装置及び電子機器

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置法を提供する。

【解決手段】メモリストリングは、垂直方向に延びるメモリ柱状半導体層と、メモリ柱状半導体層の側面を取り囲む電荷蓄積層と、電荷蓄積層を取り囲む複数層のワード線導電層とを備える。制御回路は、ワード線導電層と同層に形成された導電層と、導電層71a〜71dを垂直方向に貫通するように形成された層間絶縁層56Aと、1つの層間絶縁層56Aを垂直方向に貫通するように形成された2つのプラグ層53eとを備える。層間絶縁層56Aは、水平方向において2つの括れA1をもつ長方形状の断面B1を有する。括れA1は、断面B1の長辺に位置する。

(もっと読む)

半導体装置

【課題】デプレッション型トランジスタを用いて構成される記憶素子を有する半導体装置であっても、正確な情報の保持を可能にすること。

【解決手段】あらかじめ信号保持部への信号の入力を制御するトランジスタのゲート端子に負に帯電させ、且つ電源との接続を物理的に遮断することにより負電荷を保持させる。加えて、一方の端子が当該トランジスタのゲート端子に電気的に接続される容量素子を設け、当該容量素子を介して当該トランジスタのスイッチングを制御する。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体装置と不揮発性半導体記憶装置

【課題】キャパシタのコンタクトプラグ形成に伴うショート不良を低減させることができ、素子信頼性の向上をはかる。

【解決手段】半導体装置であって、半導体基板10上に、第1の絶縁膜21,第1の導電層22,第2の絶縁膜23,及び第2の導電層24が積層され、且つ導電層22,24の一部が接続された積層構造部と、導電層22を接続部を含む第1の領域と接続部を含まない第2の領域に分離する層間絶縁膜26と、第2の領域の一周辺部で、導電層21,絶縁膜22,及び基板10に形成された素子分離溝に埋め込まれた素子分離絶縁膜15と、第1の領域に接続された第1のコンタクトプラグ31と、第2の領域に接続され且つ素子分離絶縁膜15の上方に形成された第2のコンタクトプラグ32と、第2の領域側の一周辺部に隣接する領域で基板10に接続された第3のコンタクトプラグ33を備えた。

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジスタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導体記憶装置である。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置

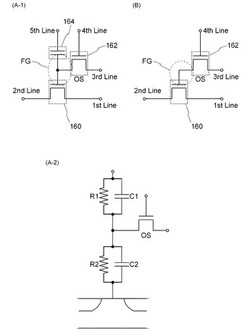

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】オフ状態のソースとドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースを書き込みビット線に、読み出しトランジスタのソースとドレインとを、それぞれ、読み出しビット線及びバイアス線に接続する。さらに、キャパシタの他方の電極を読み出しワード線に接続する。配線数を減らすために、読み出しビット線を書き込みビット線や他の列のバイアス線で代用する。

(もっと読む)

221 - 240 / 498

[ Back to top ]