Fターム[5F101BF09]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 寄生 (642) | リーク短絡防止 (498)

Fターム[5F101BF09]に分類される特許

241 - 260 / 498

不揮発性フラッシュメモリ

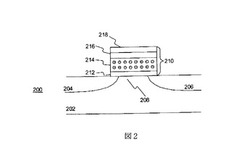

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルアレイ端部の耐圧を向上させる。

【解決手段】不揮発性半導体記憶装置10は、メモリセルトランジスタが配置される第1の領域と、メモリセルトランジスタに電気的に接続されたワード線を引き出す電極21が配置される第2の領域と、周辺トランジスタが配置される第3の領域とを有する。第1の領域には、第1の幅を有する複数の第1のアクティブ領域AA1が設けられ、第2及び第3の領域にはそれぞれ、第1の幅より広い第2の幅を有する複数の第2及び第3のアクティブ領域AA3,AA5が設けられる。第2の領域の素子分離層23Bの上面は、第1の領域の素子分離層23Aの上面より高く、第2の領域の電荷蓄積層32Bは、上部の角の曲率半径が、第3の領域の電荷蓄積層43よりも大きい。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体OSを用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ162、書き込み用トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルを有する半導体装置において、メモリセルへの情報の書き込みは、書き込み用トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードFGに電位を供給し、ノードFGに所定量の電荷を保持させることで行う。書き込みを1×109回行う前後において、メモリセルのメモリウィンドウ幅の変化量は2%以内である。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】高速処理が可能で、かつ電荷保持特性の高いチャージトラップ型フラッシュメモリを得ることができる半導体装置の製造方法を提供する。

【解決手段】基板100の表面を酸化してシリコン酸化膜140を形成するシリコン酸化膜形成工程と、プラズマ状態の窒素含有ガスをシリコン酸化膜140に供給してシリコン酸化膜140の表面近傍に窒素ピーク濃度が20原子%以上60原子%以下の窒化層141を形成する窒化層形成工程と、窒化層141が形成されたシリコン酸化膜140上に電荷保持膜150を形成する電荷保持膜形成工程と、電荷保持膜150上に、絶縁膜160と電極膜170を形成する電極膜形成工程とを有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ、該書き込み用トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。該メモリセルへの情報の書き込み及び書き換えは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給し、その後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。

(もっと読む)

半導体装置

【課題】チップ面積を縮小しつつ、高信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置は、第1、第2配線S1,S2を有する第1回路部210と、第3、第4配線S3、S4を有する第2回路部220と、それらの間に設けられ、第1回路部210から第2回路部220に向かう方向に直交する方向に沿って隣接する第1、第2トランジスタTR1、TR2を有する中間部230と、を備え、第1トランジスタTR1の一方の拡散層DA1の第1接続領CA1内の高濃度領域CAI1は第1配線S1に、他方の拡散層DB1は第3配線S3に接続される。第1接続領域CA1とゲートG01との距離は、第2接続領域CA2とゲートG02との距離よりも長い。第1トランジスタTR1の一方の拡散層DA1の第1接続領域CA1とゲートG01との間には、第1接続領域CA1よりも幅が狭い延在領域EA1が設けられる。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことにより、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】

本発明は、コンタクトホールのアスペクト比の低減可能な半導体記憶装置及びその製造

方法を提供する。

【解決手段】

半導体基板11a上に形成された所定の間隔を隔てて設けられ、直列接続された複数の

メモリセルトランジスタM、複数の前記メモリセルトランジスタMの両端に形成された選

択ゲートトランジスタTを有する複数のNANDストリングと、隣接する前記NANDス

トリングの前記選択ゲートトランジスタT間に設けられたコンタクトプラグ18とを備え

、隣接する前記選択ゲートトランジスタT間の第1の方向における幅が前記メモリセルト

ランジスタMの前記ゲート長のk倍(kは自然数)と前記所定の間隔の(k+1)倍の総

和と等しい場合には、第1の方向における前記コンタクトプラグ18の幅は、前記メモリ

セルトランジスタMの前記ゲート長のk倍と前記所定の間隔の(k−1)倍の総和よりも

長いことを特徴とする半導体記憶装置。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

不揮発性メモリ

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数の絶縁膜及び電極膜が交互に積層された信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、メモリアレイ領域にメモリ積層体を設け、周辺回路領域にダミー積層体を設け、ダミー積層体にダミーホール31a,31bを形成し、その内部に絶縁部材を埋め込む。そして、絶縁部材内に複数本のコンタクト35a,35b,35c,35d,35eを形成する。コンタクト35a,35bはMOSFET40のソース層36に、コンタクト35c,35dはドレイン層37に、コンタクト35eはゲート電極38に接続される。そして、1つのダミーホール内に配置された複数本のコンタクトは、同じ電位が印加されるコンタクトとするか、ダミーホールの長手方向に延びる中心線41a,41c、41d、41f、41h、41j、41k、41lから外れた位置に配置する。

(もっと読む)

記憶装置

【課題】ロジック回路を増やすことなく、第三者がメモリセルにアクセスできずかつ必要な場合にはいつでもアクセス可能なメモリセルを有する記憶装置を提供する。

【解決手段】本実施形態は、第1のメモリセルと、第2のメモリセルと、を有し、第2のメモリセルに設けられた第2のトランジスタの第2のチャネルが酸化物半導体膜からなる記憶装置であって、第2のメモリセルからのデータの読み出しは第2のトランジスタに紫外線を照射している時に行われる記憶装置によって解決する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置

【課題】ワードラインとビットラインのショートを防止することができる半導体装置を提供する。

【解決手段】半導体装置は、メモリセルアレイ部MCA及びメモリセルアレイ部MCAの外周に位置するメモリセルアレイ外側部EMCAからなり、メモリセルアレイ部MCAがメモリセルアレイ外側部EMCAに近接する最外周領域を有する半導体基板と、その上の中間絶縁膜上において1段目のコンタクト部CT1の群のダミーコンタクトプラグDCT1の上方に延在するとともに2段目のコンタクト部の群の第2コンタクト部CT2と接続し、メモリセルアレイ部MCAから最外周領域を越えメモリセルアレイ外側部EMCAまで延在するビットラインBLと、を有する。

(もっと読む)

241 - 260 / 498

[ Back to top ]