Fターム[5F101BG09]の内容

不揮発性半導体メモリ (42,765) | 応用 (153) | 揮発性メモリのバックアップ (15)

Fターム[5F101BG09]に分類される特許

1 - 15 / 15

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

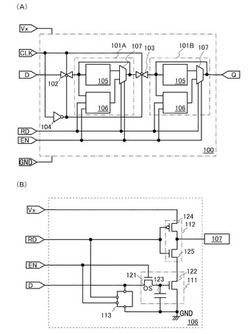

ラッチ回路及び半導体装置

【課題】新規のラッチ回路を提供すること。

【解決手段】ラッチ回路は、酸化物半導体(OS)によってチャネル領域が形成されるトランジスタ10を有し、出力端子(Q端子)並びにトランジスタ10のソース及びドレインの一方に電気的に接続され、且つトランジスタ10がオフ状態となることによって浮遊状態となるノード11においてデータを保持する。なお、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

インサイチュでのメモリのアニール

メモリデバイスを有するシステムにおいて、あるイベントがシステム操作中に検出される。メモリデバイスは、そのイベントの検出に応じて、メモリデバイスの使用に起因する劣化を反転させるために加熱される。別のシステムにおいて、メモリデバイスは、そのシステムの別のメモリデバイス内でのデータアクセス操作と同時に使用に起因する劣化を回復させるために加熱される。第1および第2のメモリデバイスと連結されたメモリコントローラを有する別のシステムにおいては、データは、メンテナンス操作が第1のメモリデバイス内において必要であると決定することに応じて、第1のメモリデバイスから第2のメモリデバイスに退避される。 (もっと読む)

半導体集積回路装置

【課題】ラッチ型メモリセルのラッチ部のサイズを増大させることなく、データ保持特性を改善する。

【解決手段】ラッチ型メモリセルの記憶ノードを構成するゲート電極配線(21a,21c)と交差する方向に、フラッシュメモリセルトランジスタの固有の配線と同一配線層の導電線(26a,26b)を連続的に延在させて配置する。ゲート電極配線と導電線の交差部において容量を形成し、導電線を固定電位に維持する。

(もっと読む)

不揮発性磁気メモリを使用している低電力電子システム

コンピューティングシステムが少なくとも1つの機能的ユニット及び少なくとも1つの機能的ユニットに接続された磁気ランダムアクセスメモリ(MRAM)ブロックを含む。MRAMブロックは少なくとも1つの機能的ユニットのパワーダウン状態の間、少なくとも1つの機能的ユニットの機能的状態を格納するように構成される。  (もっと読む)

(もっと読む)

フローティングゲートを有する不揮発性DRAM及び動作方法

【課題】電力停止の場合にDRAMセルの状態を記憶し、電力投入又は電力回復の場合にゲートからDRAMセル上にこの状態を回復するフローティングゲートを有するDRAMセルを提供する。

【解決手段】表面を備えた第1の導電型の半導体基板を有するコンデンサを用いない不揮発性の1T-DRAM。基板の表面上には、第2導電型の第1領域が存在する。基板の表面上には、第1領域から離間して、第2導電型の第2領域が存在する。基板の第1領域と第2領域との間には、第1導電型の本体領域が存在する。本体領域は、この表面と、1又はそれ以上の絶縁領域と、第1及び第2の領域とによって、境界が形成される。DRAMは、更に、この表面から絶縁されて第1領域と第2領域との間に位置決めされたフローティングゲートを有する。フローティングゲートには、制御ゲートが容量的に結合されている。

(もっと読む)

不揮発性メモリ用素子及び不揮発性メモリ並びに不揮発性メモリ内蔵シフトレジスタ

【課題】標準的なCMOSICの製造工程で電気的な書換えが可能な不揮発性メモリの形成が可能となり、集積回路の調整用等として汎用性に優れる不揮発性メモリ用素子を提供する。

【解決手段】浮遊ゲートFGをそれぞれ具備するPMOSトランジスタTr1、PMOSトランジスタTr2及びNMOSトランジスタTr3を形成するとともに、PMOSトランジスタTr1とPMOSトランジスタTr2とを互いに分離されたウェル上に形成した。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の状態決定方法および半導体集積回路装置

【課題】読み出しマージンを大きくとることができ、且つ、ワード線,ビット線の制御をVccレベルで行うことができる書き換え可能な不揮発性メモリセルを提供する。

【解決手段】記憶トランジスタ(nMOSトランジスタ)をサイドスペーサに電荷を注入することによりしきい値を制御可能なトランジスタで構成したインバータをクロス接続してフリップフロップを構成する。一方の記憶トランジスタに書き込みを行うときは、ソース線を介して記憶トランジスタのソースに高電圧を供給するとともに、反対側のインバータの負荷トランジスタを介して記憶トランジスタのゲートに高電圧を供給する。この書き込みを消去するときは、ソース線を介して記憶トランジスタのソースに高電圧を供給する。

(もっと読む)

集積されたDRAM−NVRAM多値メモリ

【課題】集積されたDRAM−NVRAMメモリセルを提供する。

【解決手段】集積されたDRAM−NVRAM(170、171)すなわち多値メモリセルは、共有される縦型ゲート(120)と浮遊プレート(115、116)を有するデバイスを含む縦型DRAMデバイスで構成される。浮遊プレート(115、116)デバイスは、2つの機能の間の柱状部にある共有された浮遊ボディによって、セルのDRAM部(104、130、101、105、131)の電荷記憶特性を高める。このメモリセルは、柱状部を構成するトレンチを有する基板(100)に形成される。セルのDRAM部(104、130、101、105、131、103)を制御するために、柱状部の一方の側面の縦型ワード線/ゲート(131、130)が用いられる。柱状部の他方の側面の縦型捕獲層(115、116)は、浮遊プレートデバイスの一部として、1以上の電荷を記憶し、またDRAMと浮遊プレートデバイスとの間の浮遊ボディを通じてDRAM機能の特性を高める。縦型NVRAMワード線/制御ゲート(120)は、捕獲層に沿って形成され、近傍の浮遊プレートデバイス(115、116)に共有される。

(もっと読む)

デュアルゲート誘電体構造を有する半導体素子の製造方法

【課題】ラジカル酸化(Radical Oxidation)によるデュアルゲート誘電体構造を有する半導体素子の製造方法を提供することを目的とする。

【解決方法】半導体基板上に絶縁膜を形成する工程と、該絶縁膜上に窒化膜を形成する工程と、所定領域の前記窒化膜を選択的にエッチングする工程と、前記エッチングされた窒化膜を含む全体構造上に酸化膜が形成されるようにラジカル酸化を実施する工程と、前記酸化膜上にゲート導電膜を形成する工程と、該ゲート導電膜と、前記酸化膜と、前記窒化膜、及び前記絶縁膜を選択的にエッチングする工程とを含み、前記所定領域に前記絶縁膜及び前記酸化膜が積層されて第1ゲート誘電体構造を形成し、前記所定領域以外の領域に前記絶縁膜、前記窒化膜、及び前記酸化膜が積層されて第2ゲート誘電体構造を形成する構成とした。

(もっと読む)

1 - 15 / 15

[ Back to top ]