Fターム[5F101BH15]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | エッチング (993) | ウェットエッチング(異方性エッチング) (424)

Fターム[5F101BH15]に分類される特許

1 - 20 / 424

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性の均一化を図る。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に設けられた積層体と、絶縁膜と、チャネルボディと、半導体層とを備えている。前記積層体は、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する。前記絶縁膜は、前記積層体を積層方向に貫通して形成されたホールの側壁に設けられている。前記チャネルボディは、前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲む。前記半導体層は、前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれている。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域、第1電極、及び第2電極を有する。メモリセル領域は、基板上に形成され、複数のメモリセルが積層される。第1電極は、基板上に複数の導電層が積層されて、容量素子の一方の電極として機能する。第2電極は、基板上に複数の導電層が積層されて、第1電極と基板に水平な方向において分離され、容量素子の他方の電極として機能する。

(もっと読む)

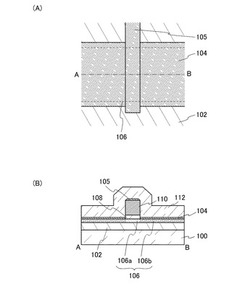

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリストリングと他の配線との電気的接続を容易にする不揮発性半導体記憶装置を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置は、複数のメモリストリングを備え、複数のメモリストリングのうちの1つのメモリストリングのチャネルボディ層の上端と、このメモリストリングとは他のメモリストリングのチャネルボディ層の上端と、に電気的に接続された電極パッドを備える。1つのメモリストリングのチャネルボディ層と、他のメモリストリングのチャネルボディ層と、は隣り合っている。

(もっと読む)

半導体装置の製造方法

【課題】デバイス特性の向上を図る。

【解決手段】本実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法においては、半導体層10上に、トンネル絶縁膜11を形成する。トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜12を形成する。第1導電膜、トンネル絶縁膜、および半導体層を加工することにより、溝15を形成する。溝内の下部側に、第1犠牲膜17を埋め込む。溝内の第1犠牲膜上に、その上面がトンネル絶縁膜の上面よりも高く、第1導電膜の上面よりも低くなるように、第1犠牲膜よりも高密度な第2犠牲膜18を形成する。第1導電膜上および第2犠牲膜上に、絶縁膜19を形成する。絶縁膜上に制御ゲート電極となる第2導電膜WLを形成する。第2導電膜を加工することにより、第2犠牲膜を露出する。第1犠牲膜および第2犠牲膜を除去する。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置を提供する。

【解決手段】基板上に、第1積層体及び第2積層体を形成する工程と、第1積層体及び第2積層体を貫通する貫通孔を形成する工程と、貫通孔の第1部分の側壁にメモリ膜を形成し、貫通孔の第2部分及び第3部分の側壁にゲート絶縁膜を形成し、メモリ膜及びゲート絶縁膜の内側にチャネルボディを形成する工程と、チャネルボディの内側に酸化シリコンを含む第3絶縁層を形成し、第2部分と第3部分との境界部分を第3絶縁層により閉塞する工程と、第3部分の内側にシリコンを含む第1埋め込み部を形成する工程と、第1埋め込み部の一部と第3絶縁層の一部とを除去してチャネルボディを露出させる工程と、第3部分の内側における第1埋め込み部の上に、第1埋め込み部よりも不純物濃度が高いシリコンを含む第2埋め込み部を埋め込む工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】不純物添加シリコン層に添加された不純物が不純物無添加シリコン層に拡散するのを抑制する。

【解決手段】セレクトゲート電極SG1上にはワード線WL1が積層され、最上層のワード線WL1上にはセレクトゲート電極SG2がロウごとに形成されることで、NANDセルNC1が構成され、セレクトゲート電極SG1、SG2およびワード線WL1は、不純物添加シリコン層2と層間絶縁膜とを拡散防止層3を介して交互に積層することで構成し、ワード線WL1は、拡散防止層3にて挟まれた不純物添加シリコン層2にて構成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性および読み出し速度の向上を図ることができる半導体記憶装置及びその製造方法を提供する。

【解決手段】電極膜WLと層間絶縁膜14を交互に複数積層して積層体を形成する工程と、前記積層体の積層方向に延びる複数の貫通孔18を形成する工程と、前記貫通孔の内部に電荷蓄積膜23と、絶縁膜24aと、ゲルマニウムを用いた第1の膜25と、アルミニウムを用いた第2の膜27を形成する工程と、置換熱処理で、前記第1の膜と前記第2の膜を置換し前記第2の膜の前記絶縁膜とは反対の側にゲルマニウムを成長させて半導体ピラーSPを形成する工程と、前記積層体の上方に配線を形成する工程と、前記置換された第2の膜を選択的に除去することで、前記絶縁膜と前記半導体ピラーとの間に空隙24bを形成する工程と、を備えている。前記半導体ピラーの上端部は、前記積層体の上方に形成された前記配線により支えられる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高電界リークを低減して、書き込み特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。そして、前記電極間絶縁膜は、シリコン窒化膜もしくは高誘電率膜を2層のシリコン酸化膜で挟んだ積層構造または高誘電率膜とシリコン酸化膜の積層構造及び前記積層構造と前記制御電極層の間に形成された第2のシリコン窒化膜を有し、前記第2のシリコン窒化膜のうちの前記電荷蓄積層の上面上の部分を消失させた。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の加工精度をより向上させる。

【解決手段】実施形態によれば、不純物含有領域と、被エッチング領域と、を有する半導体層を形成し、それぞれの表面から内部にかけて第1絶縁層を形成し、第1絶縁膜を介して、半導体層上に複数の電極層を含む積層体を形成し、積層体に、被エッチング領域に達し第2絶縁層を挟む一対のホールを形成し、被エッチング領域を一対のホールを通じて除去し、半導体層に一対のホールのそれぞれの下端とつながった空間部を形成し、一対のホールのそれぞれの側壁に、メモリ膜を形成し、空間部の内壁に第4絶縁層を形成し、一対のホールのそれぞれの側壁と空間部の内壁とに形成されたメモリ膜の表面に、チャネルボディ層を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、コントロールゲートとフローティングゲートとの間のカップリング容量比を増大させることができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。第1の絶縁膜は、半導体基板上に形成されている。フローティングゲートは、第1の絶縁膜上に設けられた第1のフローティングゲート部分、第1のフローティングゲート部分上に設けられた中間絶縁膜、および、中間絶縁膜上に設けられた第2のフローティングゲート部分を含み、電荷を蓄積可能に構成されている。第2の絶縁膜は、フローティングゲートの上面および側面に設けられている。コントロールゲートは、第2の絶縁膜を介してフローティングゲートの上面および側面に対向し、フローティングゲートの電圧を制御する。フローティングゲートの側面において中間絶縁膜が第1および第2のフローティングゲート部分に対して窪んでいる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】隣接セルの書き込み閾値の変動を抑制すると共に、制御ゲート電極膜とシリコン基板との間のリーク電流を低減して消去特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。前記電極間絶縁膜は、第1のシリコン酸化膜、第1のシリコン窒化膜、第2のシリコン酸化膜および第2のシリコン窒化膜を積層形成した積層構造を有する。そして、前記電極間絶縁膜は、前記第2のシリコン酸化膜のうちの前記素子分離絶縁膜の上面上の部分の膜厚が前記電荷蓄積層の上面上の部分の膜厚より薄くなるように構成した。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】寄生抵抗がより低いチャネルボディ層を有する不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置は、半導体層と、第1絶縁層が表面に設けられた第2絶縁層と、第3絶縁層と、第2絶縁層および第3絶縁層の上に、電極層と絶縁膜とを有する第1積層体と、第1積層体の積層方向に貫通し第2絶縁層に達する一対の第1ホールのそれぞれの側壁に設けられたメモリ膜と、メモリ膜の内側に設けられた第1チャネルボディ層と、層間絶縁膜と選択ゲートとを有する第2積層体と、一対の第1ホールのそれぞれ上端と連通し、第2積層体の積層方向に貫通する第2ホールの側壁に設けられたゲート絶縁膜と、ゲート絶縁膜の内側に設けられた第2チャネルボディ層と、第1積層体の下側に設けられた連結部と、一対の第1ホールの間に挟まれ、第1積層体の表面から第1絶縁層に達する第4絶縁層と、を備える。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離絶縁膜の形成時に、浮遊ゲート電極膜の基板に対面する部分の幅寸法が細くなってしまうことを防止する。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、浮遊ゲート電極膜、電極間絶縁膜および制御ゲート電極膜が積層されたゲート電極とを備えた。そして、前記浮遊ゲート電極膜を、窒素を含む下層シリコン層と窒素を実質的に含まない上層シリコン層とを有する多結晶シリコン層で構成し、前記下層シリコン層のゲート幅方向の寸法を、前記上層シリコン層のゲート幅方向の寸法よりも大きく構成した。

(もっと読む)

半導体記憶装置の製造方法

【課題】スループットの向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板上に、不純物濃度が第1濃度である第1シリコン層35、不純物濃度が第1濃度より低い第2濃度である第1犠牲層、不純物濃度が第1濃度である第2シリコン層35、および不純物濃度が第2濃度である第2犠牲層が順に積層された積層体を形成する工程と、積層体上に、第1絶縁膜を形成する工程と、積層体および第1絶縁膜内に、溝22を形成する工程と、溝内に、不純物濃度が第1濃度より低く、第2濃度より高い第3濃度である第3犠牲層90を埋め込む工程と、ウェットエッチングにより、溝内の第3犠牲層を上面から後退させて除去することで、第1犠牲層および第2犠牲層の端面を後退させる工程と、第1シリコン層および第2シリコン層の端面を第1犠牲層および第2犠牲層の端面に沿ってエッチングする工程とを具備する。

(もっと読む)

1 - 20 / 424

[ Back to top ]