Fターム[5F102FA01]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | 高耐圧化 (602)

Fターム[5F102FA01]に分類される特許

201 - 220 / 602

電界効果トランジスタ

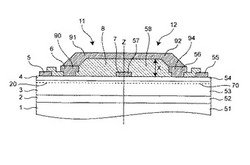

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

窒化物半導体装置

【課題】高電圧印加時にフィールドプレート構造端に集中する電界強度を緩和し、高耐圧で信頼性の高い窒化物半導体装置を提供する。

【解決手段】フィールドプレート構造を備えた窒化物半導体装置において、ゲート電極18に、オフ制御の制御電圧を印加するとき、フィールドプレート構造の傾斜面部直下の窒化物半導体層中13にはキャリアが存在しないようにする。

(もっと読む)

接合型電界効果トランジスタ

【課題】耐圧性に優れかつチャネル領域の不純物濃度やその厚さ等のばらつきの影響を受けにくいJFETを提供する。

【解決手段】SiC基板9の一方面上にはアルミニウム膜7が形成されている。そのアルミニウム膜7に接するように、そのアルミニウム膜7の両側に、SiC膜からなるチャネル領域4a、4bが設けられている。チャネル領域4a、4b上にはソース領域5a、5bを介してソース電極11a、11bが形成されている。チャネル領域4a、4bのアルミニウム膜7側と反対側にp型SiC膜2a、2bを介してゲート電極13が形成されている。SiC基板9の他方面上には、ドレイン領域6が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

金属キャリアを有する半導体デバイスおよび製造方法

【課題】 金属キャリアを有する半導体デバイス及び製造方法を提供する。

【解決手段】 金属キャリア基板を含む半導体デバイス。キャリア基板の上には、Alx1Gay1Inz1N(x1+y1+z1=1、x1≧0、y1≧0、z1≧0)の第1の半導体層が形成される。第1の半導体層の上にはAlx2Gay2Inz2N(x2+y2+z2=1、x2>x1、y2≧0、z2≧0)の第2の半導体層が配され、第2の半導体層の上にはゲート領域が配置される。半導体デバイスはさらに、ソース領域およびドレイン領域を含み、これらの領域のうちの一方が金属キャリア基板と電気的に接続され、第1の半導体層を介して延在する導電性領域を含む。

(もっと読む)

III族窒化物系半導体素子およびIII族窒化物系半導体素子の製造方法

【課題】低コストで製造することができ、かつ、高い絶縁破壊耐圧を有するIII族窒化

物系半導体素子、およびIII族窒化物系半導体素子の製造方法を提供する。

【解決手段】シリコン層、絶縁層、および表面にシリコンからなる複数の核領域と前記複

数の核領域の間を埋める絶縁領域を有する複合層がこの順に形成された基板と、前記基板

上に形成されたIII族窒化物系半導体からなるバッファ層と、前記バッファ層上に形成

されたIII族窒化物半導体からなる動作層と、前記動作層上に形成された第1の電極お

よび第2の電極とを備え、前記核領域のそれぞれの最大幅L1が、前記第1の電極および

前記第2の電極の間の距離L2よりも小さいことを特徴とする。

(もっと読む)

高電圧耐久III族窒化物半導体デバイス

【課題】高電圧の印加時に、電荷キャリアを導電領域内に抑制して、高電圧耐久性を呈する、HEMTのようなIII族窒化物半導体デバイスを提供する。

【解決手段】高電圧耐久III族窒化物半導体デバイスは、(100)シリコン層14、該(100)シリコン層14上の絶縁体層18、及び該絶縁体層18上のP型導電性の(111)シリコン層16を有する支持基板を備える、高電子移動度トランジスタ(HEMT)を備える。高電圧耐久HEMTは、P型導電性の(111)シリコン層16上に形成したIII族窒化物半導体本体12であって、HEMTのヘテロ接合を形成する、III族窒化物半導体本体も備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】本発明は、化合物半導体素子の動作に関係なく、リーク電流を防止することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置1は、2DEG310を有する第1の化合物半導体層31と、第1の化合物半導体層31上に配設され、キャリア供給層として機能する第2の化合物半導体層32と、2DEG310上に配設された第1の電極61と、2DEG310上において第1の電極61から離間して配設された第2の電極42と、を備えた化合物半導体素子10と、化合物半導体素子10の周囲を取り囲む領域の一部において2DEG310上に配設され、この2DEG310のキャリア濃度を低減させる外周電極62を有する外周領域11とを備える。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】高耐圧および高電流のスイッチング動作が可能で、かつ製造が容易なFETを提供する。

【解決手段】半導体薄体の一の主表面に設けられた、第1導電型のソース領域(1)と、第1導電型のチャネル領域(10)と、チャネル領域を限定する第2導電型の限定領域(5)と、他の主表面に設けられた第1導電型のドレイン領域(3)と、厚さ方向に連続する第1導電型のドリフト領域(4)とを備え、ドリフト領域(4)およびチャネル領域(10)の不純物濃度は、ソース領域(1)、ドレイン領域(3)および限定領域(5)の不純物濃度よりも低く、チャネル領域(10)の不純物濃度はドリフト領域(4)の不純物濃度よりも低い。

(もっと読む)

半導体装置

【課題】電界緩和効果が大きいフィールドプレート構造を有する半導体装置を提供する。

【解決手段】半導体装置10は、基板11上に形成された窒化物半導体層と、窒化物半導体層と電気的接触をして形成されたソース電極15と、窒化物半導体層と電気的接触をして形成されたドレイン電極16と、ソース電極とドレイン電極との間の窒化物半導体層上に形成されたゲート電極17と、ゲート電極とドレイン電極との間の窒化物半導体層の表面に形成されたキャップ層18と、キャップ層を覆うパシベーション層19と、キャップ層18とパシベーション層19から成る層の上にゲート電極の一部として形成されたフィールドプレート20と、を備え、キャップ層は、窒化物半導体層の材料の組成の一部の組成を含む組成から成る材料から成り、2〜50nmの厚さを有し、キャップ層のゲート電極側の端部には、60°以下のテーパ角が設けられ、斜面が形成されている。

(もっと読む)

半導体装置

【課題】GaN電子走行層、AlGaN電子供給層、およびGaNキャップ層が順次積層された半導体装置において、高周波数動作および高出力動作を実現することが可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に順次積層されたGaN電子走行層12、AlGaN電子供給層14、およびGaNキャップ層16と、GaNキャップ層16上に形成されたゲート電極18と、ゲート電極18の両側であって、AlGaN電子供給層14上に形成されたソース電極20およびドレイン電極22と、ゲート電極18とソース電極20との間のGaNキャップ層16に形成された第1の凹部30と、を具備し、第1の凹部30が有する底面32下におけるGaNキャップ層16の厚さは、ゲート電極18下におけるGaNキャップ層16の厚さに比べて薄い半導体装置である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ハイサイド駆動部62からの駆動信号を受ける第1のスイッチング機能部と、ローサイド駆動部64からの駆動信号を受ける制御電極とを有する第2のスイッチング機能部とを備え、ハイサイド駆動部62は、ノーマリーオン型の電界効果トランジスタを含み、スイッチング制御信号の基準電圧を出力ノードの電位へシフトした駆動信号を出力し、第1のスイッチング機能部はノーマリーオン型の第1の電界効果トランジスタTr1を含み、第2のスイッチング機能部はノーマリーオン型の第2の電界効果トランジスタTr2を含み、ハイサイド駆動部62および第1の電界効果トランジスタTr1は第1の半導体チップ71に含まれている。

(もっと読む)

化合物半導体エピタキシャルウェハ及びその製造方法、並びにHEMT素子

【課題】化合物半導体エピタキシャルウェハ外周部より得られたHEMT素子であってもリーク電流の急激な増加がなく、良好な耐圧を持つHEMT素子が得られる化合物半導体エピタキシャルウェハ及びその製造方法、並びにこのような化合物半導体エピタキシャルウェハを用いて得られるHEMT素子を提供する。

【解決手段】基板1上に、バッファ層3と、下部電子供給層4と、電子走行層5と、上部電子供給層6と、を有する化合物半導体エピタキシャルウェハ10において、前記バッファ層3はAlGaAsからなり、前記下部電子供給層4及び前記上部電子供給層6はAlGaAsからなり、前記下部電子供給層4及び前記上部電子供給層6のAl組成が0.2

0以上0.27以下であり、かつ前記バッファ層3のAl組成が前記下部電子供給層4の

Al組成より小さい。

(もっと読む)

半導体素子およびその製造方法

【課題】より高いブレークダウン電圧に適した半導体素子構造およびその製造方法を提供する。

【解決手段】半導体基板構造(100)は、半導体基板(1)と、半導体基板(1)の上部にGaNタイプの層スタック(20)とを備える。GaNタイプ層スタック(20)は、少なくとも1つのバッファ層(21,22)と、第1活性層(2)と、第2活性層(3)とを備え、第1活性層と第2活性層の界面において、能動素子領域が規定可能である。半導体基板(1)は、絶縁層(12)の上に存在しており、所定のパターンに従って溝(14)を規定するようにパターン化され、そのパターンは、こうした能動素子領域の下地となる少なくとも1つの溝(14)を含み、前記溝(14)は、絶縁層(12)から、GaNタイプ層スタック(20)の少なくとも1つのバッファ層(21,22)の中まで延びて、前記少なくとも1つのバッファ層(22)の範囲で過成長しており、第1および第2活性層(2,3)は、少なくとも能動素子領域の範囲で連続している。

(もっと読む)

化合物半導体装置

【課題】電流コラプスを低減させてRF特性を改善し、携帯電話基地局用アンプに必要とされる耐圧を得ることを可能とする。

【解決手段】 AlGaN層3を成長形成するに際して、i−GaN層2上にノンドープでAl組成率が15%程度のAlGaN層(i−AlGaN層)11を膜厚3nm程度に成長し、更にSiを濃度2×1018/cm3程度にドープしたAl組成率が15%程度のAlGaN層(n−AlGaN層)12を膜厚17nm程度に成長し、これら2層構造からなるAlGaN層3を形成する。

(もっと読む)

半導体素子

【課題】窒化物半導体による分極接合を用いた半導体素子において、高い歩留まりで高性能な素子を作製する。

【解決手段】InaGa1−aNチャネル層9、AlxInyGa1−x−yNバリア層10、およびInbGa1−bNキャップ層11により分極接合を形成する(0≦a、b、c<0.02)。また、上記バリア層の膜厚T及びAl組成xは、41<T<310(単位:nm)、0.08≦x<0.12、又は30<T<150、0.12≦x<0.16、又は24<T<92、0.16≦x<0.20、又は19<T<62、0.20≦x<0.24、又は16<T<45、0.24≦x<0.28、又は14<T<34、0.28≦x<0.32、又は12<T<27、0.32≦x<0.36、又は11<T<22、0.36≦x<0.40のいずれかの範囲にある。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリセス構造を採用してノーマリーオフ動作を可能とするも、バラツキの小さい安定した閾値を有し、十分な高耐圧を実現する信頼性の高い化合物半導体装置を実現する。

【解決手段】電子走行層3と電子供給層4との間にi−AlNからなる中間層5を形成し、キャップ構造7上のゲート電極の形成予定部位に中間層5をエッチングストッパとして用いて開口11aを形成した後、中間層5の開口11aに位置整合する部位に熱リン酸を用いたウェットエッチングにより開口11bを形成して、開口11a,11bからなる開口11をゲート絶縁膜12を介して下部が埋め込み、上部がキャップ構造7上方に突出するゲート電極13を形成する。

(もっと読む)

201 - 220 / 602

[ Back to top ]