Fターム[5F102FA01]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | 高耐圧化 (602)

Fターム[5F102FA01]に分類される特許

141 - 160 / 602

半導体装置およびその製造方法

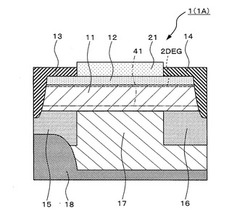

【課題】本発明は、SBD、HEMT等のデバイスに逆方向電圧をかけたときの電極端部に生じる電界集中を緩和して電流コラプス、及び長期信頼性の問題を解決した半導体装置を提供する。

【解決手段】窒化物化合物半導体層を有する電子走行層11と、前記電子走行層11に形成された窒化物化合物半導体からなる電子供給層12と、前記電子供給層12上に形成された第1電極13と、前記電子供給層12上に前記第1電極13と離間して形成された第2電極14と、前記電子走行層11および前記電子供給層12を挟んで前記第1電極13に対向して形成された、前記第1電極13と同電位の第1導電体14と、前記電子走行層11および前記電子供給層12を挟んで前記第2電極14に対向して形成された、前記第2電極14と同電位の第2導電体16とを有する半導体装置1を提供する。

(もっと読む)

接合型電界効果トランジスタを備えた半導体装置およびその製造方法

【課題】埋込ゲート層とゲート配線とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置を提供する。

【解決手段】埋込ゲート層10とゲート配線12との電気的な接続をトレンチ13内に形成したp+型コンタクト埋込層14によって行うようにする。これにより、p+型コンタクト埋込層14のみしか配置されないトレンチ13の幅を、従来の半導体装置のように層間絶縁膜やゲート配線などが配置されるトレンチと比較して、狭くすることが可能となる。したがって、埋込ゲート層10とゲート配線12とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置とすることが可能となる。

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法

【課題】本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。

【解決手段】このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】ゲートのリーク電流を少なくする。

【解決手段】サファイアからなる基板11上に膜厚が30nmのGaNからなる核形成層12を形成し、核形成層12上に膜厚が2μmのGaNからなるバッファ層13を形成し、バッファ層13上に膜厚が20nmでありかつIn組成が0.25のInAlNからなるバリア層16の第1の層14を形成し、第1の層14上に膜厚が20nmでありかつIn組成が0.15のInAlNからなるバリア層16の第2の層15を形成し、第2の層15上にAl/TiまたはTi/Auからなるソース電極17、ドレイン電極18をオーミック接合により形成し、第2の層15が除去された部分にNi/Auからなるゲート電極19を形成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】低オン抵抗の電界効果トランジスタを低コストで実現する。

【解決手段】電界効果トランジスタは、第一導電型の半導体基体であるN+型SiC基板2及びN-型ドレイン領域1と、N+型SiC基板2の第一主面側に、P型ウエル領域3とN+型ソース領域5とゲート電極7とを有する。N-型ドレイン領域1中に、N-型ドレイン領域1とはバンドギャップの異なるP+型ポリシリコンで形成され、第一主面から第二主面へ向かって伸びる柱状のヘテロ半導体領域4が、間隔を置いて並んで複数形成されている。ゲート電極7直下にチャネル領域が形成されないときに、N-型ドレイン領域1がヘテロ半導体領域4と接することによりN-型ドレイン領域1の全域が空乏化される。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、窒化物系半導体装置を提供することを目的とする。

【解決手段】ショットキー電極30が、ソース電極24とドレイン電極26とが対向する領域の、ソース電極24とドレイン電極26とが対向する方向と略直交する方向にゲート電極28と並んで形成されている。ショットキー電極30は、AlGaN層20とショットキー接合されており、ソース電極24に電気的に接続されている。

(もっと読む)

大面積シリコン基板及びその他の基板上の多層III族窒化物バッファの成長

【課題】半導体基板上に第1エピタキシャル層を形成し且つ該層をエッチングして複数の分離領域を形成することを包含する方法を提供する。

【解決手段】本方法は、エッチングした第1エピタキシャル層106a上に第2エピタキシャル層106bを形成することを含む。106a,b層は少なくとも1個のIII族窒化物を含み、106a,b層は一緒になって1個のバッファ106を形成する。本方法は、更に、該バッファ上に装置層108を形成し、且つ該装置層を使用して半導体装置を製造することを包含している。106b層は、実質的に106a領域上にのみ存在する106b領域を包含することが可能である。106b層は、又、106a領域及び該基板を被覆することが可能であり、且つ106b層はエッチングするか又はしない場合がある。該装置層は106b層を形成するために使用するのと同じ操作期間中に形成することが可能である。

(もっと読む)

窒化物系半導体装置

【課題】導通抵抗が低く、かつ高い電圧を維持すると共に、ゲート絶縁膜の破壊を抑制したゲート信頼性の高い窒化物系半導体装置を提供することを目的とする。

【解決手段】AlGaN層20上に形成されたショットキー電極22が、正孔をソース電極30に流す(輸送する)ため、ゲート絶縁膜24、特にトレンチ部23のコーナー部に集中して電圧が印加されることがなくなる。

(もっと読む)

窒化物系化合物半導体、窒化物系化合物半導体素子、およびその製造方法

【課題】長期信頼性が高い窒化物系化合物半導体、窒化物系化合物半導体素子、およびその製造方法を提供すること。

【解決手段】アルミニウム原子、ガリウム原子、インジウム原子およびボロン原子から選択される、少なくともガリウム原子を含むIII族原子と、窒素原子とを含む窒化物系化合物半導体であって、前記III族原子の格子間原子を拡散させる拡散促進物質を添加物としてドープしたものである。好ましくは、前記拡散促進物質はリン、砒素、またはアンチモンである。

(もっと読む)

シングルゲートまたはマルチゲートフィールドプレート製造

【課題】電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセスの提供。

【解決手段】本製造プロセスは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体を有する半導体装置において、熱による出力低下を低減する。

【解決手段】半導体装置は、基板101上に設けられ、III-V族窒化物半導体からなるバッファ層102と、バッファ層102上に設けられ、III-V族窒化物半導体からなる第1の半導体層103と、第1の半導体層103上に設けられ、III-V族窒化物半導体からなる第2の半導体層104と、基板101の裏面上に設けられ、接地に接続された裏面電極111と、第2の半導体層104上に互いに離間して設けられたソース電極132及びドレイン電極134と、第2の半導体層104上に設けられたゲート電極136とと、第2の半導体層104、第1の半導体層103、及びバッファ層102を貫通し、少なくとも基板101に達し、ソース電極132と裏面電極111とを電気的に接続させるプラグ109とを備えている。

(もっと読む)

電界効果トランジスタ

【課題】III族窒化物半導体からなる電界効果トランジスタにおける高電圧スイッチング時の電流コラプスを効果的に抑制できるようにする。

【解決手段】第1の半導体層103は、少なくともゲート電極106におけるドレイン電極107側の端部の下側の領域において、炭素濃度が1×1017cm−3未満である低炭素濃度領域を有し、基板101の上面から第1の半導体層103及び第2の半導体層104を含むドレイン電極までの半導体層の厚さをd1(μm)とし、低炭素濃度領域の厚さをd2(μm)とし、動作耐圧をVm(V)としたとき、Vm/(110・d1)≦d2<Vm/(110・d1)+0.5の関係を満たし、且つ、緩和状態におけるオン抵抗をRon0とし、動作電圧Vmにおけるオフ状態からオン状態に遷移した100μs後のオン抵抗をRonとしたとき、電流コラプス値の指標とするRonとRon0との比の値が、Ron/Ron0≦3である。

(もっと読む)

半導体装置

【課題】作製プロセスに起因する特性劣化を生ぜず、ボンディングパッドの電位変化による特性変化を受け難い小型化した半導体装置を提供する。

【解決手段】半導体装置10は、アクティブ領域12と、アクティブ領域12を覆う第1の絶縁層13と、第1の絶縁層13上に形成されるフローティング導体14と、第1の絶縁層13上およびフローティング導体14上に形成される第2の絶縁層15と、第2の絶縁層17上に形成されたボンディングパッド18と、アクティブ領域12とボンディングパッド18を電気的に接続する導通ビア19,20と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ドレイン電流コラプスを抑制すること。

【解決手段】窒化物半導体層19上に形成されたソース電極20、ゲート電極24およびドレイン電極22と、前記窒化物半導体層上に接して形成された窒化シリコン膜26と、前記ゲート電極と前記ドレイン電極との間の前記窒化シリコン膜の上面に接して設けられた有機絶縁膜32と、を含む半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート−ソース間の容量低減及びソース抵抗を低減させ、且つ耐圧向上、高出力化及び高周波化を、容易且つ確実に可能とする量産化に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極19を形成する際に、4層の電子線レジスト11〜14を用いてゲート開口17を形成し、ゲート開口17内に、キャップ層5の表面との接触面を含む幹状の下方部分19aと下方部分19aから傘状に拡がる上方部分19bとが一体形成されてなり、下方部分19aの接触面がドレイン電極7に比べてソース電極6に偏倚した位置に設けられており、上方部分19bの傘状の下端面のうちソース電極6側の部位がドレイン電極7側の部位よりもキャップ層5の表面からの高さが高いゲート電極19を形成する。

(もっと読む)

半導体装置

【課題】高温・高電圧で動作させた場合でも故障の発生を抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、GaNキャップ層38上のソースフィンガー12と、ソースフィンガーと交互に配置されたドレインフィンガー14と、ソースフィンガーとドレインフィンガーとの間のゲートフィンガー16と、ゲートフィンガーの上面と側面を覆う第1絶縁膜44と、ゲートフィンガーとドレインフィンガーとの間の第1絶縁膜上に設けられたフィールドプレート26と、活性領域18の外側で第1絶縁膜上にフィンガー方向と交差方向に設けられソースフィンガーとその両側のフィールドプレートとを接続するフィールドプレート配線28と、を備え、フィールドプレートと第1絶縁膜の第1段差部46とは100nm以上離れ、フィールドプレート配線と第1絶縁膜の第2段差部48とは100nm以上離れている半導体装置である。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】GaN系HEMTは、基板と、窒化ガリウム系半導体と、融点が3000℃と高融点金属のタンタルと低融点金属のアルミニウムが前記窒化ガリウム系半導体上に積層されてなる前記ソースおよび前記ドレイン電極を備えている。前記ソース電極および前記ドレイン電極は、前記タンタルと前記アルミニウムの積層膜厚の比(前記アルミニウム膜厚/前記タンタル膜厚)を10以上にし、積層後のアニール処理温度が510℃以上、600℃未満で処理されて成る。

(もっと読む)

電界効果トランジスタ

【課題】歩留りの低下を抑制する。

【解決手段】開口部121.1の形成により、第1の半導体層110の上面のうち、上方に第2の半導体層120が形成されていない部分の少なくとも一部には、絶縁体130.1が形成される。開口部121.1には、絶縁体130.1を覆うようにソース電極S10が形成される。ソース電極S10は、第1の半導体層110と前記第2の半導体層120との界面と接するように形成される。

(もっと読む)

141 - 160 / 602

[ Back to top ]