Fターム[5F102FA01]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | 高耐圧化 (602)

Fターム[5F102FA01]に分類される特許

121 - 140 / 602

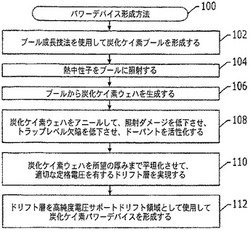

ブール成長された炭化ケイ素ドリフト層を使用してパワー半導体デバイスを形成する方法、およびそれによって形成されるパワー半導体デバイス

【課題】炭化ケイ素の好ましい電気特性にもかかわらず、その中においてより厚い電圧サポート領域を有する炭化ケイ素パワーデバイスの必要性が引き続き存在している。

【解決手段】高電圧炭化ケイ素パワーデバイスを形成する方法は、法外に高いコストのエピタキシャル成長された炭化ケイ素層の代わりに、高純度炭化ケイ素ウエハ材料から得られる高純度炭化ケイ素ドリフト層を利用している。本方法は、約100μmより厚い厚みを有するドリフト層を使用して10kVを超えるブロッキング電圧をサポートすることができる少数キャリアパワーデバイスと多数キャリアパワーデバイスの両方を形成することを含んでいる。これらのドリフト層は、その中に約2×1015cm−3未満である正味n型ドーパント濃度を有するブール成長炭化ケイ素ドリフト層として形成される。このn型ドーパント濃度は、中性子変換ドーピング(NTD)技法を使用して実現することができる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧が高く破壊等が生じにくい、信頼性の高い半導体装置を提供する。

【解決手段】基板上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層14と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスの底面は、中央部分23aが周辺部分23bに対し高い形状であることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリーク電流の発生及び耐圧の低下、又は電流コラプスの発生を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】キャップ層21に、n−GaN層6と、n−GaN層6上方に形成されたi−AlN層8と、i−AlN層8上方に形成されたn−GaN層10と、が設けられている。更に、n−GaN層6とi−AlN層8との間に形成され、i−AlN層8に近くづくほどAl組成が増加するAlGaN含有層7、又はi−AlN層8とn−GaN層10との間に形成され、i−AlN層8に近くづくほどAl組成が増加するAlGaN含有層9の少なくとも一方が設けられている。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】本発明は、電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果型トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明のヘテロ接合電界効果型トランジスタは、バリア層4及びバリア層4上に形成されたキャップ層5を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして窒化物半導体層上に設けられたゲート電極10と、ゲート電極10の両側に離間して夫々設けられたドレイン電極8及びソース電極9とを備える。ゲート電極10のドレイン電極8側端面とソース電極9側端面のうち少なくともドレイン電極8側端面は、キャップ層5と少なくとも部分的に乖離しており、当該乖離部分が空隙である。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

窒化物半導体装置

【課題】ゲート電極から染み出した金属がドレイン電極に到達することを抑制して、ドレイン−ゲート間の絶縁破壊を抑制する窒化物半導体装置を提供する。

【解決手段】ゲート電極5の直下に位置するAlGaN層22と、このAlGaN層22の直上に位置する絶縁膜30との間の界面Sに、ゲート電極5とドレイン電極1との間に位置するように、溝50を設けている。ゲート電極5から界面Sを伝ってドレイン電極1側へ染み出した金属を、溝50によって、堰き止めることができる。

(もっと読む)

窒化物半導体素子および窒化物半導体パッケージ

【課題】GaN電子走行層の厚さを広い範囲で選択することができ、デバイス設計の自由度を高めることができる窒化物半導体素子、および耐圧および信頼性に優れる窒化物半導体素子パッケージを提供すること。

【解決手段】基板41上に、AlN層47、第1AlGaN層48(平均Al組成50%)および第2AlGaN層49(平均Al組成20%)からなるバッファ層44を形成する。バッファ層44上には、GaN電子走行層45およびAlGaN電子供給層46からなる素子動作層を形成する。これにより、HEMT素子3を構成する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

炭化珪素半導体装置

【課題】従来よりオン抵抗が低くかつ高い耐圧を有する炭化珪素半導体装置を提供する。

【解決手段】この発明に従ったJFET10は、n型基板11と、p型層2、12と、n型層13と、ソース領域15と、ドレイン領域17と、ゲート領域16とを備える。n型基板11は、{0001}面に対するオフ角が32°以上である主表面11Aを有し、炭化珪素(SiC)からなる。p型層2、12は、n型基板11の主表面11A上に形成され、導電型がp型である。n型層13は、p型層2、12上に形成され、導電型がn型である。ソース領域15およびドレイン領域17は、n型層13において、互いに間隔を隔てて形成され、導電型がn型である。ゲート領域16は、n型層13において、ソース領域15とドレイン領域17との間の領域に形成され、導電型がp型である。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】 GaN系積層体15は、n−型GaNドリフト層4/p型GaNバリア層6/n+型GaNコンタクト層7、を有し、開口部28は表層からn−型GaNドリフト層4内にまで届いていて、開口部の壁面および底部を覆うように位置する、電子走行層22および電子供給層26を含む再成長層27と、開口部の周囲に位置するソース電極Sと、開口部の再成長層上に位置するゲート電極Gと、開口部の底部に位置する底部絶縁膜37とを備えることを特徴とする。

(もっと読む)

窒化物系化合物半導体素子の製造方法および窒化物系化合物半導体素子

【課題】リーク電流が低減された、耐圧性が高い窒化物系化合物半導体素子の製造方法および窒化物系化合物半導体素子を提供すること。

【解決手段】基板上に少なくともガリウム原子を含むIII族原子と窒素原子とからなる窒化物系化合物半導体層をエピタキシャル成長する成長工程と、素子構造形成前に、前記窒化物系化合物半導体層にレーザ光または電離放射線を照射し、前記窒化物系化合物半導体層中のIII族空孔と水素原子との複合体を分解する分解工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】開口部28が設けられたGaN系積層体15を備える縦型の半導体装置であって、n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を備え、開口部を覆うように電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、再成長層上に位置するゲート電極Gとを備え、ゲート電極Gは、p型GaNバリア層の厚み範囲に対応する部分を覆い、かつ開口部の底部から離れた位置の壁面内で終端している。

(もっと読む)

半導体装置およびその製造方法

【課題】開口部にチャネルを備える縦型半導体装置において、高周波特性を向上することができる半導体装置およびその製造方法を提供する。

【解決手段】 n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を有し、開口部28は表層からn型GaN系ドリフト層内にまで届いており、該開口部を覆うように位置する電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、ドレイン電極Dと、再成長層上に位置するゲート電極Gとを備え、ソース電極を一方の電極とし、またドレイン電極を他方の電極としてコンデンサを構成するとみて、該コンデンサの容量を低下させる容量低下構造を備えることを特徴とする。

(もっと読む)

直列接続式の高電子移動度トランジスターデバイス及びその製造方法

【課題】等価回路により電圧の累積効果を達成することが可能であって、ハイブレークダウン電圧の特性を有する高電子移動度トランジスターデバイスを提供する。

【解決手段】本発明は、製造プロセスで高電子移動度トランジスターを定義し、内部接続の方法で前記高電子移動度トランジスターを直列接続させた直列接続式の高電子移動度トランジスターデバイス及びその製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】

本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】

化合物半導体装置は、基板と、前記基板上に形成された窒化ガリウム系半導体と、前記窒化ガリウム系半導体上に形成された窒化ガリウム系保護層と、前記窒化ガリウム系保護層上にタンタルとアルミニウムが任意の順に積層されてなるオーミック電極とを備え、前記オーミック電極が形成された箇所の前記窒化ガリウム系保護層の膜厚は、前記オーミック電極が形成されていない箇所の前記窒化ガリウム系保護層の膜厚よりも薄い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的短い製造時間で容易且つ確実に反りのない基板を得ることを可能とし、低コストで信頼性の高い高耐圧及び高出力の化合物半導体装置を実現する。

【解決手段】Si基板10上に、AlNからなる第1のバッファ層2と、AlGaNのAl組成比率が均一となるように形成された均一組成領域3aと、第2のバッファ層3の上面に近づくにつれてAlGaNのAl組成比率が徐々に高くなるように形成された傾斜組成領域3bとが積層されてなる第2のバッファ層3とが形成され、第2のバッファ層3上に電子走行層4及び電子供給層6等が形成されてAlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 縦型GaN系半導体装置において、p型GaNバリア層による耐圧性能の向上を得ながら、オン抵抗を低くできる半導体装置を提供する。

【解決手段】 開口部28壁面に位置するチャネルを含む再成長層27と、端面が被覆されるp型バリア層6と、p型バリア層上に接するソース層7と、再成長層の上に位置するゲート電極Gと、開口部の周囲に位置するソース電極Sとを備え、ソース層が超格子構造で構成され、該超格子構造が、p型バリア層よりも小さい格子定数を持つ第1の層(a層)と、該第1の層よりも格子定数が大きい第2の層(b層)との積層体である、ことを特徴とする。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】本発明は、トランジスタ特性の再現性が高く、高速でパワーの大きい電界効果トランジスタ及びその製造方法を提供することを課題とする。

【解決手段】ダイヤモンド基板11と、前記ダイヤモンド基板11の一面11a側に離間して形成された第2の電極13及び第3の電極14と、2つの電極13、14の間に離間して形成された第1の電極15と、を有する電界効果トランジスタであって、第1の電極15とダイヤモンド基板11との間にIII族窒化物半導体層12が設けられ、ダイヤモンド基板11とIII族窒化物半導体層12との界面17の近傍領域に正孔伝導チャネル領域16が形成されている電界効果トランジスタ10を用いることによって前記課題を解決できる。

(もっと読む)

121 - 140 / 602

[ Back to top ]