Fターム[5F102FB01]の内容

接合型電界効果トランジスタ (42,929) | 特殊動作 (121) | SIT (80)

Fターム[5F102FB01]に分類される特許

21 - 40 / 80

半導体装置

【課題】優れた特性を有し、IC化に適した起動回路を提供する。

【解決手段】N型エピタキシャル層12に形成され、ドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成される。ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ドレイン領域121と、ゲートとして機能するP型分離領域13とドレイン領域121に印加される電圧により、P型素子分離領域13が逆バイアスされて空乏層が延びるチャネル領域を介して、JFETのソース引出層23が配置され、JFETが形成される。

(もっと読む)

エッジ終端性能改善のための電場停止層を備えた半導体構造

例示のエッジ終端構造は、半導体素子の周囲に電場停止層を形成することによって、ウエハから切断され実装された後に半導体素子の降伏電圧を維持する。電場停止層は、ドリフト層またはチャネル層のようなエッジ終端構造が提供された層のものより高いドーパント濃度を有する。電場停止層は、素子の周囲に高濃度でドープされた材料を保護し維持するため、素子の製造工程、すなわちメサエッチング中に素子の周囲を選択的にマスキングすることによって形成される。  (もっと読む)

(もっと読む)

電力用半導体装置

【課題】トランジスタの逆モード動作の特性改善が可能な超接合静電誘導型トランジスタを有する電力用半導体装置を提供する。

【解決手段】n型ドリフト層12と、n型ドリフト層12中に膜面に沿う方向に周期的に配置され、膜面に垂直な方向に伸長した複数の柱状のp型ゲート・ドリフト層14と、n型ドリフト層12の一方の側の表面に設けられn型ドリフト層12と電気的に接続されたドレイン電極23と、n型ドリフト層12の他方の側の表面に設けられた低抵抗のn+型ソース層16と、n+型ソース層16の表面に接するように設けられたソース電極21と、p型ゲート・ドリフト層14に接続されたゲート電極25とを有するノーマリオン型のSJ−SIT10と、ソース電極21とゲート電極25との間に接続され、ゲート電極25の電圧がソース電極21の電圧を超えないように維持する抵抗33とを備えている。

(もっと読む)

半導体装置

【課題】 一対の主電極の間に設けられたゲート電極を有する半導体装置において、高い耐圧を確保しながらオン抵抗を低くする技術を提供する。

【解決手段】 半導体装置100は、一対の主電極2,22間に設けられたゲート電極10を備えている。ゲート部10は絶縁ゲート電極部10aとショットキー電極部10bを有している。半導体装置100は、主電極2に接続するコンタクト領域18と、コンタクト領域18に隣接するチャネル半導体領域8と、チャネル半導体領域8の裏面に接しているp型半導体領域20と、チャネル半導体領域8とp型半導体領域20の両者に隣接するドリフト半導体領域12を備えている。絶縁ゲート電極部10aは、ゲート絶縁膜4を介してコンタクト領域18の表面に対向している。ショットキー電極部10bは、ドリフト半導体領域12の表面に直接的に接触している。

(もっと読む)

伝導を高めた非パンチスルー半導体チャネルを有する半導体デバイス及びその製法

デバイスにおける電流フローが整流接合(例えば、p−n接合又は金属半導体接合)の間で制限される、半導体デバイスが記載される。デバイスは、非パンチスルー挙動と高められた電流伝導能力を提供する。デバイスは、接合型電界効果トランジスタ(JFETs)、静電誘導トランジスタ(SITs)接合型電界効果サイリスタ、又はJFET電流制限器などのような電力半導体デバイスである。デバイスは、炭化ケイ素(SiC)等の広バンドギャップでできている。いくつかの実施形態において、デバイスは、常時オフ型SiC垂直接合型電界効果トランジスタである。デバイス及びデバイスを備える回路を製造する方法もまた記載される。 (もっと読む)

パラメータ抽出方法及び装置

【課題】電力変換回路に用いられる電界効果型トランジスタの等価回路モデルにおけるパラメータを比較的簡単な方法において高精度に抽出することにより、高精度な回路シミュレーションが行える環境を提供する。

【解決手段】電力変換回路に用いられる電界効果型トランジスタの等価回路モデルにおいて、ゲート−ソース間容量Cgs、ゲート−ドレイン間容量Cgd、及びチャネル電流源Ichを、電界効果型トランジスタの誘導性負荷におけるスイッチング波形から抽出する。

(もっと読む)

促進された導電性を有する非パンチスルー半導体チャネルを備えた半導体素子及び製法

半導体素子が記載されており、当該素子における電流の流れは変換接合(例えば、p−n接合又は金属−半導体接合)の間に閉じ込められる。当該素子は、非パンチスルー挙動と、促進された導電可能性とをもたらす。当該素子は、接合型電界効果トランジスタ(JFET)、スタティック誘導トランジスタ(SIT)、接合型電界効果サイリスタ、又はJFET電流リミッタであり得る。当該素子は、炭化ケイ素(SiC)などの広いバンドギャップ半導体により製造され得る。いくつかの実施形態によれば、当該素子は、通常OFFのSiC垂直接合型電界効果トランジスタであり得る。当該素子の製法、及び当該素子を備えた回路も記載されている。 (もっと読む)

フルオレン系高分子化合物及び有機薄膜素子

【課題】電荷輸送性が優れた高分子化合物、及びその製造方法を提供する。

【解決手段】下記式(1)で示される繰り返し単位を有する高分子化合物

〔式中、R1は、置換基を有していてもよいアリール基又は置換基を有していてもよいヘテロアリール基を表す。aは1〜3の整数を表す。R1が複数存在する場合、それらは同一でも異なっていてもよい。〕;特定の化合物を縮合重合させる工程を有する前記高分子化合物の製造方法。

(もっと読む)

分岐型化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】電荷輸送性に優れる両極性の有機半導体として利用可能な分岐型化合物の提供。

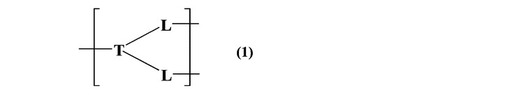

【解決手段】コア部と、該コア部に結合した少なくとも1つの側鎖部と、末端と、から構成される分岐型化合物であって、上記側鎖部の少なくとも1つは、下記一般式(1)で表される繰返し単位が1又は2以上繰り返しており(但し、コア部と結合する前記繰返し単位においては、Tがコア部に結合しており、2以上繰り返す前記繰返し単位においては、LがTに結合している。)、Lは、共役形成単位が複数連結して構成され、上記共役形成単位として少なくとも一つのチエニレン単位を含み、Lの末端(Tと結合していない側のLの末端)に存在する基は、少なくとも2つがアクセプター性の基である、分岐型化合物。

(式中、Lは置換基を有していてもよい2価の有機基を示し、Tは置換基を有していてもよい3価の有機基を示す。)

(もっと読む)

チップ内隣接構成デュアル静電誘導トランジスタ及びこれを用いたオーディオ用パワーアンプ回路

【課題】解決しようとする課題は、差動増幅器の入力段の対構成の差動トランジスタに最適な特性の揃ったディュアル静電誘導トランジスタを提供して、トランジスタ製造上の選別を容易にし、対形成不良を少なくし、回路製作上の調整作業を容易にすることである。

【解決手段】本発明では、半導体の1ウェーハ内の隣同士に隣接して、対構成の同一導電型、同一サイズの静電誘導トランジスタを構成して、差動増幅器の入力段用には、1チップとして組立し提供したものである。

(もっと読む)

有機電子デバイス及びその作製方法

【課題】高い移動度を有し光起電力を利用する有機電子デバイス、該デバイスを容易なプロセスで作製する方法を提供する。

【解決手段】従来とは異なる特定の環状構造のビシクロ化合物を溶媒に溶解した溶液を基板上に塗布することにより膜を製膜し、次いで加熱等の外部作用を加えることで、該ビシクロ化合物からエチレン誘導体を脱離させることにより基板上で変換された化合物を有機半導体として用いてなる光起電力を利用する有機電子デバイス、及びその作製方法。

(もっと読む)

静電誘導トランジスタ

【課題】高いゲート・ソース間耐圧を有する静電誘導トランジスタを提供する。

【解決手段】第1導電型の半導体基板の第1主面に、第1導電型の不純物領域であるソース領域と、前記ソース領域を取り囲むように第2導電型の不純物領域であるドレイン領域と、前記ソース領域と前記ドレイン領域との間にはメサ溝部を有し、前記半導体基板の第2主面の周縁部および前記メサ溝方向に交差する方向に、前記半導体基板の第1導電型の不純物と交互に配列するようにストライプ状の第2導電型不純物領域部であるゲート領域と、前記第1主面から前記ゲート領域まで達する深さの前記メサ溝部と、前記第1主面の前記ソース領域にはソース金属電極、前記ドレイン領域にはドレイン金属電極を有し、前記第2主面の前記ゲート領域の第2導電型不純物領域にゲート金属電極を有することを特徴とする静電誘導トランジスタ。

(もっと読む)

炭化ケイ素静電誘導トランジスタの制御装置及び制御方法

【課題】電力用変換器の過電流においてオン抵抗損失の著しい増大を抑制して、電力用変換器の小型・軽量化および低価格化をはかる。

【解決手段】定格電流容量の5倍ないし20倍のサージ電流が流れる電力用変換器に炭化ケイ素を素材とした静電誘導トランジスタを適用するにあたり、該静電誘導トランジスタのオン時のゲート電圧を定格電流以下の正常動作時にはゲート接合のビルトイン電圧以下として高速、低損失、高効率の電力変換を行い、定格を超える過電流が流れた場合にかぎりゲート電圧をビルトイン電圧以上に昇圧することにより過電流による素子破壊を防止する制御方法によって変換器に使用される炭化ケイ素静電誘導トランジスタの電流容量を変換のそれを大幅に超えない小容量とする。

(もっと読む)

選択的エピタキシまたは選択的注入の使用による、炭化ケイ素におけるセルフアライントランジスタおよびダイオードトポロジー

【課題】SiC内に縦型ダイオードおよびトランジスタを作る方法が提供される。

【解決手段】この発明に従った方法は、マスク(たとえば機構を素子にエッチングするために以前使用されたマスク)を選択的エピタキシャル成長または選択的イオン注入用に使用する。このように、静電誘導トランジスタおよびバイポーラ接合トランジスタのゲート領域およびベース領域が、セルフアラインプロセスで形成可能である。プレーナダイオードおよびプレーナエッジ終端構造(たとえばガードリング)を作る方法も提供される。

(もっと読む)

有機薄膜トランジスタ

【課題】 有機物を利用して薄膜トランジスタを製造しようとする場合、有機半導体薄膜のキャリア移動度が小さく、実用的な動作速度を有する有機薄膜トランジスタは得られなかった。この課題を解決するために縦型有機薄膜トランジスタが検討され、高速動作が期待されているが、十分な電流オンオフ比が得られないという課題がある。

【解決手段】 本発明の有機薄膜トランジスタは、基板上に第1の電極(ソース又はドレイン)、第1の有機半導体層、第3の電極(ゲート)、第2の有機半導体層、第2の電極(ドレイン又はソース)の順に積層した構造を有する。第3の電極の膜厚を80nm以上の厚膜とする。第3の電極の膜厚を厚くすることで、大きなオンオフ比を有する有機薄膜トランジスタが得られる。

(もっと読む)

有機薄膜トランジスタ

【課題】 有機物を利用して薄膜トランジスタを製造しようとする場合、有機半導体薄膜のキャリア移動度が小さく、実用的な動作速度を有する有機薄膜トランジスタは得られなかった。この課題を解決するために縦型有機薄膜トランジスタが検討され、高速動作が期待されているが、十分な電流オンオフ比が得られないという課題がある。

【解決手段】 本発明の有機薄膜トランジスタは、第1の絶縁層、第3の電極、第2の絶縁層を有機半導体層の形成前に成膜し、同時にパターニングする。パターニングされた第1の絶縁層、第3の電極、第2の絶縁層を覆うように第1の電極上に有機半導体層を形成する。本発明によれば、良好な製造歩留まりで製造でき、かつ電流オンオフ比の大きな有機薄膜トランジスタが得られる。

(もっと読む)

ワイドバンドギャップ半導体デバイス用ゲート駆動部

【課題】小型で、費用効率の良い半導体接合型ゲートトランジスタ用制御回路を提供する。

【解決手段】ゲート電流制限抵抗器445は、使用時にワイドバンドギャップ半導体接合ゲートトランジスタのゲート入力に結合され、接合ゲートトランジスタのゲートに入力されるゲート電流を制限する。AC結合充電コンデンサ435は、使用時にワイドバンドギャップ半導体接合ゲートトランジスタのゲート入力に結合され、ゲート電流制限抵抗器445に並列に配置されている。ダイオード430は、ゲート電流制限抵抗器445及びAC結合充電コンデンサ435に、ゲート駆動チップの出力に結合されている。使用時に、ダイオード430は、ゲート電流制限抵抗器445を介してワイドバンドギャップ半導体接合ゲートトランジスタのゲート入力に印加され、ゲート駆動チップからのゲート電圧出力を低下させる。

(もっと読む)

論理素子

【課題】有機物を利用した論理素子を製造しようとする場合、従来はシリコンデバイスと類似のMOS型構造を複数組み合わせた構造で検討されてきたが、有機半導体薄膜のキャリア移動度が小さく駆動に高い電圧を必要とするためで実用的な電圧範囲の動作ができなかった。

【解決手段】縦型の構造を有する有機静電誘導型トランジスタを複数組み合わせることによって、低電圧で動作可能なまた実装面積の小さな論理素子を得る。

(もっと読む)

絶縁ゲート炭化珪素半導体装置とその製造方法

【課題】SIT構造とノーマリオフ型の利点が得られるMOSFET構造との組み合わせ構造としても、オン抵抗を小さくできる炭化珪素絶縁ゲート型半導体装置の提供。

【解決手段】SiCn+基板1上にn−型半導体層3を備え、該層中に埋め込みp型ベース領域26、27と、前記n−型半導体層3の表面から前記p型ベース領域26に達する深さのトレンチ19と、その底部の前記p型ベース領域26の表面に選択形成されるn+型第一ソース領域30と、前記トレンチ19側壁表面に形成され一端が前記第一ソース領域30に接するp型チャネル領域24と、この領域の前記トレンチ側表面にゲート絶縁膜25を介して接するゲート電極22と、そのトレンチ側表面に層間絶縁膜28を介して接し、且つ前記トレンチ底部に露出する第一ソース領域30とp型ベース領域26とに接するソース電極20とを備える。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】 制御電極のリーク電流、周波数分散の抑制とチップの小型化、低オン抵抗化できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】 基板上にn型GaN層からなる高濃度の第1の窒化物半導体層と、第2の窒化物半導体層と、高濃度の第3の窒化物半導体層を積層形成し、ソース電極以外の領域を凹状に除去し、露出する第2の窒化物半導体層の側壁及び底面にゲート電極を形成する。基板裏面から第3の窒化物半導体層に接続するドレイン電極を形成する。ソース電極、ゲート電極を微結晶構造のGaN層上に形成することもできる。

(もっと読む)

21 - 40 / 80

[ Back to top ]