Fターム[5F102GD10]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160) | その他(MOS、擬似MIS) (744)

Fターム[5F102GD10]に分類される特許

81 - 100 / 744

半導体装置

【課題】ヘテロ接合を有する半導体装置において、リーク電流と電流コラプスのトレードオフ関係を打破し、リーク電流と電流コラプスの双方を抑制すること。

【解決手段】半導体装置1の電子走行層4は、炭素が導入されている高抵抗領域4aを含んでいる。電子走行層4と電子供給層5のヘテロ接合5aと平行な断面において、高抵抗領域4aの炭素の濃度分布が、ドレイン電極12とソース電極18の少なくともいずれか一方の下方で相対的に濃く、ドレイン電極12と絶縁ゲート部16の間で相対的に薄くなるような断面が存在している。

(もっと読む)

窒化物系半導体素子

【課題】本実施形態は、窒化物半導体層のクラックがほとんどなく、表面の粗度が極めて優秀であるので、全体的な安定性の向上された窒化物系半導体素子を提供する。

【解決手段】本実施形態の窒化物系半導体素子は、基板と、前記基板上に形成されるアルミニウムシリコンカーバイド(AlSixC1−x)前処理層と、前記前処理層上に形成されるAlがドーピングされたGaN層と、前記AlがドーピングされたGaN層上に形成されるAlGaN層とを含む。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層104に形成された第1チャネル型の第1MISFET120の第1ソース124および第1ドレイン126が、第1半導体結晶層104を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、またはニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層106に形成された第2チャネル型の第2MISFET130の第2ソース134および第2ドレイン136が、第2半導体結晶層106を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、または、ニッケル原子とコバルト原子との化合物からなる。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系トランジスタを簡便な構造で適切に保護することができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極110gと保護ダイオード用電極115pとが互いに接続されている。絶縁膜113は、所定値以上の電圧がゲート電極110gに印加された場合にリーク電流を保護ダイオード用電極115pと電子走行層104及び電子供給層103との間に流し、所定値は、HEMTがオン動作する電圧より高く、ゲート絶縁膜109gの耐圧よりも低い。

(もっと読む)

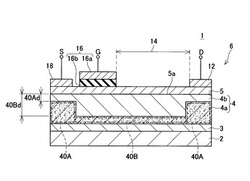

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

エンハンスメント型III−V族高電子移動度トランジスタ(HEMT)および製造方法

【課題】ノーマリオフ型、すなわちエンハンスメント型トランジスタであるIII族窒化物HEMTを提供する。

【解決手段】エンハンスメント型高電子移動度トランジスタ(HEMT)400はIII−V族半導体412上に位置するIII−V族バリア層414を含むヘテロ接合416、およびIII−V族バリア層414上に形成され、P型III−V族ゲート層452を含むゲート構造462を具える。P型III−V族ゲート層452によりゲート構造462下での2次元電子ガス(2DEG)の発生を防ぐ。エンハンスメント型HEMT400を製造する方法は、基板402を設け、基板402にIII−V族半導体412を形成し、III−V族半導体412上にIII−V族バリア層414を形成し、III−V族バリア層414上にP型III−V族ゲート層452を含むゲート構造462を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

ノーマリーオフ型高電子移動度トランジスタ

【課題】 ノーマリーオフ型高電子移動度トランジスタを提供する。

【解決手段】 ノーマリーオフ型トランジスタは、III−V半導体材料の第1の領域、第1の領域上のIII−V半導体材料の第2の領域、第2の領域上のIII−V半導体材料の第3の領域、および第3の領域の少なくとも1つの側壁に隣接するゲート電極を含む。第1の領域はトランジスタのチャネルを提供する。第2の領域は第1の領域のバンドギャップより大きなバンドギャップを有し、チャネル内に2D電子ガス(2DEG)を引き起こす。第2の領域は第1の領域と第3の領域との間に挿入される。第3の領域は、トランジスタのゲートを提供し、トランジスタが正の閾値電圧を有するようにチャネル内の2DEGを空乏化するのに十分な厚さを有する。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】ウルツ鉱型結晶構造の半導体を用いた電界効果トランジスタで、電極との接触抵抗を高くすることなく、バンドギャップエネルギーのより大きな半導体から障壁層が構成できるようにする。

【解決手段】ゲート電極104を挟んで各々離間して障壁層103の上に接して形成された2つの電流トンネル層105と、各々の電流トンネル層105の上に形成された2つのキャップ層106とを備える。電流トンネル層105の分極電荷は、障壁層103の分極電荷よりも大きい。

(もっと読む)

スイッチ装置

【課題】スイッチ素子のオン抵抗をより一層小さく抑えることができるスイッチ装置を提供する。

【解決手段】スイッチ素子10は、半導体基板104に絶縁膜15を介して接合された電界印加電極14を有している。駆動回路20の電界制御部22は、スイッチ素子10の電界印加電極14およびソース電極13に接続されており、電界印加電極14−ソース電極13間にバイアス電圧Veを印加する。電界制御部22は、閾値を超えるバイアス電圧Veをスイッチ素子10に印加することによって、電界印加電極14から半導体基板104のヘテロ接合界面に電界を印加する。要するに、スイッチ素子10がオン状態で、電界印加電極14から半導体基板104に印加される電界は、電界効果によってチャネル領域の電子濃度を高くし、スイッチ素子10のオン抵抗を小さくするように作用する。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

電界効果型トランジスタ

【課題】ゲート電極のドレイン端の電界を緩和し、ゲート絶縁膜の破損を低減する。

【解決手段】窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップエネルギーが大きい窒化物半導体で形成された電子供給層112と、チャネル層108の上方に形成されたソース電極116およびドレイン電極118と、チャネル層108の上方に形成されたゲート電極120と、チャネル層108の上方に形成され、チャネル層108からホールを引き抜くホール引抜部126と、ゲート電極120およびホール引抜部126を、電気的に接続する接続部124と、を備える電界効果型トランジスタ100。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】チャネルとなるナノワイアの周囲をゲート電極が取り巻いて形成されているFETが、より容易に高い精度で製造できるようにする。

【解決手段】被覆ナノワイア103を配置した基板121のゲート電極形成領域の上に、被覆ナノワイア103に交差して下部ゲート電極122に重なる上部ゲート電極124を形成する。上部ゲート電極124の形成は、公知のリソグラフィー技術とリフトオフとにより行えばよい。例えば、被覆ナノワイア103が下部ゲート電極122と交差して配置されている基板121の上に、電子ビーム露光により電極形成部に開口を備えるレジストパターンを形成し、この上に、電極材料を堆積する。この後、先に形成してあるレジストパターンを除去すれば、上部ゲート電極124が形成できる。

(もっと読む)

半導体装置とその製造方法

【課題】 半導体装置を高耐圧化する技術を提供することを目的とする。

【解決手段】 半導体装置100は、p型の埋込み層26と、p型埋込み層26上に設けられており、ヘテロ接合面3が構成されている窒化物半導体のヘテロ接合層32を備えている。p型埋込み層26は、ソース電極10側からドレイン電極2側に向けて厚みが減少する厚み減少部24を有している。厚み減少部24では、ソース電極10側の減少開始点14からドレイン電極2側の減少終了点16までの長さ24bが、減少開始点14における厚み24aよりも長い。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

81 - 100 / 744

[ Back to top ]