Fターム[5F102GK08]の内容

接合型電界効果トランジスタ (42,929) | バッファ層(中間層) (2,318) | 多層構造(起格子を含む) (565)

Fターム[5F102GK08]に分類される特許

61 - 80 / 565

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

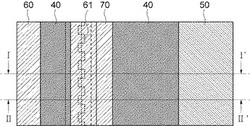

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置の製造方法

【課題】水素を用いた熱分解において、水素濃度を規定してエッチング速度を制御することで、半導体装置の製造方法の加工精度を向上させる。

【解決手段】半導体装置1の製造方法は、基板10に窒化物半導体で形成された第1層(障壁層25)および第2層(キャップ層26)を順に堆積させる堆積工程と、窒素および水素の混合雰囲気中で加熱して第2層をエッチングする熱エッチング工程とを備える。熱エッチング工程では、水素濃度が1%以上20%以下であることが望ましい。

(もっと読む)

半導体装置

【課題】基板の反りを抑制しつつ、バッファ層及び化合物半導体の厚さを稼ぐことができ、素子耐圧を向上することができる半導体装置を提供する。

【解決手段】半導体装置は、基板2と、バッファ層3と、窒化物系化合物半導体4とを備える。バッファ層3は、AlN層とGaN層とを積層した第1のバッファ領域321,331と、GaN層を有する第2のバッファ領域322,332とを交互に積層して構成される。バッファ層3において窒化物系化合物半導体4側の第1のバッファ領域331とそれに隣接する第2のバッファ領域332との1組の全体のAl組成は基板側の1組のAl組成に対して大きく設定されている。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

半導体デバイスおよび方法

【課題】光照射に適合した、少なくとも1つの電位障壁、又は表面障壁を持つ半導体デバイスの製造または処理に関し、高い絶縁破壊電圧と、大電流で低いキヤリア密度を有するデバイスの製造方法を提供する。

【解決手段】a)基板1を用意するステップと、b)第1エピタキシャル半導体層3を基板1の上に設けるステップと、c)1次元または2次元の繰り返しパターンを形成するステップと、を含み、パターンの各部分が、0.1〜50の範囲のアスペクト比を有するようにした方法を開示する。対応する半導体デバイス、電子回路および装置も開示している。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

半導体装置

【課題】窒化物半導体により、反転型のHEMTが構成された半導体装置において、半導体装置の形成を容易としつつ2DEGを効果的に形成する。

【解決手段】窒化物半導体からなる下地層15の(0001)面上に、窒化物半導体からなる電子供給層17、窒化物半導体からなる電子走行層19の順に積層され、電子走行層19における電子供給層17と反対の面上に、ゲート電極21、ソース電極23、及びドレイン電極25が設けられている。そして、電子走行層19における電子供給層17側に、二次元電子ガスが形成される。このような反転型のHEMTが構成された半導体装置10において、分極の正方向を[0001]方向とした場合、電子供給層17の自発分極とピエゾ分極の和P2が、電子走行層19の自発分極とピエゾ分極の和P1よりも大きくなっている。

(もっと読む)

エピタキシャル基板

【課題】シリコン基板を下地基板とし、基板サイズに比して問題ない程度に反りが抑制され、半導体素子の作製に好適なエピタキシャル基板を提供する。

【解決手段】エピタキシャル基板が、シリコン単結晶からなる下地基板と、下地基板の上に形成された複数のIII族窒化物層からなるIII族窒化物層群と、を備えており、下地基板が、所定のn型ドーパントが添加されてなることでn型の導電性を有し、かつ、比抵抗が0.1Ω・cm以下であり、複数のIII族窒化物層がそれぞれ、少なくともAlまたはGaを含み、エピタキシャル基板の反り量をSR(単位:μm)、窒化物層群の総膜厚をte(単位:μm)、下地基板の膜厚をts(単位:mm)、下地基板の直径をds(単位:mm)とするときに、規格化反り指数KがK={(SR/te)×(ts/ds)2}≦1×10-3なる関係式をみたすようにする。

(もっと読む)

エピタキシャル基板

【課題】シリコン基板を下地基板とし、基板サイズに比して問題ない程度に反りが抑制され、半導体素子の作製に好適なエピタキシャル基板を提供する。

【解決手段】エピタキシャル基板10が、シリコン単結晶からなる下地基板1と、下地基板1の上に形成された複数のIII族窒化物層2,3,4からなるIII族窒化物層群と、を備えており、下地基板1が、ボロンが添加されてなることでp型の導電性を有し、かつ、比抵抗が0.01Ω・cm以上0.1Ω・cm以下であり、複数のIII族窒化物層2,3,4がそれぞれ、少なくともAlまたはGaを含み、エピタキシャル基板の反り量をSR(単位:μm)、窒化物層群の総膜厚をte(単位:μm)、下地基板1の膜厚をts(単位:mm)、下地基板1の直径をds(単位:mm)とするときに、規格化反り指数KがK={(SR/te)×(ts/ds)2}≦1×10-3なる関係式をみたすようにする。

(もっと読む)

半導体装置

【課題】バッファ層からキャリア層への不純物拡散による悪影響を排除することができる。

【解決手段】このバッファ層20における最下部には超格子層(第1の領域)21が配され、その上には拡散防止下部層22、拡散防止層(第2の領域)23、拡散防止上部層24が順次形成されている。基板11上に形成されたバッファ層20、キャリア層30中においては、バッファ層20中の超格子層21のみに意図的に不純物がドーピングされ、他の層はノンドープである。そのc軸方向が膜厚方向であり、a軸は成長層の面内方向(膜厚方向と垂直な方向)となる。a軸格子定数は膜厚方向にわたりほぼ一定となるのに対し、c軸格子定数は拡散防止層23で極大値をとる。

(もっと読む)

エピタキシャル基板のシート抵抗評価方法

【課題】下地基板の導電性を問わずに非破壊でHEMT構造のシート抵抗を評価する方法を提供する。

【解決手段】HEMT構造を備えるエピタキシャル基板のシート抵抗評価方法が、障壁層におけるIII族元素の組成比を除いて評価対象エピタキシャル基板と同一の構造を有する複数のエピタキシャル基板のそれぞれについてフォトルミネッセンス測定を行い、得られたスペクトルからバンド端ピーク強度値を取得する第1予備測定工程と、複数のエピタキシャル基板のそれぞれについてシート抵抗値を測定する第2予備測定工程と、取得したバンド端ピーク強度値とシート抵抗値とから検量線を作成する検量線作成工程と、評価対象エピタキシャル基板についてフォトルミネッセンス測定を行ってバンド端ピーク強度値を取得する実測工程と、得られたバンド端ピーク強度値と検量線とに基づいて評価対象エピタキシャル基板のシート抵抗値を算出する工程と、を備える。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース18、ドレイン20、およびゲート22を含む。第1のスペーサ層26が、活性領域の上方でソースとゲートの間にあり、第2のスペーサ層28が、活性領域の上方でドレインとゲートの間にある。第1のスペーサ層上の第1のフィールドプレート30、及び第2のスペーサ層上の第2のフィールドプレート32が、ゲートに接続される。第3のスペーサ層34が、第1のスペーサ層、第2のスペーサ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、第3のフィールドプレート36が、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート部におけるリーク電流が低減できる反面、プロセス上の制約があるため製造が困難で、ゲートリーク電流を安定して低減させることが困難だった。

【解決手段】基板と、前記基板上に形成され且つ二次元キャリアガスを有する半導体機能層と、前記半導体機能層上において互いに離間して形成される第1及び第2の主電極と、前記半導体機能層上における前記第1及び第2の主電極間に形成される制御電極と、前記半導体機能層と前記制御電極との間に形成される金属酸化膜と、を備え、

前記金属酸化膜と前記半導体機能層との接合界面における結晶格子は不連続であることを特徴とする半導体装置。

(もっと読む)

窒化物半導体デバイス用エピタキシャルウエハとその製造方法

【課題】Si基板上のAlN下地層の上面における凹凸をマスクするように平滑な上面を有する高Al組成比のAlGaN層形成し、AlN下地層の表面凹凸に起因するV字欠陥を上面に含まない窒化物半導体デバイス用エピタキシャルウエハを提供する。

【解決手段】窒化物半導体デバイス用エピタキシャルウエハ(10)は、Si基板上(1)にMOCVDで順次積層されたAlN下地層(2)、AlxGa1−xN(0.6≦x<1)のモフォロジー改善層(3)、AlGaNバッファ層(4)を含み、そのモフォロジー改善層(3)は熱拡散を利用して平滑化された上面を有することと特徴としている。

(もっと読む)

エネルギー障壁を有するヘテロ接合トランジスタおよび関連する方法

【課題】チャネル内へのキャリアの閉じ込めを改善すること。

【解決手段】へテロ接合トランジスタは、III族窒化物を含むチャネル層14と、チャネル層の上のIII族窒化物を含む障壁層16と、チャネル層14が障壁層16とエネルギー障壁38との間にあるようにした、チャネル層14の上のインジウムを有するIII族窒化物の層を含むエネルギー障壁とを備えることができる。障壁層16は、チャネル層よりも大きなバンドギャップを有することができ、エネルギー障壁38のインジウム(In)の濃度はチャネル層14のインジウム(In)の濃度よりも高い可能性がある。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】所望の不純物濃度と、高い結晶性とを有するドリフト層を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】バッファ層31は、基板30上に設けられ、不純物を含有する炭化珪素から作られ、1μmより大きく7μmより小さい厚さを有する。ドリフト層32は、バッファ層31上に設けられ、バッファ層31の不純物濃度よりも小さい不純物濃度を有する炭化珪素から作られている。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

化合物半導体装置及び化合物半導体装置の製造方法

【課題】トレンチを用いて素子分離され、且つ、隣接素子の動作による影響が抑制された化合物半導体装置及び化合物半導体装置の製造方法を提供する。

【解決手段】半導体基板10と、キャリア走行層21とキャリア供給層22を有し、半導体基板上に配置された窒化物半導体層20と、上端部がキャリア走行層とキャリア供給層との界面よりも上方に位置する空洞40を内部に有する、窒化物半導体層の周囲を囲んで配置された素子分離絶縁膜30とを備える。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

61 - 80 / 565

[ Back to top ]