Fターム[5F102GM04]の内容

接合型電界効果トランジスタ (42,929) | ゲート下介在層(ゲートメタル電極底面とチャネル層表面間に介在する層) (3,125) | 単一半導体層 (2,140) | 3−5族 (2,057)

Fターム[5F102GM04]の下位に属するFターム

Fターム[5F102GM04]に分類される特許

1,721 - 1,734 / 1,734

エンハンスメント型III族窒化物デバイス

III族窒化物スイッチは、凹型のゲートコンタクトを含み、ノミナリーオフの、すなわち、エンハンスメント型のデバイスを提供する。凹型のゲートコンタクトを提供することにより、ゲート電極が不活性状態である場合には、2つのIII族窒化物材料の界面に形成された伝導チャンネルが遮断され、デバイス中の電流の流れを防止する。ゲート電極は、ショットキコンタクト又は絶縁金属コンタクトである可能性がある。2つのゲート電極が提供され、ノミナリーオフ特性の双方向スイッチを形成することが可能である。ゲート電極と共に形成された凹部は、傾斜した側壁を持つ可能性がある。デバイスの電流伝達電極に関連して、多くの形状にてゲート電極を形成することが可能である。  (もっと読む)

(もっと読む)

電極、その製造方法およびそれを用いた半導体素子

低接触抵抗を実現しつつ表面荒れの少ない電極が得られる技術を提供する。

半導体膜101の上部に設けられる電極であって、この半導体膜101の上部にこの半導体膜の側から順に積層された第一金属層102と第二金属層103とを有し、この第一金属膜102が、Alからなり、この第二金属膜103が、Nb、W、Fe、Hf、Re、TaおよびZrからなる群より選ばれる1種以上の金属からなることを特徴とする電極。

(もっと読む)

絶縁体構造を強化した電界効果トランジスタ

【解決手段】材料層の界面の面内格子定数の間の関係を操作することにより、III族窒化物ベースの電界効果トランジスタの性能特性を改善する。III族窒化物材料の界面において生成される高移動度の二次元電子ガスは、低いオン抵抗での高い導電を可能にし、III族窒化物材料の特性に従って得られた自発分極電界の操作によって制御可能である。電界効果トランジスタは、ノミナリーオン型の素子として形成可能であり、その際、界面を形成する材料の面内格子定数は一致する。材料層の一方が、他方の層の材料よりも大きい面内格子定数を有するようにして、ノミナリーオフ型の素子を形成してもよい。層の材料は、本発明の特性に対して特に調整したInAlGaN/GaNの層であることが好ましい。 (もっと読む)

III族窒化物素子の不動態化およびその方法

【課題】

【解決手段】III族窒化物半導体素子およびその製造方法の実施形態は、高温処理中にIII族窒化物材料に損傷を与えずに、素子のコンタクトを形成することを可能にする低抵抗の不動態化層を備えてよい。不動態化層は、素子全体を不動態化するために用いられてよい。不動態化層は、さらに、素子のコンタクトと活性層との間に設けられて、導電のための低抵抗の電流路を提供してもよい。この不動態化処理は、FET、整流器、ショットキダイオードなど、任意の種類の素子に用いて、破壊電圧を改善すると共に、コンタクトの接合部付近の電界集中効果を防止してよい。不動態化層は、外部拡散に関してIII族窒化物素子に影響を与えない低温アニールで活性化されてよい。

(もっと読む)

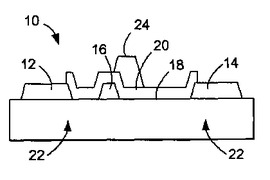

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

ひずみ印加半導体デバイス

多数キャリアが正孔であるトランジスタにおいて、少なくとも1つの狭いバンドギャップの領域または層が、p型にドーピングされるかまたは過剰の正孔を含み、かつ機械的圧縮ひずみを受け、これによって、正孔の移動度がかなり増大し得る。pチャネル量子井戸FETでは、量子井戸のInSb井戸のp型層5(変調ドーピングまたは直接ドーピングされている)が、In1−xAlxSb層4と、In1−xAlxSb層6との間にあるが、ここで、xは、軽い正孔および重い正孔が、kTをはるかに超える量だけ分離されるような範囲にまで、層5中にひずみを導入するに十分な値である。pnpバイポーラデバイスを含む、本発明の範囲内にあるトランジスタは、相補型論理回路における電子が多数キャリアである従来の等価物と一緒に用いられ得る。  (もっと読む)

(もっと読む)

増大した線形性および製造可能性を有するFETを含むBiFET

例示的一実施例によれば、基板上に位置するBiFETは、基板の上に位置するエミッタ層部分を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFETをさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。  (もっと読む)

(もっと読む)

半導体部品および半導体部品の製造方法

半導体部品は、半導体基板(110)と、半導体基板の上方のエピタキシャル半導体層(120)と、エピタキシャル半導体層内のバイポーラトランジスタ(770、870)と、エピタキシャル半導体層内の電界効果トランジスタ(780、880)とを含む。エピタキシャル半導体層の一部によって、バイポーラトランジスタのベースと電界効果トランジスタのゲートとが形成され、エピタキシャル半導体層のその一部は実質的に均一なドーピング濃度を有する。同じまたは他の実施形態においては、エピタキシャル半導体層の異なる部分によって、バイポーラトランジスタのエミッタと電界効果トランジスタのチャネルとが形成され、エピタキシャル半導体層のその異なる部分はエピタキシャル半導体層の一部の実質的に均一なドーピング濃度と同じかまたは異なる実質的に均一なドーピング濃度を有する。  (もっと読む)

(もっと読む)

窒化物半導体装置

HEMTは、シリコン基板(1)、窒化物半導体から成るバッファ領域(2)、窒化物半導体領域(3)、ソース電極(4)、ドレイン電極(5)、ゲート電極(6)、絶縁膜(7)、導体膜(8)及びコンタクト電極(9)を有している。バッファ領域(2)はシリコン基板(1)の上に複数回繰返して成長されたAINから成る第1の層(13)とGaNから成る第2の層(14)とから成る。半導体領域(3)は電子走行層(15)と電子供給層(16)とを有している。バッファ領域(2)及び半導体領域(3)の側面(17)は傾斜している。この傾斜側面(17)に絶縁膜(7)を介して導体膜(8)が対向している。導体膜(8)はコンタクト電極(9)を介してシリコン基板(1)に接続され、側面(17)における漏れ電流の低減に寄与する。 (もっと読む)

シングルゲートまたはマルチゲートフィールドプレート製造

電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセス。本製造プロセスのは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。  (もっと読む)

(もっと読む)

スプリットチャネル高電子移動度トランジスタデバイス

トランジスタ構造体であって、ガリウムヒ素(GaAs)半導体基板と、インジウムアルミニウムガリウムヒ素(InAlGaAs)格子整合層と、格子整合層の上に配設されるインジウムアルミニウムヒ素(InAlAs)バリア層と、バリア層上に配設されるInyGa1−yAs下部チャネル層であって、yは下部チャネル層のIn含有量のモル分率である、InyGa1−yAs下部チャネル層と、下部チャネル層上に配設されるInxGa1−xAs上部チャネル層であって、xは上部チャネル層のIn含有量のモル分率であり、xはyと異なる、InxGa1−xAs上部チャネル層と、InxGa1−xAs上部チャネル層上のInAlAsショットキー層とを有するトランジスタ構造体。下部チャネル層は、上部チャネル層のバンドギャップより大きいバンドギャップを有し、下部チャネル層は、上部チャネル層のバルク電子移動度より低いバルク電子移動度を有する。 (もっと読む)

化合物半導体層の表面処理方法及び半導体装置の製造方法

【課題】窒素を含む化合物半導体層の表面に生じた、エッチングによるダメージを除去あるいは軽減し、ゲート電極に良好なショットキ特性を有する半導体装置を形成する。

【解決手段】ドライエッチングにより、第1化合物半導体層22のゲート電極形成予定領域36の表面を露出するとともに、コンタクト層32を形成する。次いで、この第1化合物半導体層22の露出した表面に対するアニール処理を行う。前述のドライエッチングの際に第1化合物半導体層22の表面に生じたダメージを、窒素プラズマを用いた表面処理を行うことにより、良好な電気特性をもつ第1化合物半導体層22の表面を形成する。この窒素プラズマを用いた表面処理を行った第1化合物半導体層22の表面上にゲート電極38を形成し、良好なショットキ特性を有するゲート電極を具えたリセス型HEMT10を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長の短いゲート電極を有し、しかも低抵抗で高周波特性が優れている半導体装置およびその製造方法を提供する。

【解決手段】少なくともノンドープInGaP層又はノンドープInAlGaP層からなる上層半導体層12と、この上層半導体層直下にGaAs層またはAlGaAs層からなる下層半導体層11を含む半導体基板に、上層半導体層表面から上層半導体層への浸入が、下層半導体層で略停止するショットキーゲート電極15と、このショットキーゲート電極部に接続して第1の電極の抵抗を低減する第2の電極部16からなるT字型ゲート電極を形成する。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】耐圧性、特性安定性に優れ、ゲートリーク電流が低減されたヘテロ接合型電界効果トランジスタを提供すること。

【解決手段】半導体基板上にバッファ層と、チャネル層と、スペーサ層と、キャリア供給層と、ショットキーバリア層と、高濃度不純物ドープキャップ層とが順次堆積され、ソース電極及びドレイン電極がキャップ層表面に形成され、ソース電極とドレイン電極の間のキャップ層にショットキーバリア層に達する開口部が形成され、開口部に露出したショットキーバリア層表面にゲート電極が形成されているヘテロ接合型電界効果トランジスタであって、キャップ層が複数の細線で構成され、細線間はショットキーバリア層が露出し、ソース電極及びドレイン電極が、細線と細線間に露出したショットキーバリア層との両方に接触していることを特徴とするヘテロ接合型電界効果トランジスタを構成する。

(もっと読む)

1,721 - 1,734 / 1,734

[ Back to top ]