Fターム[5F102GM06]の内容

接合型電界効果トランジスタ (42,929) | ゲート下介在層(ゲートメタル電極底面とチャネル層表面間に介在する層) (3,125) | 単一半導体層 (2,140) | 3−5族 (2,057) | GaAlAs (261)

Fターム[5F102GM06]に分類される特許

1 - 20 / 261

評価方法

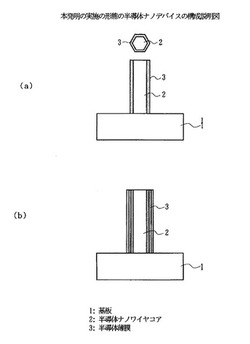

半導体ナノデバイス

【課題】 半導体ナノデバイスに関し、基板上における臨界膜厚を超えた厚さの歪のある半導体薄膜を形成してデバイス領域とする。

【解決手段】 長径が1μm未満の半導体ナノワイヤコアと、前記半導体ナノワイヤコアの側壁に形成され、前記半導体ナノワイヤコアの構成材料との歪εが1%以上異なる半導体材料からなり、且つ、膜厚t〔nm〕と歪ε〔%〕とが、

−0.720+0.0988ε−1.2<t≦−0.705+0.227ε−1.2

の関係を満たす少なくとも一層の半導体薄膜との接合界面或いは前記半導体薄膜同士の接合界面を機能領域とする。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

半導体装置

【課題】電子が第1励起準位に存在する割合が増えても、量子井戸層の中の電子の有効質量が軽くなる井戸層にできるだけ多くの電子が存在するようにして、より一層の高速化を実現する。

【解決手段】半導体装置を、基板10の上方に設けられた第1半導体層11と、第1半導体層11の上側に接する電子走行層24と、電子走行層24の上側に接する第2半導体層17(25)とを備えるものとし、電子走行層を24、第1井戸層13、中間障壁層14、第2井戸層15を順に積層させた構造を含む2重量子井戸層とし、中間障壁層14の伝導帯のエネルギーが、第1半導体層11及び第2半導体層17(25)の伝導帯のエネルギーよりも低くなり、第1井戸層13及び第2井戸層15の中に基底準位が形成され、2重量子井戸層の中に第1励起準位が形成されるようにする。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

電子デバイス

【課題】改良されたプレーナデバイスを提供する。

【解決手段】電子デバイスは、移動電荷キャリアを支持する基板と、該基板面上に形成されてその両側に第1および第2の基板領域を定義し、該第1および第2の基板領域は該絶縁体によって定義される細長いチャネルによって接続され、該チャネルは該第1の領域から該第2の領域への基板内の電荷キャリア流路を提供し、該第1および該第2の基板領域間の伝導度は、この2つの領域間の電位差に依存する。該基板は有機材料とすることができる。移動電荷キャリアは、0.01cm2/Vs〜100cm2/Vsの範囲の移動度を有することができ、該電子デバイスはRFデバイスであってもよい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体パッケージ内における半導体素子の位置ずれを抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、凸部23が形成されたパッケージ基板11、導電性の接着剤25、およびパッケージ基板11上に実装された半導体素子14、を具備する。パッケージ基板11は、少なくとも2箇所に凸部23が形成された基板である。導電性の接着剤25は、凸部23を含むパッケージ基板11上に形成される。パッケージ基板11上に実装される半導体素子14は、各凸部23に係合する複数のバイアホール24を有している。さらに、半導体素子14は、少なくとも2箇所のバイアホール24が、各凸部23に接着剤25を介して係合するようにパッケージ基板11上に実装される。

(もっと読む)

トランジスタ素子

【課題】単体構造のHBTデバイスと同等の信頼性を得る。

【解決手段】化合物半導体からなる、高電子移動度トランジスタ(HEMT)とヘテロバイポーラトランジスタ(HBT)とを、同一基板上に重ねてエピタキシャル成長した多層構造のトランジスタ素子において、エピ層として内在するインジウムガリウムリン層(InGaP)のバンドギャップエネルギを1.91eV以上にすることを特徴とする。

(もっと読む)

トランジスタ素子

【課題】n型不純物としてTeを用いたノンアロイ層を有していても、ベース電流、コレクタ電流のリーク電流が少ないトランジスタ素子を提供する。

【解決手段】基板11と、基板11上に設けられた高電子移動度トランジスタ構造層28と、高電子移動度トランジスタ構造層28上に設けられたヘテロバイポーラトランジスタ構造層29とを備えたトランジスタ素子10において、ヘテロバイポーラトランジスタ構造層29のノンアロイ層26,27は、n型不純物としてTeがドーピングされており、n型不純物濃度が1.0×1019cm-3以上2.0×1019cm-3以下にされているものである。

(もっと読む)

III−窒化物デバイスの製造方法およびIII−窒化物デバイス

【課題】高耐圧なIII−窒化物デバイスを提供する。

【解決手段】半導体基板1、基板1上の活性層のスタックであって、それぞれの層はIII−窒化物材料を含むスタック2−5、スタック2−5上のゲート8、ソース9およびドレインコンタクト10、および基板1の裏側(活性層のスタックに接する側に対向する側)から基板1に接する活性層のスタックの下層まで基板中を延びるトレンチであって、トレンチはドレイン領域を完全に囲み、ドレインに向かうゲート領域の端と、ゲートに向かうドレイン領域の端との間に配置され、基板のドレイン領域は本質的に半導体材料から形成されるような幅を有するトレンチを含むIII−窒化物デバイス。

(もっと読む)

III−V族化合物半導体エピタキシャルウエハ

【課題】充分な選択比を備え、また、除去が比較的容易なエッチングストッパ層を得る。

【解決手段】GaAs基板10上に設けられた高電子移動度トランジスタ構造20と、高電子移動度トランジスタ構造20の上に設けられたヘテロ接合バイポーラトランジスタ構造40と、を備え、高電子移動度トランジスタ構造20とヘテロ接合バイポーラトランジスタ構造40との間には、As濃度が1.0×1016atoms/cc以上1.0×1021atoms/cc以下のInGaAsP層からなるエッチングストッパ層30を備える。

(もっと読む)

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ

【課題】オン抵抗の低いストッパー層を有するIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板8上に、GaAs層、AlGaAs層からなるバッファ層9、n型不純物を含有するAlGaAs層又はInGaP層若しくはSiプレナードープ層からなる電子供給層10、InGaAs層からなるチャネル層12、ノンドープ又は低濃度n型不純物を含有するGaAs層又はAlGaAs層からなるショットキー層14、ノンドープ又は低濃度n型不純物を含有するInGaP層からなるストッパー層15、n型不純物を含有するGaAs層からなるキャップ層16を積層したHEMT構造18を有するIII−V族化合物半導体エピタキシャルウェハ17において、ストッパー層15におけるInGaP中のAsが占めるV族原子分率が15%以下であるものである。

(もっと読む)

電界効果トランジスタ、半導体スイッチ回路、および通信機器

【課題】半導体スイッチのチップサイズを大きくすることなく、高調波特性を改善する。

【解決手段】FET1において、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられる複数のソース電極6を有するソース配線3と、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられて複数のソース電極6に対して並列方向に交互に配置される複数のドレイン電極7を有するドレイン配線4と、化合物半導体基板上に形成され、少なくとも前記並列方向に互いに隣り合うソース電極6とドレイン電極7との電極間に位置する部分を有するゲート配線5と、ゲート配線5が形成される領域にてゲート配線5下に形成され、複数のソース電極6と複数のドレイン電極7との各電極間に独立して設けられる複数の埋め込みゲート層8とを備えた。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

1 - 20 / 261

[ Back to top ]