Fターム[5F102GR01]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 素子形成にあたり、結晶軸、面方位を選択したもの (450)

Fターム[5F102GR01]に分類される特許

141 - 160 / 450

窒化物半導体装置

【課題】シリコン基板の上に形成され、優れた高周波特性を有する窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、シリコン基板101と、シリコン基板101の上に形成された窒化物半導体からなるバッファ層102と、バッファ層102の上に形成された窒化物半導体からなる能動層103とを備えている。バッファ層は、シリコン基板101と接して形成された第1の層121と、第1の層121及び能動層103と接して形成された第2の層122とを含む。第1の層121と第2の層122との界面における炭素濃度は、1×1019原子/cm3以上且つ1×1021原子/cm3以下であり、第2の層122は、炭素濃度が第1の層121と接する部分において最も高く、能動層103と接する部分において最も低い。

(もっと読む)

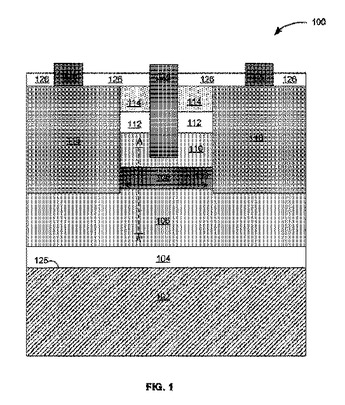

低リークGANMOSFET

エンハンスメント・モードGaN MOSFET(100)が、AlGaN(又はInAlGaN)障壁層(118)上のSiO2/Si3N4ゲート絶縁層(124)を用いて形成される。SiO2/Si3N4ゲート絶縁層(124)のSi3N4部分(120)は、ゲート絶縁層(124)と障壁層(118)との間の接合での界面準位の形成を低減させ、SiO2/Si3N4ゲート絶縁層(124)のSiO2部分(122)は、漏れ電流を著しく低減させる。

(もっと読む)

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

トランジスタ

【課題】キャリア密度の精密な制御が可能な半導体装置を提供する。

【解決手段】単結晶基板105と、対称性6mmの六方晶系結晶から構成され、単結晶基板105上に形成された半導体層101と、半導体層101上に形成されたソース電極102、ドレイン電極103及びゲート電極104とを備え、半導体層101を構成するGaN層106及びAlGaN層107の主面は六方晶系結晶のC軸を面内に含み、半導体層101内のチャネル領域101aの長手方向は六方晶系結晶のC軸と平行である。

(もっと読む)

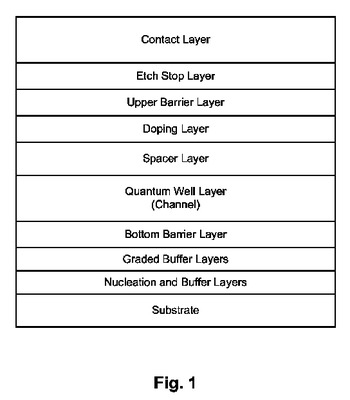

集積回路デバイスに歪みを与える技術及び構成

本開示の実施形態により、例えば横型電界効果トランジスタなどの集積回路デバイスに歪みを与える技術及び構成が提供される。集積回路デバイスは、半導体基板と、該半導体基板と結合された第1のバリア層と、第1のバリア層に結合された、第1の格子定数を持つ第1の材料を有する量子井戸チャネルと、量子井戸チャネルに結合されたソース構造とを含む。ソース構造は、第1の格子定数とは異なる第2の格子定数を持つ第2の材料を有し、量子井戸チャネルに歪みを与える。その他の実施形態も開示される。  (もっと読む)

(もっと読む)

窒化物系化合物半導体基板の製造方法及び窒化物系化合物半導体自立基板

【課題】反り返りがなく、面内のオフ角のばらつきが小さな窒化物系化合物半導体層を再現性よく成長させることができる窒化物系化合物半導体基板の製造方法、及び半導体デバイスの作製に好適な窒化物系化合物半導体自立基板を提供する。

【解決手段】成長用基板上に窒化物系化合物半導体層をエピタキシャル成長させる窒化物系化合物半導体基板の製造方法において、成長用基板として、(011)面を≒[010]方向に0〜2°(0°を除く)のオフ角で傾斜させた主面を有する希土類ペロブスカイト基板を用いる。

(もっと読む)

量子井戸トランジスタへのコンタクトを形成する方法

半導体へテロ構造内に形成されたデバイスへの低抵抗自己整合コンタクトを供する方法が開示されている。当該方法はたとえば、III-V族及びSiGe/Ge材料系において作製される量子井戸トランジスタのゲート、ソース、及びドレイン領域へのコンタクトを形成するのに用いられてよい。ゲートへのソース/ドレインコンタクト間に比較的大きな空間を生成してしまう従来のコンタクト作製処理の流れとは異なり、当該方法により供されたソースとドレインのコンタクトは自己整合され、各コンタクトは、ゲート電極に対して位置合わせされ、かつ、スペーサ材料を介して前記ゲート電極から分離される。  (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

エピタキシャルウェハ、それを用いたトランジスタ、発光素子、およびエピタキシャルウェハの製造方法

【課題】反りの少ないエピタキシャルウェハを提供する。

【解決手段】エピタキシャルウェハは、基板1と窒化物半導体4,5,6の間に形成されたアルミニウム層2と、アルミニウムを陽極酸化して形成したアルミニウムの陽極酸化(陽極酸化Al)層3によって、熱膨張係数差に起因した応力を緩和することで、ウェハのそりを押さえることが可能となる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるようにする。

【解決手段】エピタキシャル成長を行わず、素子を構成する各領域をイオン注入のみによって形成すると共に、SiC基板1としてオフ角を有しないオン基板を用いる。これにより、イオン注入領域を活性化するための熱処理によってバンチングが発生しないようにできる。したがって、エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるSiC半導体装置とすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】オーミック電極とオーミックリセス部とのコンタクト抵抗を低減した窒化物半導体素子および窒化物半導体素子の製造方法を提供する。

【解決手段】窒化物半導体素子400は、基板401上に形成された第1の窒化物半導体層402と、第1の窒化物半導体層402上に形成され、第1の窒化物半導体層402と比べてバンドギャップが大きい第2の窒化物半導体層403と、少なくとも第2の窒化物半導体層403に形成されたオーミックリセス部405と、オーミックリセス部405に接触して設けられたオーミック電極407とを備え、オーミックリセス部405は、オーミック電極407と接触する面の少なくとも一部に凹凸構造を有する。

(もっと読む)

高電圧耐久III族窒化物半導体デバイス

【課題】高電圧の印加時に、電荷キャリアを導電領域内に抑制して、高電圧耐久性を呈する、HEMTのようなIII族窒化物半導体デバイスを提供する。

【解決手段】高電圧耐久III族窒化物半導体デバイスは、(100)シリコン層14、該(100)シリコン層14上の絶縁体層18、及び該絶縁体層18上のP型導電性の(111)シリコン層16を有する支持基板を備える、高電子移動度トランジスタ(HEMT)を備える。高電圧耐久HEMTは、P型導電性の(111)シリコン層16上に形成したIII族窒化物半導体本体12であって、HEMTのヘテロ接合を形成する、III族窒化物半導体本体も備える。

(もっと読む)

半導体装置

【課題】ソース・ゲート間およびドレイン・ゲート間に発生する2次元電子ガスの濃度を最適にしたまま、オン抵抗を低くして、消費電力の低い半導体装置を提供する。

【解決手段】第2のAlGaN層6のAlの組成比は、第1のAlGaN層5のAlの組成比よりも大きい。このため、ゲート電極8に電圧を印加したとき、GaN層3の凹溝30の内面の側面31と第2のAlGaN層6との第1の界面S1に2次元電子ガスを発生させつつ、第2のAlGaN層6における凹溝30の内面の側面31に平行な部分と絶縁層7との第2の界面S2に2次元電子ガスを発生させることを抑制できる。

(もっと読む)

III族窒化物系半導体素子およびIII族窒化物系半導体素子の製造方法

【課題】低コストで製造することができ、かつ、高い絶縁破壊耐圧を有するIII族窒化

物系半導体素子、およびIII族窒化物系半導体素子の製造方法を提供する。

【解決手段】シリコン層、絶縁層、および表面にシリコンからなる複数の核領域と前記複

数の核領域の間を埋める絶縁領域を有する複合層がこの順に形成された基板と、前記基板

上に形成されたIII族窒化物系半導体からなるバッファ層と、前記バッファ層上に形成

されたIII族窒化物半導体からなる動作層と、前記動作層上に形成された第1の電極お

よび第2の電極とを備え、前記核領域のそれぞれの最大幅L1が、前記第1の電極および

前記第2の電極の間の距離L2よりも小さいことを特徴とする。

(もっと読む)

窒化物系ダイオード

【課題】高耐圧でかつ低オン電圧動作が可能な窒化物系ダイオードを提供する。

【解決手段】窒化物系ダイオード10は、シリコン基板11の(111)面上に形成されたバッファ層12と、アンドープのGaNからなるチャネル層13と、チャネル13層上に形成されたアンドープのAlGaNからなる電子供給層14と、電子供給層14上に形成されたカソード電極15およびアノード電極16とを備える。窒化物系ダイオード10はさらに、電子供給層14を、チャネル層13に達する深さまで部分的に除去したメサ18を備え、メサ18の一方の側面部18aにアノード電極16が接触している。アノード電極16がメサ18の側面部18aに接触することで、アノード電極16と2次元電子ガス層17とが電気的に接続されている。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

141 - 160 / 450

[ Back to top ]