Fターム[5F102GR01]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 素子形成にあたり、結晶軸、面方位を選択したもの (450)

Fターム[5F102GR01]に分類される特許

161 - 180 / 450

ガリウム窒化物又は他の窒化物ベースの半導体デバイスの裏側応力補償

半導体基板(102)の第1の側の上に応力補償層(104)を形成すること(302)と、前記基板の第2の側の上にIII族窒化物層(108a、108b、110、112)を形成すること(304)を含む方法。III族窒化物層により前記基板上につくられる応力が、前記応力補償層により前記基板上につくられる応力によって少なくとも部分的に低減される(306)。前記応力補償層を形成することが、非晶質又は微結晶材料から応力補償層を形成することを含み得る。また、この方法は、前記基板の前記第2の側の上の一つ又は複数の層(106〜114)の後続の形成の間、前記非晶質又は微結晶材料を結晶化することを含み得る。前記非晶質又は微結晶材料の結晶化は、前記III族窒化物層の後続の形成の間及び/又はアニールプロセスの間に成され得る。前記非晶質又は微結晶材料は、前記基板上につくる応力が全くないか又は量が小さく、前記結晶化した材料が前記基板上に一層大きな応力をつくり得る。

(もっと読む)

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

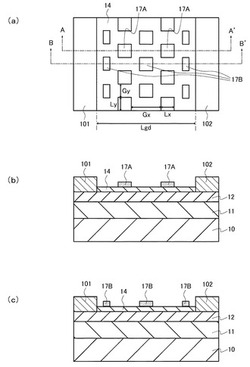

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス、及びその製造方法

【課題】III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス及びその製造方法を提供する。

【解決手段】III−V族材料のエネルギーレベルの密度とドーピング濃度をIII−V族材料とIV族材料のヘテロエピタキシと素子の構造設計によって高める。本発明の方法は、基板100上にダミーゲート材料層を堆積し、フォトリソグラフィでダミーゲート材料層にダミーゲートを区画することと、ダミーゲートをマスクとして使用し、セルフアライン型イオン注入によってドーピングを行い、高温で活性化を行い、ソース−ドレイン108を形成することと、ダミーゲートを除去することと、ソース−ドレインのペアの間の基板にエッチングで凹陥部を形成することと、凹陥部にエピタキシャル法によりチャネル含有スタック素子112を形成することと、チャネル含有スタック素子上にゲート120を形成することと、を含む。

(もっと読む)

半導体装置

【課題】GaN電子走行層、AlGaN電子供給層、およびGaNキャップ層が順次積層された半導体装置において、高周波数動作および高出力動作を実現することが可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に順次積層されたGaN電子走行層12、AlGaN電子供給層14、およびGaNキャップ層16と、GaNキャップ層16上に形成されたゲート電極18と、ゲート電極18の両側であって、AlGaN電子供給層14上に形成されたソース電極20およびドレイン電極22と、ゲート電極18とソース電極20との間のGaNキャップ層16に形成された第1の凹部30と、を具備し、第1の凹部30が有する底面32下におけるGaNキャップ層16の厚さは、ゲート電極18下におけるGaNキャップ層16の厚さに比べて薄い半導体装置である。

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

III族窒化物積層基板

【課題】割れの発生を抑制することに加え、結晶性も向上させたIII族窒化物半導体を提供する。

【解決手段】シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ前記第1超格子積層体の総厚が1μmを超えることを特徴とする。

(もっと読む)

集積半導体基板構造の製造方法

【課題】GaN素子およびCMOS素子の両方を備えた集積回路を製造するための改善した方法を提供する。

【解決手段】集積半導体基板構造100は、基板11と、GaNヘテロ構造20と、半導体基板層30とを備える。GaNヘテロ構造20は、第1素子エリアに存在し、少なくとも部分的に保護層8で覆われている。半導体基板層30は、CMOS素子の区画のための第2素子エリアに存在する。GaNヘテロ構造20および半導体基板層30の少なくとも1つが、基板11の少なくとも1つの溝内をエピタキシャル成長して形成され、GaNヘテロ構造20および半導体基板層30は横方向に並置される。

(もっと読む)

半導体素子およびその製造方法

【課題】より高いブレークダウン電圧に適した半導体素子構造およびその製造方法を提供する。

【解決手段】半導体基板構造(100)は、半導体基板(1)と、半導体基板(1)の上部にGaNタイプの層スタック(20)とを備える。GaNタイプ層スタック(20)は、少なくとも1つのバッファ層(21,22)と、第1活性層(2)と、第2活性層(3)とを備え、第1活性層と第2活性層の界面において、能動素子領域が規定可能である。半導体基板(1)は、絶縁層(12)の上に存在しており、所定のパターンに従って溝(14)を規定するようにパターン化され、そのパターンは、こうした能動素子領域の下地となる少なくとも1つの溝(14)を含み、前記溝(14)は、絶縁層(12)から、GaNタイプ層スタック(20)の少なくとも1つのバッファ層(21,22)の中まで延びて、前記少なくとも1つのバッファ層(22)の範囲で過成長しており、第1および第2活性層(2,3)は、少なくとも能動素子領域の範囲で連続している。

(もっと読む)

窒化物半導体デバイス

【課題】 ウエハ−プロセスで基板の上に製造された素子単位をチップ分離する際に研磨、切断などの工程を減らすことができ、基板を繰り返し使用できる窒化物半導体デバイス作製方法によって作製したデバイスを提供する。

【解決手段】 閉曲線をなす結晶成長速度の遅い欠陥の集合した欠陥集合領域Hと結晶成長速度の速い低欠陥の領域ZYの位置が予め決まっている窒化物半導体欠陥位置制御基板Sを用い、低欠陥領域ZYにデバイスの内部が、欠陥集合領域Hに境界線が来るように窒化ガリウム基板の上に窒化物半導体層(上層部B)をエピタキシャル成長させ、レーザ照射或いは機械的手段で欠陥位置制御基板Sと成長層(上層部B)を上下方向横方向に同時分離し、基板は繰り返し使用する。作製されたデバイスは端面が成長によるファセットで形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低く、移動度を高く、かつピンチオフ特性を良好にした上で、ドレイン電圧を増大させてもキンク現象が生じない、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】開口部28が設けられたGaN系積層体15と、チャネルを含む再成長層27と、ゲート電極Gと、ソース電極Sと、ドレイン電極Dとを備え、再成長層27は電子走行層22および電子供給層26を含み、GaN系積層体には再成長層に開口部でその端面が被覆されるp型GaN層6が含まれ、そのp型GaN層にオーミック接触するp部電極11を備えることを特徴とする。

(もっと読む)

高電子移動度トランジスタ、エピタキシャル基板、及び高電子移動度トランジスタを作製する方法

【課題】ノーマリオフ特性を実現する高電子移動度トランジスタを提供する。

【解決手段】チャネル層25が第1のバリア層27上に設けられると共に第1のバリア層27と第1のヘテロ接合33を成す。また、チャネル層25は圧縮歪みを内包して、チャネル層25のピエゾ電界PZC2は支持基体13から第1のバリア層27への方向に向く。第1のヘテロ接合33がIII族窒化物領域23のc軸方向に対して40度以上85度以下及び140度以上180度未満の角度範囲の傾斜角αで傾斜した基準軸ベクトルに垂直な平面に沿って延在するとき、ゲート電極19直下におけるチャネル層25におけるピエゾ電界PZC2の大きさをc面上のトランジスタにおけるピエゾ電界の大きさに比べて小さくできて、有限な大きさのピエゾ電界を残しながらノーマリオフ特性が実現される。

(もっと読む)

ヘテロ接合トランジスタ、及びヘテロ接合トランジスタを作製する方法

【課題】チャネル層内の抵抗の不均一を避けることを可能にする構造を有するヘテロ接合トランジスタを提供する。

【解決手段】半導体積層15が、半極性を示すIII族窒化物主面13a上に設けられ、半導体積層15が主面13aに到達する開口16を有する。開口16の側面16aは、III族窒化物半導体のa面に対して大きな角度を成すと共にIII族窒化物半導体のm面に対しても大きな角度を成して、III族窒化物半導体のc面に非常に近い面から構成される。開口16の側面16aの傾斜角は、m面やa面よりもc面に近い。この開口16の側面16aにドリフト層17及びチャネル層19が成長されるので、その成長中に不可避的に取り込まれる不純物量を小さくできる。これ故に、ドリフト層17及びチャネル層19における抵抗の不均一を避けることができる。

(もっと読む)

電子スピン共鳴生成装置および電子スピン共鳴の生成方法

【課題】外部磁場を用いることなく、電子スピン共鳴を生じさせること。

【解決手段】本発明は、半導体からなり、電子の走行方向に対し交差する方向に第1のスピン軌道相互作用に起因した一定の第1有効磁場が生じるチャネル18と、前記チャネル内に前記第1有効磁場に起因して生じた前記電子のスピン分離エネルギに対応する周波数の交流電界を生じさせることにより、前記チャネル内に前記電子の走行方向および前記第1有効磁場の方向に交差する方向に第2スピン軌道相互作用に起因した交流の第2有効磁場を発生させる電極24と、を具備する電子スピン共鳴生成装置である。

(もっと読む)

半導体素子用エピタキシャル基板、半導体素子、および半導体素子用エピタキシャル基板の製造方法

【課題】反りが抑制された、半導体素子用のエピタキシャル基板を提供する。

【解決手段】下地基板1の上にIII族窒化物層群を積層形成した半導体素子用のエピタキシャル基板10において、III族窒化物層群が、少なくとも2層以上のIII族窒化物層が積層された緩衝層2と、Inx1Aly1Gaz1N(0≦x1≦1、0≦y1≦1、0<z1≦1、x1+y1+z1=1)なる組成のIII族窒化物からなるチャネル層3と、Inx2Aly2Gaz2N(0≦x2≦1、0<y2≦1、0≦z2≦1、x2+y2+z2=1)なる組成のIII族窒化物からなる障壁層4と、を備え、緩衝層2の少なくとも1つが、格子空孔を有する格子空孔内在層23であるようにする。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】ノーマリオフでオン抵抗の低いHFETを実現すること。

【解決手段】HFET100は、第1キャリア走行層103上の互いに離間した2つの領域上に、2つに分離して形成されたノンドープのGaNからなる第2キャリア走行層104と、2つの分離した第2キャリア走行層104上にそれぞれ位置するAlGaNからなるキャリア供給層105を有している。第2キャリア走行層104とキャリア供給層105は、第1キャリア走行層103上に選択的に再成長させて形成した層である。第2キャリア走行層104とキャリア供給層105のヘテロ接合界面110は平坦性が高く、そのヘテロ接合界面110近傍は再成長に伴って混入した不純物はほとんど見られないため、2DEGの移動度を低下させることがなく、オン抵抗が低減されている。

(もっと読む)

電界効果トランジスタ

【課題】十分に大きな電流密度を得ることができるノーマリオフ型の窒化物半導体からなる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】基板101上にAlNバッファ層102、アンドープGaN層103、アンドープAlGaN層104、p型GaN層105、高濃度p型GaN層106が順に形成され、ゲート電極111が高濃度p型GaN層106とオーミック接合する。アンドープAlGaN層104の上にはソース電極109及びドレイン電極110が設けられる。アンドープAlGaN層104とアンドープGaN層との界面で発生する2次元電子ガスとp型GaN層105とによって生じるpn接合がゲート領域に形成されるのでゲート電圧を大きくすることができる。

(もっと読む)

半導体素子用エピタキシャル基板、ショットキー接合構造、およびショットキー接合構造の漏れ電流抑制方法

【課題】ショットキー接合の逆方向特性についての信頼性が高い半導体素子を実現可能な、半導体素子用のエピタキシャル基板を提供する。

【解決手段】下地基板1の上にIII族窒化物層群を(0001)結晶面が基板面に対し略平行となるよう積層形成した半導体素子用エピタキシャル基板10が、Inx1Aly1Gaz1N(x1+y1+z1=1、z1>0)なる組成の第1のIII族窒化物からなるチャネル層3と、Inx2Aly2N(x2+y2=1、x2>0、y2>0)なる組成の第2のIII族窒化物からなる障壁層5とを備え、第2のIII族窒化物が、短距離規則度パラメータαが0<α<1の範囲をみたす短距離規則混晶であるようにする。

(もっと読む)

電界効果トランジスタの製造方法

【課題】ゲート長が短い電界効果トランジスタを低コストで製造できる電界効果トランジスタの製造方法を提供すること。

【解決手段】基板上に、窒化物系化合物半導体からなるチャネル層および該チャネル層上に積層した上部層を含む半導体層を形成する工程と、半導体層の一部領域を少なくとも上部層からチャネル層に到る深さまでエッチングして、該チャネル層の表面の一部を底面部とし、エッチングによって露出した半導体層の側面を側壁部とする段差部を形成する工程と、段差部を含む半導体層の表面を覆うようにマスク層を形成し、該マスク層をエッチバックして該段差部のマスク層を残留させたマスク部を形成する工程と、イオン注入法によって、底面部のマスク部を除く領域にコンタクト領域を形成する工程と、マスク部を除去した後に、少なくとも段差部の底面部と側壁部とを覆うようにゲート絶縁膜およびゲート電極を順次形成する工程と、を含む。

(もっと読む)

フィールドプレートを有する半導体デバイス

III−N材料層と、III−N材料層の表面上に設けられた絶縁体層と、III−N材料層から反対側の絶縁体層上記に設けられたエッチング停止層と、絶縁体層から反対側のエッチング停止層上に設けられた電極画定層とを備えるIII−Nデバイスを開示する。電極画定層内には、凹部が形成される。凹部内には、電極が形成される。絶縁体は、特に電極とIII−N材料層との間で、正確に制御された厚さを有することができる。 (もっと読む)

半導体装置及びその製造方法

【課題】チャネルにおけるキャリア移動度が高く、ノーマリオフを実現する半導体装置を提供する。

【解決手段】 n型GaNキャップ層18の開口部28との界面(開口部境界面)は、複数のほぼ鉛直な面S1と、各面S1の間を補完するように形成された傾斜した面S3により構成されている。傾斜面はドライエッチングにより形成し、異方性エッチングによりダメージ層を除去する。縦型FET1では、GaN基板10上に、六方晶のGaN、AlGaNを、{ 0 0 0 1}面を成長面として、エピタキシャル成長させており、n型GaNキャップ層18における鉛直な面S1は、{ 1-1 0 0}面(m面)となる。m面は、C面とは異なり無極性面であるので、m面を成長面として、GaN電子走行層22、AlGaN電子供給層26を再成長させると、ピエゾ電荷等の分極電荷がAlGaN/GaNヘテロ界面に生じない。よって、縦型FET1においては、よりノーマリオフに近づけることが可能となる。

(もっと読む)

161 - 180 / 450

[ Back to top ]