Fターム[5F102GR01]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 素子形成にあたり、結晶軸、面方位を選択したもの (450)

Fターム[5F102GR01]に分類される特許

61 - 80 / 450

パワー半導体素子

【課題】窒化物化合物半導体を用いたパワーダイオード、パワーMOSFET等のパワー

半導体素子について、クラックフリーで形成されて従来よりも厚い窒化物化合物半導体層

を使用して耐圧を向上することである。

【解決手段】シリコン基板1上に厚さ10μm以上の凸状に選択成長された窒化物化合物

半導体からなるキャリア移動層3と、キャリア移動層3上に形成された電極4とを有し、

1つのパワー半導体素子は1つのキャリア移動層3から構成されている。

(もっと読む)

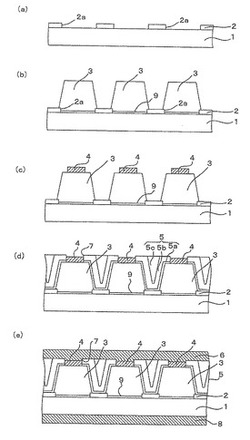

ノーマリオフ型パワーJFETの製造方法

【課題】SiC系JFETにおいて、トレンチゲート領域間を高精度に制御するため、ソース領域内にゲート領域を形成する必要がある。これにより増加するソース領域、ゲート領域間高濃度PN接合による接合電流を削減できる半導体装置を提供する。

【解決手段】ノーマリオフ型パワーJFETの製造方法であって、N型SiC1sの表面に、Nエピタキシャル下層1ea、中層1eb、上層1ec等複数層を形成し、表面には複数のソース層9、及びPゲート領域4が設けられる。ゲート領域はアクティブ領域3の外端部に接するように、下層、中層、上層のPエッジターミネーション領域7a、7b、7cが設けられる。裏側種面には、高濃度ドレイン層8が形成される。

(もっと読む)

半導体素子用のエピタキシャル基板、および半導体素子用エピタキシャル基板の製造方法

【課題】高耐電圧性を有するとともにp型不純物の拡散による結晶品質の劣化が好適に抑制された、半導体素子用のエピタキシャル基板を提供する。

【解決手段】(111)方位の単結晶シリコンである下地基板1の上に、前記下地基板の基板面に対し(0001)結晶面が略平行となるようにIII族窒化物層群を形成してなる半導体素子用のエピタキシャル基板10が、組成の相異なる第1単位層31と第2単位層32とを繰り返し交互に積層してなる組成変調層3と、組成変調層の上に形成され、Alを含むIII族窒化物からなる中間層5と、を含む単位構造体を複数積層してなるバッファ層8と、バッファ層の直上に形成されたチャネル層9aと、チャネル層の上に形成されたバリア層9bと、を備え、バッファ層に含まれる複数の前記中間層のうちの少なくとも1つにp型不純物が意図的に導入されてなり、隣接層に第1の層から拡散したp型不純物が存在する、ようにする。

(もっと読む)

高電子移動度トランジスタ(HEMT)

【課題】高周波特性を改善する。

【解決手段】III族窒化物系高電子移動度トランジスタ(HEMT)20は、GaNバッファ層26を備えており、Ganバッファ層26上にAlyGa1−yN(y=1又は≒1)層28がある。AlxGa1−xN(0≦x≦0.5)バリア層30が、GaNバッファ層26の反対側でAlyGa1−yN層28上にあり、該層28のAl濃度は、バリア層30よりも高い。GaNバッファ層26とAlyGa1−yN層28との間の界面に2DEG38が形成されている。バリア層30上に、ソース、ドレイン、及びゲート・コンタクト32、34、36が形成されている。また、AlyGa1−yN層28の反対側において、バッファ層26に隣接する基板22も含み、GaNバッファ層26と基板22との間に、核生成層24を含むことができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体の表面の酸化物を含む不純物を、エッチングあるいは、他の層を積層する前に除去する。

【解決手段】第1の半導体層110の少なくとも一部に接し、第1の半導体層110に含まれる不純物の固溶度が、第1の半導体層110より高い第1の犠牲層を形成する第1犠牲層形成工程と、第1の犠牲層および第1の半導体層をアニールするアニール工程と、第1の犠牲層をウェットプロセスで除去する除去工程と、第1の半導体層の少なくとも一部を覆う絶縁層120を形成する工程および第1の半導体層の一部をエッチングする工程の少なくとも一の工程と、第1の半導体層に電気的に接続された電極層126を形成する電極形成工程とを備える。

(もっと読む)

半導体素子

【課題】低オン抵抗で、ノーマリーオフ動作を有し、高信頼性の半導体素子を提供する。

【解決手段】半導体素子1Aは、支持基板10上にN面成長されたAlXGa1−XN(0≦X<1)を含む第1半導体層11と、前記第1半導体層上に形成されたノンドープもしくは第1導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層15と、前記第2半導体層上に形成されたAlZGa1−ZN(0≦Z<1、Z<Y)を含む第3半導体層16と、を備える。半導体素子1Aは、第3半導体層16に接続された第1主電極20と、第3半導体層16に接続された第2主電極21と、第1主電極と第2主電極とのあいだの第3半導体層16の上に設けられたゲート電極31と、を備える。第3半導体層16の厚さは、ゲート電極31下において選択的に薄い。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体ウエーハ及び半導体素子及びその製造方法

【課題】クラックが少なく表面の平坦性が良好な半導体ウエーハ及び半導体装置及びその製造方法を提供する。

【解決手段】半導体ウエーハは、基板2と、基板2の一方の主面上に配置され且つ化合物半導体で形成されたバッファ領域3と、バッファ領域3の上に配置され且つ化合物半導体で形成された主半導体領域4とを有する半導体ウエーハであって、バッファ領域3は、第1の多層構造バッファ領域5と、基板と第1の多層構造バッファ領域5との間に配置された第2の多層構造バッファ領域8とから成る。

(もっと読む)

炭化シリコン基板上のIII族窒化物エピタキシャル層

【課題】炭化シリコン基板上のIII族窒化物エピタキシャル層の提供。

【解決手段】半導体構造が開示され、この半導体構造は、少なくとも100mmの直径を有する炭化シリコンのウェハと、ウェハ上のIII族窒化物ヘテロ構造とを含んでおり、これは、多くの特性において、高い均一性を示す。これらは、ウェハ全面で3パーセント未満のシート抵抗率の標準偏差;ウェハ全面で1パーセント未満の電子移動度の標準偏差;ウェハ全面で約3.3パーセント以下のキャリア密度の標準偏差;およびウェハ全面で約2.5パーセントの導電性の標準偏差を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

応力変調III−V族半導体装置および関連方法

【課題】基板の変形を制限しつつ厚いIII−V族半導体層の成長を可能にする方法を提供する。

【解決手段】III−V族半導体装置は、基板102の上およびIII−V族半導体装置の活性領域112を支持するバッファ層110の下に配置された組成傾斜本体108を備える。組成傾斜本体108は、基板102に圧縮応力を与える第1の領域を含む。組成傾斜本体108は、第1の領域上に応力変調領域をさらに含み、その応力変調領域は基板102に引張応力を与える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】素子形成領域となる素子形成層の高品質化を実現し、また基板の反りを低減させると共に確実な素子分離を図り、信頼性の高い装置構成を得ることができる化合物半導体装置を実現する。

【解決手段】下地層3上に、素子分離領域に相当する部位に開口4aを有する第1のマスク4を形成し、開口4aを埋め込み、第1のマスク4上を覆うようにELO−GaN層5を成長し、ELO−GaN層5上に、素子形成領域に相当する部位に開口6aを有する第2のマスク6を形成し、開口6aを埋め込むように素子形成層7を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】急峻なヘテロ界面が形成され、高い移動度を有する窒化物半導体からなる半導体装置を得る。

【解決手段】まず、第1成長工程においては、電子走行層(GaN層)を成長させるため、MOCVD装置のチャンバ内に、NH3とTMGがオン(供給)され、TMAはオフ(停止)とされる。次に、バリア層を成長させる前に、TMG、TMAを共にオフとする成長中断工程を行う。次に、TMAのみをオンとし、TMGをオフのままとしたプリフロー工程を行う。プリフロー工程において、TMAの流量は、第2の流量f2に設定される。f2は、電子走行層12とバリア層13との間に急峻な界面が形成されるように設定される。次に、TMGと共にTMAをオンとし、バリア層(AlGaN層)を成長させる第2成長工程を行う。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】通常の極性面上(すなわちc軸方向)に形成するエンハンスメント型の窒化物半導体電界効果トランジスタとして、高い密度のドレイン電流を実現することが可能にする。

【解決手段】窒化物半導体からなるチャネル層半導体6の上方の極性面方向に、チャネル層半導体6よりもバンドギャップの大きい窒化物半導体からなる障壁層半導体5が積層され、ゲート電極2の下方に存在する素子領域のうち少なくとも一部の素子領域を覆う第1領域21内に存在する障壁層半導体5の層厚が、第1領域21以外の素子領域を覆う第2領域22内に存在する障壁層半導体5の層厚よりも薄く形成されるか、または、第1領域21内には障壁層半導体5が存在しない状態で形成されるとともに、第2領域22内に存在する障壁層半導体5中に、障壁層半導体5よりもバンドギャップが小さい単一層の量子井戸7または多重層の多重量子井戸を挿入した量子井戸構造が形成される構造にする。

(もっと読む)

炭化珪素半導体装置

【課題】従来よりオン抵抗が低くかつ高い耐圧を有する炭化珪素半導体装置を提供する。

【解決手段】この発明に従ったJFET10は、n型基板11と、p型層2、12と、n型層13と、ソース領域15と、ドレイン領域17と、ゲート領域16とを備える。n型基板11は、{0001}面に対するオフ角が32°以上である主表面11Aを有し、炭化珪素(SiC)からなる。p型層2、12は、n型基板11の主表面11A上に形成され、導電型がp型である。n型層13は、p型層2、12上に形成され、導電型がn型である。ソース領域15およびドレイン領域17は、n型層13において、互いに間隔を隔てて形成され、導電型がn型である。ゲート領域16は、n型層13において、ソース領域15とドレイン領域17との間の領域に形成され、導電型がp型である。

(もっと読む)

窒化物半導体素子および窒化物半導体パッケージ

【課題】トランジスタ動作のオフ時におけるリーク電流を低減することができる窒化物半導体素子、およびリーク電流が少なく、信頼性に優れる窒化物半導体素子パッケージを提供すること。

【解決手段】基板41上に、AlN層47、第1AlGaN層48(平均Al組成50%)および第2AlGaN層49(平均Al組成20%)からなるバッファ層44を形成する。バッファ層44上には、GaN電子走行層45およびAlGaN電子供給層46からなる素子動作層を形成する。これにより、HEMT素子3を構成する。このHEMT素子3において、GaN電子走行層45の厚さ方向途中部に、BNとGaNとの混晶からなるBGaN部50を形成する。

(もっと読む)

基板上に堆積された窒化ガリウムフィルムにおける応力の制御方法

【課題】シリコンおよび炭化ケイ素基板上に堆積されたGaNフィルムにおける応力の制御方法、およびこれによって生成されたGaNフィルムを提供する。

【解決手段】典型的な方法は、基板を供給すること、および供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上にグレーデッド窒化ガリウム層を堆積させることを含む。典型的な半導体フィルムは、基板と、供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上に堆積されたグレーデッド窒化ガリウム層とを含む。

(もっと読む)

窒化物半導体素子および窒化物半導体パッケージ

【課題】GaN電子走行層の厚さを広い範囲で選択することができ、デバイス設計の自由度を高めることができる窒化物半導体素子、および耐圧および信頼性に優れる窒化物半導体素子パッケージを提供すること。

【解決手段】基板41上に、AlN層47、第1AlGaN層48(平均Al組成50%)および第2AlGaN層49(平均Al組成20%)からなるバッファ層44を形成する。バッファ層44上には、GaN電子走行層45およびAlGaN電子供給層46からなる素子動作層を形成する。これにより、HEMT素子3を構成する。

(もっと読む)

窒化物系化合物半導体素子の製造方法および窒化物系化合物半導体素子

【課題】リーク電流が低減された、耐圧性が高い窒化物系化合物半導体素子の製造方法および窒化物系化合物半導体素子を提供すること。

【解決手段】基板上に少なくともガリウム原子を含むIII族原子と窒素原子とからなる窒化物系化合物半導体層をエピタキシャル成長する成長工程と、素子構造形成前に、前記窒化物系化合物半導体層にレーザ光または電離放射線を照射し、前記窒化物系化合物半導体層中のIII族空孔と水素原子との複合体を分解する分解工程と、を含む。

(もっと読む)

61 - 80 / 450

[ Back to top ]