Fターム[5F102GR01]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 素子形成にあたり、結晶軸、面方位を選択したもの (450)

Fターム[5F102GR01]に分類される特許

21 - 40 / 450

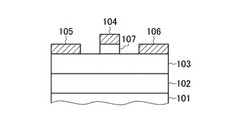

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

高周波用半導体素子形成用のエピタキシャル基板および高周波用半導体素子形成用エピタキシャル基板の作製方法

【課題】コストメリットがあり、かつ、特性の優れた高周波動作用の半導体素子を実現できるエピタキシャル基板を提供する。

【解決手段】導電性を有するSiCまたはSiからなる基材の上に、絶縁性を有する第1のIII族窒化物からなる下地層をMOCVD法によって、表面に実質的に非周期的な凹凸構造を有するようにかつ、表面の平均粗さが0.5μm以上1μm以下となるように、エピタキシャル形成し、下地層の上に、GaNからなるチャネル層をエピタキシャル形成し、チャネル層の上に、AlxGa1−xN(0<x<1)からなる障壁層をエピタキシャル形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因するクラック等を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成されたGaN系化合物半導体積層構造3と、基板1とGaN系化合物半導体積層構造3との間に設けられたAlN系の応力緩和層2と、が設けられている。応力緩和層2のGaN系化合物半導体積層構造3と接する面に、深さが5nm以上の窪み2aが2×1010cm-2以上の個数密度で形成されている。

(もっと読む)

化合物半導体基板

【課題】化合物半導体層全体の膜厚を抑制しつつ、半導体素子の高い性能と信頼性を両立することのできる化合物半導体基板を提供する。

【解決手段】シリコン単結晶の基板12と、基板上に形成される化合物半導体の第1の半導体層16と、第1の半導体層上に形成され、第1の半導体層よりもバンドギャップエネルギーの大きい、化合物半導体の障壁層18と、障壁層上に形成され、障壁層よりもバンドギャップエネルギーの小さい化合物半導体の第2の半導体層20と、第2の半導体層上に形成され、第2の半導体層よりもバンドギャップエネルギーの大きい化合物半導体の第3の半導体層22とを有することを特徴とする化合物半導体基板。

(もっと読む)

半導体素子、HEMT素子、および半導体素子の製造方法

【課題】逆方向漏れ電流が抑制されてなるとともに二次元電子ガスの移動度が高い半導体素子を提供する。

【解決手段】下地基板1の上にIII族窒化物層群を(0001)結晶面が基板面に対し略平行となるよう積層形成したエピタキシャル基板10と、ショットキー性電極9と、を備える半導体素子20において、エピタキシャル基板10が、Inx1Aly1Gaz1N(x1+y1+z1=1、z1>0)なる組成の第1のIII族窒化物からなるチャネル層3と、Inx2Aly2N(x2+y2=1、x2>0、y2>0)なる組成の第2のIII族窒化物からなる障壁層5と、GaNからなり障壁層5に隣接する中間層6aと、AlNからなり中間層に隣接するキャップ6b層と、を備え、ショットキー性電極9がキャップ層6bに接合されてなるようにする。

(もっと読む)

電界効果トランジスタ

【課題】チャネルへの電子供給能力が改善されたIII−V族FETを提供する。

【解決手段】基板2の上には、ナローバンドギャップ材料のチャネル層4が形成される。チャネル層4の上のソース領域には、ワイドバンドギャップ材料のコンタクト層6が形成される。ソースコンタクト層6は、1×1019cm−3以上の濃度でドーピングされる。FET1は、ソースコンタクト層6によってアンドープのチャネル層4に直接キャリアが注入されるように構成される。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

低マイクロパイプの100mm炭化ケイ素ウェハ

【課題】種結晶を用いた昇華システムにおいて形成された結晶の欠陥レベルが低く、より大きく、高品質のSiC単結晶ウェハを製造する方法を提供する。

【解決手段】少なくとも約100mmの直径と、約25cm−2未満のマイクロパイプ密度とを有し、また、3C、4H、6H、2Hおよび15Rポリタイプからなる群から選択されるポリタイプを有するSiC単結晶ウェハ。なお、マイクロパイプ密度は、表面上にある全マイクロパイプの総数を、ウェハの表面積で割ったものを表す。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

III−窒化物デバイスの製造方法およびIII−窒化物デバイス

【課題】高耐圧なIII−窒化物デバイスを提供する。

【解決手段】半導体基板1、基板1上の活性層のスタックであって、それぞれの層はIII−窒化物材料を含むスタック2−5、スタック2−5上のゲート8、ソース9およびドレインコンタクト10、および基板1の裏側(活性層のスタックに接する側に対向する側)から基板1に接する活性層のスタックの下層まで基板中を延びるトレンチであって、トレンチはドレイン領域を完全に囲み、ドレインに向かうゲート領域の端と、ゲートに向かうドレイン領域の端との間に配置され、基板のドレイン領域は本質的に半導体材料から形成されるような幅を有するトレンチを含むIII−窒化物デバイス。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】ウルツ鉱型結晶構造の半導体を用いた電界効果トランジスタで、電極との接触抵抗を高くすることなく、バンドギャップエネルギーのより大きな半導体から障壁層が構成できるようにする。

【解決手段】ゲート電極104を挟んで各々離間して障壁層103の上に接して形成された2つの電流トンネル層105と、各々の電流トンネル層105の上に形成された2つのキャップ層106とを備える。電流トンネル層105の分極電荷は、障壁層103の分極電荷よりも大きい。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

半絶縁性窒化物半導体ウエハ、半絶縁性窒化物半導体自立基板及びトランジスタ、並びに半絶縁性窒化物半導体層の成長方法及び成長装置

【課題】高い抵抗率(例えば、1×105Ωcm以上、1×1012Ωcm以下)、良好な抵抗率の均一性(例えば、ウエハ表面積の80%に相当するウエハ内周側の位置での抵抗率のバラツキが±30%以下)、及び良好な結晶性(例えば、X線(004)回折の半値幅が30〜300秒)を有する半絶縁性窒化物半導体ウエハ、半絶縁性窒化物半導体自立基板及びトランジスタ、並びに半絶縁性窒化物半導体層の成長方法及び成長装置を提供する。

【解決手段】窒化物半導体層の成長方法は、基板上にIII族原料GaClを連続的又は断続的に供給するとともに、窒素原料NH3と半絶縁性を付与する半絶縁性ドーパント原料Cp2Feとを交互に供給して基板上に半絶縁性窒化物半導体層を成長させる。

(もっと読む)

半導体素子及びその製造方法

【課題】転位密度を低減させるバッファ層を有する半導体素子を提供する。

【解決手段】基板と、基板の上方に形成されたバッファ領域と、バッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、バッファ領域は、第1の格子定数を有する第1半導体層と、第1の格子定数と異なる第2の格子定数を有する第2半導体層と、第1の格子定数と第2の格子定数との間の第3の格子定数を有する第3半導体層とが順に積層した複合層を少なくとも一層有する半導体素子。

(もっと読む)

半導体素子及びその製造方法

【課題】リーク電流が低減された窒化物系半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板10の上方に形成されたバッファ領域30と、バッファ領域30上に形成された活性層70と、活性層上に形成された少なくとも2つの電極72、74、76とを備え、バッファ領域30は、格子定数の異なる複数の半導体層31、32、33を含み、バッファ領域30の表面に、基板10の裏面より低い電位を与え、基板10の裏面とバッファ領域30の表面との間の電圧をバッファ領域30の膜厚に応じた範囲で変化させたときの基板10の裏面およびバッファ領域30の表面との間の静電容量が略一定である半導体素子100を提供する。

(もっと読む)

半導体素子及びその製造方法

【課題】厚膜化が可能で、反りが小さく、かつリーク電流が小さい半導体素子を提供する。

【解決手段】基板と、基板の上方に形成された第1のバッファ領域と、第1のバッファ領域上に形成された第2のバッファ領域と、第2のバッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、第1のバッファ領域は、第1半導体層と、第2半導体層とが順に積層した複合層を少なくとも一層有し、第2のバッファ領域は、第3半導体層と、第4半導体層と、第5半導体層とが順に積層した複合層を少なくとも一層有し、第4半導体層の格子定数は、第3半導体層と第5半導体層の間の格子定数を有する半導体素子。

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

【課題】ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する。

【解決手段】SiC層10にSiO2層を形成し、次いで、熱伝導率を高めるためにダイアモンド層11を形成する。そして、SiC層10の厚さを低減し、ダイアモンド層11及びSiC層10の向きを逆にしてダイアモンド11を基板とする。次いで、SiC層10上に、バッファ層16、ヘテロ構造層14及び15を形成する。

(もっと読む)

21 - 40 / 450

[ Back to top ]