Fターム[5F102GS06]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 断面形状 (702) | 左右非対称 (75)

Fターム[5F102GS06]に分類される特許

41 - 60 / 75

電界効果トランジスタ及びその製造方法

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタは、基板1、チャネル層3及びバリア層4と、バリア層4上にこの順で離間して設けられたソース電極6、ゲート電極7およびドレイン電極8とを備え、ソース電極6の直下に第1のn型不純物拡散領域12が設けられ、ドレイン電極8の直下に第2のn型不純物拡散領域13が設けられ、第2のn型不純物拡散領域の下側の前記チャネル層3および第2のn型不純物拡散領域の前記ゲート電極側の前記チャネル層3および前記バリア層4に第3のn型不純物拡散領域15が設けられる。第3のn型不純物拡散領域15は第2のn型不純物拡散領域13よりも低いn型不純物濃度を有し、ゲート電極とドレイン電極との間に電圧が印加されたときバリア層4およびチャネル層3においてその絶縁破壊強度を超える電界集中が生じることを抑制する。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

エンハンスメント型窒化ガリウム高電子移動度トランジスタ

実施形態には、これに限定されないが、第1バリア層と、該第1バリア層上の窒化ガリウムチャネル層と、該窒化ガリウムチャネル層上に存在し、第1サブレイヤーと第2サブレイヤーと第3サブレイヤーとを備える第2バリア層と、を有するヘテロ構造を備える装置とシステムが含まれる。該第1バリア層、第1サブレイヤーおよび第3サブレイヤーは各々アルミニウムを含んでいてもよい。他の実施形態も、本明細書に記載され特許請求される。 (もっと読む)

ヘテロ接合電界効果トランジスタ、その製造方法

【課題】ゲート電極下の電子の走行方向が基板表面に略平行であるようにデバイス構造を改良しながらも各種弊害を解消したヘテロ接合電界効果トランジスタを提供する。

【解決手段】n型導電層は選択的にイオン注入されているシリコン(Si)などのn型不純物をアニール処理で活性化することにより形成されており、n型導電層は、イオンが200keV以上の加速エネルギーで注入されており、p型窒化物半導体層より深く、かつドレイン電極114と導通する半導体層にまで注入イオンが達する選択的イオン注入によって形成されており、n型導電層とn型不純物が注入されていないチャネル領域との接続部115に注入されているn型不純物濃度が1×1018cm−3以下である。

(もっと読む)

GaN系半導体素子およびその製造方法

【課題】SiO2からなるゲート絶縁膜を常圧CVDによって形成することで、十分なノーマリオフ特性が得られるGaN系半導体素子およびその製造方法を提供する。

【解決手段】基板11上にバッファ層13を介して積層されたp型のGaN系化合物半導体からなるチャネル層14とゲート電極Gとの間にゲート絶縁膜17が形成されたGaN系半導体素子1において、ゲート絶縁膜17が、常圧CVD法により成膜されたSiO2膜である。常圧CVD法により成膜されたSiO2膜は、Si−H結合や未結合手の発生が抑制された高品質のSiO2膜である。このようなSiO2膜により、GaN系半導体素子のしきい値の制御に及ぼす悪影響も抑制されるので、十分なノーマリオフ特性が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】電流コラプスを減少し耐圧を維持しつつ、オン抵抗を改善した、高電圧、高周波で動作する半導体装置を提供する。

【解決手段】この発明にかかる半導体装置は、ヘテロ接合型の窒化物半導体装置であって、基板1上に形成されたチャネル層2と、チャネル層2上に形成された電子供給層3と、電子供給層3上に選択的に形成されたゲート電極5と、ゲート電極5を挟み離間して形成されたソース、ドレイン電極4a,4bと、ゲート電極5のドレイン電極側端部近傍を除く第1領域に形成され、当該第1領域に対応する二次元電子ガス濃度に作用する第1薄膜である薄膜8と、ゲート電極5のドレイン電極側端部近傍の第2領域に形成され、当該第2領域に対応する二次元電子ガス濃度に作用し、当該濃度を第1領域に対応するそれよりも低くする第2薄膜である薄膜6とを備える。

(もっと読む)

半導体装置及びその製造方法

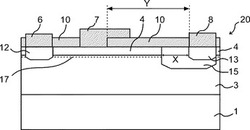

【課題】高い高周波利得と高出力密度とを兼ね備える半導体装置及びその製造方法を提供すること。

【解決手段】本発明は、基板1上に、バッファ層2、チャネル層3、電子供給層4が順に形成されている。電子供給層4は表面保護膜21で覆われている。また、電子供給層4に接するソース電極6及びドレイン電極7が形成されている。ゲート電極8は、ソース電極6とドレイン電極7の間で、電子供給層4に接して形成されている。さらに、電子供給層4に形成された凹部5に充填された絶縁体からなる電界緩和層11が形成されている。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】ゲート容量の増大を抑制しつつ、耐湿性を大幅に向上させることを可能にした電界効果型トランジスタおよびその製造方法を得る。

【解決手段】半導体層1上にT型ゲート電極2が形成された電界効果型トランジスタであって、T型ゲート電極2が形成されている領域をトランジスタ能動領域としたとき、当該トランジスタ能動領域全体において、T型ゲート電極2上に設けられた、耐湿性・耐エッチング性の高い絶縁膜若しくは有機膜を含む第1の高耐湿性保護膜5を備え、T型ゲート電極2の傘下を含むT型ゲート電極2の近傍において、半導体層1と第1の高耐湿性保護膜5との間に空隙6が形成されており、空隙6が外界に接している端面6aを第2の高耐湿性保護膜7により塞いだ構成となっている。

(もっと読む)

III族窒化物デバイスおよび回路

ゲート接続接地電界プレートを有するIII族窒化物ベースの高電子移動度トランジスタを説明する。ゲート接続接地電界プレートデバイスは、ミラー容量効果を最小化することができる。トランジスタは、高電圧空乏モードトランジスタとして形成し、低電圧エンハンスメントモードトランジスタと組み合わせて、単一の高電圧エンハンスメントモードトランジスタとして動作する部品を形成するために用いることができる。 (もっと読む)

半導体装置及びその製造方法

【課題】本発明は、逆阻止特性を有し、かつノーマリオフ特性、オン抵抗とオフ電流の抑制を実現する半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、チャネル層14及び電子供給層15を含む半導体積層構造10と、半導体積層構造10上に離間して形成されたソース電極1およびドレイン電極4と、ソース電極1及び前記ドレイン電極4間に形成された絶縁膜22と、絶縁膜上に形成されたゲート電極2とを備え、ドレイン電極4と前記半導体積層構造10との間の逆電流が阻止されたものである。

(もっと読む)

半導体装置及びその製造方法

【課題】 窒化アルミニウムあるいは窒化アルミニウムガリウムを含む窒化物半導体層を用い、緩やかに傾斜したフィールドプレートの形成が容易に形成ができ、電界集中を緩和して高耐圧化が実現できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】 窒化アルミニウムあるいは窒化アルミニウムガリウムを含む窒化物半導体層に形成した側壁が斜めに傾斜した凹部内に、ゲート電極を形成する。側壁が斜めの凹部は、アルミニウムを含む窒化物半導体層の結晶性を劣化させながら成長させ、その後、結晶性の違いに応じてエッチングレートが異なるエッチング液を使用してエッチングして形成する。あるいはアルミニウムの組成比を変化させて形成することも可能である。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】MIS−HEMTにおいて、閾値電圧の低下を抑制する。

【解決手段】半導体装置は、基板19と、この基板上に形成されており、電子走行層13及び電子供給層15が順次積層されて形成された積層構造体17とを含む下地11を具えている。この下地の下地面には、互いに離間し、かつ対向して第1及び第2主電極が形成されている。そして、下地面11aの、これら第1主電極41a及び第2主電極41b間に挟まれた領域内に、ゲート形成用凹部27が形成されている。更に、半導体装置はゲート絶縁膜29を具えている。そして、このゲート絶縁膜は、最小でも2.9g/cm3の結晶密度で形成されている。また、半導体装置は、ゲート絶縁膜が形成された前記ゲート形成用凹部を埋め込むゲート電極43を具えている。

(もっと読む)

半導体装置

【課題】電界集中を緩和し耐圧を向上しつつ、電流コラプスを低減しかつリーク電流を減少することができる半導体装置を提供する。

【解決手段】半導体装置1において、窒化物系半導体2上に互いに離間して配設された制御電極5及び第2の主電極4と、窒化物系半導体2上の制御電極5と第2の主電極4との間に配設された第1の絶縁体6と、制御電極5に一端が電気的に接続され、他端が第1の絶縁体6上において制御電極5と第2の主電極4との間に配設された第1のフィールドプレート5FPと、第1の絶縁体6上において一端が第1のフィールドプレート5FPに接続され、他端が第2の主電極4に向かって延伸され、第1のフィールドプレート5FPに比べて高いシート抵抗を有する抵抗性フィールドプレート7とを備える。

(もっと読む)

GaN系半導体素子

【課題】小さいオン抵抗を維持しながら閾値を確実にプラスに引き上げ、実効的にノーマ

リオフになるGaN系半導体素子を提供する。

【解決手段】電界効果トランジスタ20では、サファイア基板1上に、バッファ層2と、チャネル層(アンドープGaN層)3と、電子供給層(アンドープAlGaN層)4とを順に積層している。電子供給層4上のソース部分にnpn積層構造9が形成され、積層構造9上にソース電極Sが形成されている。電子供給層4のドレイン部分にドレイン電極Dが形成され、そのゲート部分に形成された開口部11に絶縁膜8が形成されている。ゲート電極Gに順方向に閾値以上の電圧を印加すると、反転層Aと反転層Bが形成されてドレイン電流が流れる。p型(In)GaN層6の厚さやその不純物濃度を変えることで、閾値電圧を制御することができる。ドリフト層12によりゲート電極Gとドレイン電極D間の電界集中が緩和され、耐圧が向上する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】耐圧性が高い電界効果トランジスタおよびその製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成された、リセス部を有する半導体動作層と、前記リセス部を含む前記半導体動作層上に形成された絶縁膜と、前記リセス部における前記絶縁膜上に形成されたゲート電極と、前記半導体動作層上に前記リセス部を挟んで形成され、前記半導体動作層に電気的に接続されたソース電極およびドレイン電極と、を備え、前記リセス部が前記半導体動作層に対して傾斜して立ち上がっている側壁部を有する。

(もっと読む)

窒化物半導体装置の製造方法

【課題】 電流コラプスの抑制と高耐圧化が実現できると共に、微結晶構造の窒化物半導体層を緩やかに傾斜した形状に形成し、電界集中を緩和することができる窒化物半導体装置の製造方法を提供する。

【解決手段】 アルミニウムを含まない高絶縁性の第2の窒化物半導体層に形成した側壁が斜めに傾斜した凹部内に、ゲート電極を形成する。側壁が斜めの凹部は、第2の窒化物半導体装置の成長温度を徐々に低くしながら成長させ、その後、成長温度に応じてエッチングレートが異なるエッチング液を使用してエッチングして形成する。

(もっと読む)

窒化物半導体装置

【課題】 窒化物半導体層に形成されるゲート電極のリーク電流を低減し、窒化物半導体層内での衝突イオン化を抑制することにより高耐圧化を実現し、同時に電流コラプスを抑制することができる窒化物半導体装置を提供する。

【解決手段】 基板上に、第1の窒化物半導体層と、アルミニウムを含まない微結晶構造の第2の窒化物半導体層とを備え、ゲート電極は、第2の窒化物半導体層の一部を切り欠き形成された凹部内に露出する前記第1の窒化物半導体層あるいはわずかに残した第2の窒化物半導体層にショットキ接触し、ドレイン側に延出するフィールドプレート部を備える。

(もっと読む)

III族窒化物双方向スイッチ

【課題】 双方向スイッチが記載される。

【解決手段】 双方向スイッチは、第1及び第2III・Nベース高電子移動度トランジスタを有している。幾つかの実施例においては、該第1トランジスタのソースは該第2トランジスタのソースと電気的に接触している。幾つかの実施例においては、該第1トランジスタのドレインは該第2トランジスタのドレインと電気的に接触している。幾つかの実施例においては、該2個のトランジスタはドリフト領域を共用し、且つ該スイッチは該2個のトランジスタ間にはドレインコンタクトが無い。該双方向スイッチからマトリックスコンバータを形成することが可能である。

(もっと読む)

半導体装置

【課題】III族窒化物半導体からなり、ヘテロ接合を有する半導体装置において、HJFETを作製する際、エンハンスメント型のHJFETが容易に実現でき、そのエンハンスメント動作時におけるチャネル抵抗の低減がなされる構造を提供を提供する。

【解決手段】ゲート部を、障壁層に接するように設ける。ゲート直下となる部分では、ゲートを設けていない状態でも、障壁層とチャネル層とのヘテロ接合界面には、二次元電子ガスは発生しないように、チャネル層上に形成されるInAlGaN障壁層を構成する、InAlGaNの組成を選択する。ゲート直下を除き、InAlGaN障壁層の上層として、InAlGaNキャップ層を設ける。InAlGaNキャップ層は、バッファ層と格子整合し、自発分極により、障壁層とチャネル層の界面に二次元電子を発生させる組成のInAlGaNで形成する。

(もっと読む)

41 - 60 / 75

[ Back to top ]