Fターム[5F102GT03]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | 金属 (1,688) | 高融点金属(Mo、Ti、Ta、W、Cr、Nb、Hf、V、Zr) (912)

Fターム[5F102GT03]に分類される特許

901 - 912 / 912

熱スペーサを有する半導体デバイス

高出力高周波数半導体デバイスは、並列に接続された複数のユニットセルを有する。これらのユニットセルは各々、制御電極と、第1及び第2の被制御電極とを有する。熱スペーサ(すなわち、電気的に不活性な領域)が、これらのユニットセルのうち少なくとも1つを第1の活性部分及び第2の活性部分に分割し、第2の活性部分は、この熱スペーサにより第1の部分から離隔される。ユニットセルの制御電極ならびに第1及び第2の被制御電極は、第1の熱スペーサを横切っている。

(もっと読む)

(もっと読む)

III族窒化膜双方向スイッチ

【課題】電力用デバイスにおいて双方向に電圧をブロックできるようにする。

【解決手段】大電流を搬送するチャンネルを得るAlGaN/GaNインターフェースを備えたIII族窒化物双方向スイッチであり、この双方向スイッチは、この双方向スイッチのために、電流を搬送するチャンネルを形成するための二次元電子ガスの発生を阻止したり、または可能にする少なくとも1つのゲートにより作動する。

(もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。  (もっと読む)

(もっと読む)

炭化珪素半導体素子及びその製造方法

半導体素子の製造方法は、炭化珪素基板1上に形成された炭化珪素薄膜2内にイオンを注入する工程と、炭化珪素基板を減圧雰囲気で加熱することで炭化珪素基板の表面にカーボン層5を形成する工程と、カーボン層5を形成する工程より高い圧力で、且つ高い温度の雰囲気中で炭化珪素基板を活性化アニールする工程とを含んでいる。 (もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

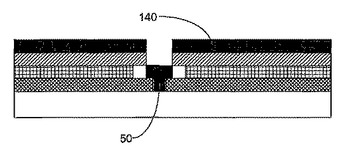

フィールドプレートを有するワイドバンドギャップトランジスタデバイス

活性層との電気的コンタクトで形成された金属のソースおよびドレインコンタクト(20,22)を有する活性半導体層を備えるトランジスタ構造。ゲートコンタクト(26)が、活性層内の電界を変調するためにソースコンタクトとドレインコンタクトとの間に形成されている。スペーサ層(24)が、活性層の上に形成されている。導電性フィールドプレート(28)がスペーサ層の上に形成され、ゲートコンタクトの端からドレインコンタクトに向かって距離Lf延びている。フィールドプレートは、ゲートコンタクトに電気的に接続されている。

(もっと読む)

(もっと読む)

化合物半導体層の表面処理方法及び半導体装置の製造方法

【課題】窒素を含む化合物半導体層の表面に生じた、エッチングによるダメージを除去あるいは軽減し、ゲート電極に良好なショットキ特性を有する半導体装置を形成する。

【解決手段】ドライエッチングにより、第1化合物半導体層22のゲート電極形成予定領域36の表面を露出するとともに、コンタクト層32を形成する。次いで、この第1化合物半導体層22の露出した表面に対するアニール処理を行う。前述のドライエッチングの際に第1化合物半導体層22の表面に生じたダメージを、窒素プラズマを用いた表面処理を行うことにより、良好な電気特性をもつ第1化合物半導体層22の表面を形成する。この窒素プラズマを用いた表面処理を行った第1化合物半導体層22の表面上にゲート電極38を形成し、良好なショットキ特性を有するゲート電極を具えたリセス型HEMT10を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長の短いゲート電極を有し、しかも低抵抗で高周波特性が優れている半導体装置およびその製造方法を提供する。

【解決手段】少なくともノンドープInGaP層又はノンドープInAlGaP層からなる上層半導体層12と、この上層半導体層直下にGaAs層またはAlGaAs層からなる下層半導体層11を含む半導体基板に、上層半導体層表面から上層半導体層への浸入が、下層半導体層で略停止するショットキーゲート電極15と、このショットキーゲート電極部に接続して第1の電極の抵抗を低減する第2の電極部16からなるT字型ゲート電極を形成する。

(もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

マイクロストリップ線路、その製造方法、インダクタ素子及び高周波半導体装置

【課題】 マイクロストリップ線路の線路幅の狭小化を行なったとしても、導体損失が増加しないようにする。

【解決手段】 半絶縁性GaAsからなる基板11上には、接地電極12と、厚さが約0.5μmのチタン酸ストロンチウムからなる誘電体層13と、線状導体層14とにより構成されるマイクロストリップ線路が形成されている。線状導体層14は、幅が約0.5μmの狭小部14aと、幅が約5μmの幅広部14bとにより構成されている。この線状導体層14は、異なる材料からなる積層体であって、基板11側から順次形成された、厚さが約0.1μmの窒化タングステンシリコンからなる第1層15と、厚さが約0.05μmのTiと厚さが約0.5μmのAuとの積層体からなる第2層16と、厚さが約3μmのAuからなる第3層17とから構成されている。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】耐圧性、特性安定性に優れ、ゲートリーク電流が低減されたヘテロ接合型電界効果トランジスタを提供すること。

【解決手段】半導体基板上にバッファ層と、チャネル層と、スペーサ層と、キャリア供給層と、ショットキーバリア層と、高濃度不純物ドープキャップ層とが順次堆積され、ソース電極及びドレイン電極がキャップ層表面に形成され、ソース電極とドレイン電極の間のキャップ層にショットキーバリア層に達する開口部が形成され、開口部に露出したショットキーバリア層表面にゲート電極が形成されているヘテロ接合型電界効果トランジスタであって、キャップ層が複数の細線で構成され、細線間はショットキーバリア層が露出し、ソース電極及びドレイン電極が、細線と細線間に露出したショットキーバリア層との両方に接触していることを特徴とするヘテロ接合型電界効果トランジスタを構成する。

(もっと読む)

901 - 912 / 912

[ Back to top ]