Fターム[5F102GT05]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | シリサイド (137)

Fターム[5F102GT05]に分類される特許

1 - 20 / 137

ヘテロ接合電界効果型トランジスタおよびその製造方法

窒化物半導体素子及びその製造方法

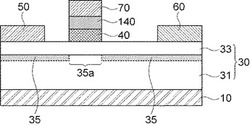

【課題】ノーマリーオフ特性を具現すると共にゲートリーク電流を抑制する窒化物半導体素子及びその製造方法を提供する。

【解決手段】第1の窒化物層31とその材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、その上にオミック接触されたソース電極50と、これから離間して窒化物半導体30層上にオミック接触されたドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に、これらから離間して形成されたP型窒化物層40と、この上に形成されたN型窒化物層140と、ソース側の側壁が、P型窒化物層40及びN型窒化物層140のソース側の側壁と整列するようにN型窒化物層140上に接触させたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】耐圧を高めた窒化物半導体素子及び製造方法を提供する。

【解決手段】第1の窒化物層31と該第1の窒化物層31の材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、該接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、窒化物半導体層30上にオーミック接触されるソース電極50とドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に形成され、ソース電極50から所定距離だけ離間された第1の側壁からドレイン側へ長く形成された多数のP型窒化物半導体セグメント80と、ソース電極50とドレイン電極60との間でソース電極50に近く形成され、多数のP型窒化物半導体セグメント80間の窒化物半導体層30上及びP型窒化物半導体セグメント80上に接触されるゲート電極70とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、オン抵抗を低くしつつ、閾値電圧を高くする。

【解決手段】キャップ層400と障壁層300の界面、及びチャネル層200とバッファ層100の界面には圧縮歪が生じており、障壁層300とチャネル層200の界面には引張り歪が生じている。このため、キャップ層400と障壁層300の界面、並びにチャネル層200とバッファ層100の界面において、負の電荷が正の電荷よりも多くなっており、障壁層300とチャネル層200の界面において、正の電荷が負の電荷よりも多くなっている。チャネル層200は、第1層、第2層、及び第3層の積層構造を有している。第2層は、第1層及び第3層よりも電子親和力が大きい。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

【課題】貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタを作製する。

【解決手段】ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極に臨む領域の半導体層へのダメージ層の形成を抑制して、ノーマリオフ動作を実現することができるヘテロ接合電界効果型トランジスタを備える半導体装置およびその製造方法を提供する。

【解決手段】チャネル層23とヘテロ接合を形成するバリア層24のうち、ゲート電極29に臨む領域を除く他の領域に、バリア層24の伝導帯から、チャネル層23とバリア層24とのヘテロ界面のバンド不連続量ΔEcと、バリア層24に発生する分極によるバリア層24のゲート電極29側とヘテロ界面側とのエネルギー差ΔEpとを足し合わせたエネルギー(ΔEc+ΔEp)までのエネルギー深さのバンドギャップ中に準位を形成する不純物をドーピングして、不純物ドーピング領域26を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系トランジスタを簡便な構造で適切に保護することができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極110gと保護ダイオード用電極115pとが互いに接続されている。絶縁膜113は、所定値以上の電圧がゲート電極110gに印加された場合にリーク電流を保護ダイオード用電極115pと電子走行層104及び電子供給層103との間に流し、所定値は、HEMTがオン動作する電圧より高く、ゲート絶縁膜109gの耐圧よりも低い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

トランジスタ

【課題】耐圧特性に優れた高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】基板12上に形成された複数の活性半導体層16、18を含むHEMT10。ソース電極20、ドレイン電極22、およびゲート24は、複数の活性層16、18と電気的に接触して形成される。スペーサ層26は、複数の活性層16、18の表面の少なくとも一部の上に形成され、ゲート24を覆っている。フィールドプレート30が、スペーサ層26上に形成されて、ソース電極22に電気的に接続され、このフィールドプレート30はHEMT10内の最高動作電界を低減する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】エアブリッジの強度を向上させる。

【解決手段】半導体層上に設けられ、互いに並列に配置された複数のソースフィンガー10と、半導体層上に設けられ、複数のソースフィンガー10と交互に配置された複数のドレインフィンガー12と、半導体層上に設けられ、ソースフィンガー10とドレインフィンガー12との間にそれぞれ配置された複数のゲートフィンガー14と、複数のゲートフィンガー14同士、複数のソースフィンガー10同士、および複数のドレインフィンガー12同士のいずれかを共通に接続するバスラインと、複数のソースフィンガー10、複数のドレインフィンガー12、および複数のゲートフィンガー14のいずれかに設けられ、バスライン上を跨ぐ複数の第1エアブリッジ24と、複数の第1エアブリッジ24同士の間を接続し、半導体層との間に空隙を有する第2エアブリッジ26と、を備える半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】 JFET等のような低ノイズ特性が要求される半導体装置において、発生するノイズを低減すると共に、半導体装置を小さい寸法で製造する。

【解決手段】 半導体装置は、半導体層(101)に形成された素子分離(102)、第1導電型の不純物層(104)、第1導電型のソース領域(106)、第1導電型のドレイン領域(107)、第2導電型のゲート領域(105)、絶縁膜(108)を介して形成された制御電極(109)を備える。制御電極(109)に電圧を印加すると、半導体装置の動作中に制御電極(109)の下の不純物層(104)に空乏層を発生させることができ、キャリアは絶縁膜(108)と不純物層(104)の界面から離れて流れる。

(もっと読む)

半導体装置およびその製造方法

【課題】電子移動度の低下が抑制され、かつ二次元電子ガスの閉じ込めが高められた半導体装置およびその製造方法を提供する。

【解決手段】AlaInbGa1-(a+b)N(0≦a,b≦1、0≦a+b≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが大きい第1の窒化物半導体層2、AlcIndGa1-(c+d)N(0≦c,d≦1、0≦c+d≦1)から成る第2の窒化物半導体層3、IneGa1-eN(0<e≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが小さいバックバリア層4、AlfIngGa1-(f+g)N(0≦f,g≦1、0≦f+g≦1)から成り、第2の窒化物半導体層3とバンドギャップが等しいチャネル層5、AlhIniGa1-(h+i)N(0≦h,i≦1、0≦h+i≦1)から成り、チャネル層5よりもバンドギャップが大きいバリア層6を、この順に基板1に積層する。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ

【課題】電子トラッピングによる、DC特性とRF特性の差を低減する。

【解決手段】トランジスタ10は、チャネル層を有する活性領域を含み、この活性領域と接触してソースおよびドレイン電極20,22が形成され、このソース電極とドレイン電極との間にあって活性領域と接触したゲート24が形成される。ゲートとドレイン電極との間およびゲートとソース電極との間の複数の活性領域の表面の少なくとも一部分上にスペーサ層28がある。このスペーサ層上にはフィールドプレート32があり、活性領域の上のスペーサ上をドレイン電極に向かって延びる。このフィールドプレートはさらに、活性領域の上のスペーサ層上をソース電極に向かって延びる。少なくとも1つの導電性経路34,36が、フィールドプレートをソース電極またはゲートに電気的に接続する。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】耐圧特性の低下やゲートリーク電流の増加を生じることなく、低抵抗で高速動作可能なヘテロ接合電界効果型トランジスタおよびその製造方法を提供する。

【解決手段】ヘテロ接合FETの製造方法に関し、(a)チャネル層3及びチャネル層3上に形成されたバリア層4を窒化物半導体層として準備する工程と、(b)窒化物半導体層上に不純物拡散源としてZnO膜9を形成する工程と、(c)ZnO膜9上のドレイン電極6及びソース電極5を形成すべき領域以外に酸化膜10を形成する工程と、(d)窒化物半導体層に対して熱処理を行い、酸化膜10が形成されていない領域の下部のチャネル層3及びバリア層4に選択的に、ZnO膜9からZn及びOを拡散させる工程とを備える。

(もっと読む)

1 - 20 / 137

[ Back to top ]