Fターム[5F102GV03]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | ボンディング、パッド構造 (230)

Fターム[5F102GV03]に分類される特許

101 - 120 / 230

半導体装置および半導体装置の製造方法

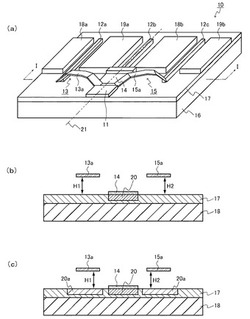

【課題】 電力等の信号の合成効率が高く、チップ占有面積を低減可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】 本発明の半導体装置10は、電極パッド11と、複数の信号伝送電極12a、12bおよび12cと、複数の伝送線路13、14および15とを有し、前記電極パッド11と前記各信号伝送電極12a、12bおよび12cとは、前記各伝送線路13、14および15により電気的に接続され、前記複数の伝送線路13、14および15の少なくとも一本は、その線路長が他の伝送線路14以上であり、前記線路長が他の伝送線路以上である伝送線路13および15は、その一部または全部が空中配線され、前記空中配線された伝送線路13aおよび15aが、マイクロストリップラインであることを特徴とする。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能で、性能のばらつきが抑制された半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下方から上方に向かって径が連続的に拡大された形状であるとともに、下から順にソース領域17、ゲート領域18、ドレイン領域19からなるとともに、ドレイン領域19は、ソース領域17よりも長く形成され、ソース領域17の周囲には第1の絶縁膜20、ゲート領域18の周囲にはゲート電極21、ドレイン領域19の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

はんだ濡れ性の前面金属部を備えるIII族窒化物パワーデバイス

【課題】外部回路接続に棒はんだを用いる、複数の相互接続金属層およびはんだ濡れ性の前面金属部構造を備えるHEMTを含むIII族窒化物パワーデバイスの、いくつかの典型的な実施形態を提供する。

【解決手段】はんだ濡れ性の前面金属部140aおよび140bの構成は、TiNiAgのようなトリメタルからなり、HEMTのソースおよびドレインコンタクトを交互の細長いデジットまたはバーとして露出するように設けられる。また、単一のパッケージは、前面金属部構造140aおよび140bが交互の相互嵌合したソースおよびドレインコンタクトを露出する、こうしたHEMTを多数集積し、これはIII族窒化物デバイスを用いるDC‐DCパワー変換回路設計に有利となり得る。外部回路接続に棒はんだを用いることにより、横方向の導電が可能となり、これによりデバイスのオン抵抗Rdsonを低減する。

(もっと読む)

電子デバイス及びオーミック電極形成方法

【課題】製造工程において高温で短時間のアニールを可能にすることにより、イオン注入の工程が不要なAlxGa1−xN/AlyGa1−yNヘテロ接合のオーミック電極を備える電子デバイスを提供する。

【解決手段】

電子デバイスは、ワイドバンドギャップ化合物半導体層と、前記ワイドバンドギャップ化合物半導体層上に形成されるオーミック電極とを含む電子デバイスであって、前記ワイドバンドギャップ化合物半導体層は、IniAljGakN(i+j+k=1,0≦i≦1,0<j≦1,0≦k<1)からなる化合物半導体バリア層とAlyGa1−yN(0<y≦1)からなる化合物半導体チャネル層からなり、前記オーミック電極は、前記化合物半導体バリア層上に密着層が積層され、前記密着層上にオーミック層が積層されて形成された電極であり、前記密着層はZrからなるようにする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能で、性能のばらつきが抑制された半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたドレインパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたソースパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下方から上方に向かって径が連続的に拡大された形状であるとともに、下から順にドレイン領域17、ゲート領域18、ドレイン領域17よりも短いソース領域19からなり、ドレイン領域17の周囲には第1の絶縁膜20、ゲート領域18の周囲にはゲート電極21、ソース領域19の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが抑制された窒化物半導体を用いた電界効果トランジスタを容易に実現できるようにする。

【解決手段】電界効果トランジスタは、基板100の上に形成され、第1の窒化物半導体層122及び第2の窒化物半導体層123を有する半導体層積層体102を備えている。半導体層積層体102の上には、互いに間隔をおいてソース電極131及びドレイン電極132が形成されている。ソース電極131とドレイン電極132との間には、ソース電極131及びドレイン電極132と間隔をおいてゲート電極133が形成されている。ドレイン電極132の近傍には正孔注入部141が形成されている。正孔注入部141は、p型の第3の窒化物半導体層142及び第3の窒化物半導体層142の上に形成された正孔注入電極143を有している。ドレイン電極132と正孔注入電極142とは、電位が実質的に等しい。

(もっと読む)

半導体装置

【課題】電流駆動型の半導体装置のゲートへの寄生インダクタンスによる外乱ノイズを低減し、ゲート駆動を高精度化及び安定化させる。

【解決手段】半導体装置100であって、電流駆動型の半導体素子3と、半導体素子3を制御するゲート駆動回路11と、接続端子部とを備え、半導体素子3は、窒化物半導体層の積層体の上に形成されたゲート電極パッド1と、オーミック電極パッド2及び5とを有し、接続端子部は、オーミック電極パッド2と接続されたオーミック電極端子6と、オーミック電極パッド5と接続されたオーミック電極端子10と、オーミック電極パッド2と接続されたゲート駆動用端子7と、ゲート電極パッド1と接続されたゲート端子8とを有し、ゲート駆動回路11の入力端子はゲート駆動用端子7に接続され、ゲート駆動回路11の出力端子はゲート端子8に接続され、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位とする。

(もっと読む)

半導体装置

【課題】Ti、PtおよびAuからなるゲート電極を有するリセス構造を有し、Ti上のPt若しくはAuが、素子領域表面のAlGaAs層に拡散することを抑制する半導体装置を提供する。

【解決手段】GaAs基板11上に形成された素子領域16と、第1のリセス領域25と、第2のリセス領域26と、第1のリセス領域25外の素子領域16上に、互いに離間して形成されたドレイン電極13およびソース電極14と、第2のリセス領域26の表面の一部に接し、第1のリセス領域25の表面の一部に接するゲート電極15を具備し、最下層が、第1のリセス領域25、および第2のリセス領域26の表面の一部に接するように、隙間を有して形成された第1のTi層29と、第1のTi層29上に、第1のTi層29の隙間を埋めるように形成されたAl層30と、Al層30上に形成されたPt層32と、Pt層上に形成されたAu層33と、を含むように構成する。

(もっと読む)

半導体装置

【課題】半絶縁性基板に形成されたゲートパッドにマイナスの電圧が印加され、半絶縁性基板の裏面に形成された裏面電極にプラスの電圧が印加されても、リーク電流を抑制できる半導体装置を提供する。

【解決手段】裏面電極10が形成された半絶縁性基板11の表面上に並列に形成された、複数のゲート電極15がゲート電極接続部21に接続されるとともに、このゲート電極接続部21が複数に分割された半導体装置であって、ゲート電極接続部21間の半絶縁性基板11の表面に形成されたn型の抵抗層22と、このn型の抵抗層22の周囲を覆うように、p型不純物層23と、このp型不純物層23の周囲を覆うように、所望の濃度で形成されたn型不純物層24と、を具備し、ゲートパッド29は、ゲート電極接続部21と、このゲート電極接続部21に隣接するn型の抵抗層22上の引き出し電極25とを接続するように形成される。

(もっと読む)

高周波半導体装置

【課題】FETセルごとに電源を用意・制御することなく、所望の出力電力値に合わせて、出力電力値を調整可能な高周波半導体装置を提供する。

【解決手段】分配・入力整合回路32と入力伝送線路パターン36とを搭載した分配・入力整合回路基板14と、複数の入力キャパシタセル40を搭載した入力キャパシタ基板16と、複数の電界効果トランジスタセルを搭載した半導体基板18と、複数の出力キャパシタセル41を搭載した出力キャパシタ基板20と、出力伝送線路パターン38と合成・出力整合回路34とを搭載した合成・出力整合回路基板22とを備え、所望の出力電力値に合わせて複数のセルからなる電界効果トランジスタのセル数を接続・非接続により、総ゲート電極長を実質的に変化させて、出力電力値を調整可能な高周波半導体装置30。

(もっと読む)

半導体装置

【課題】保護素子の素子面積を小さく抑え且つ製造工程を複雑にすることなくサージ耐性が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1の素子領域106Aに形成された第1のトランジスタ111と、第2の素子領域106Bに形成された第2のトランジスタ121を含む第1の保護素子とを備えている。第2の保護素子オーミック電極123Bは第1のゲート電極115と接続され、第1の保護素子オーミック電極123Aは第1のオーミック電極113Aと接続され、第1の保護素子ゲート電極115は、第1の保護素子オーミック電極123A及び第2の保護素子オーミック電極123Bの少なくとも一方と接続されている。第2の素子領域106Bの面積は、第1の素子領域106Aよりも小さい。

(もっと読む)

高い電流許容能力を有するラテラル半導体構成エレメント用のスケーラビリティを有する構造

本発明は、半導体部品、特に、高い電流許容能力を有するラテラル半導体構成エレメント用のスケーラビリティを有する構造に関する。本発明に係るある一つのトランジスター・セルは、一つの制御端子、多数のスプリング・フィールド、並びに、多数のシンク・フィールドを包含している。尚、該制御端子は、少なくとも一つのスプリング・フィールド、或いは、シンク・フィールドを完全に取り囲んでいる。また本発明に係るある一つのトランジスターは、複数のトランジスター・セルを基質上に有しているが、各々のトランジスター・セルは、一つのスプリング・コンタクト・フィールド、及び/或いは、一つのシンク・コンタクト・フィールドを包含している。スプリング・コンタクト・フィールドは、基質の裏側において互いに導通するようにつながれており、シンク・コンタクト・フィールドも、基質の裏側において互いに導通するようにつながれている。本発明に係るトランジスターの製造方法は、以下の工程を包含している:基質を準備する;基質上に、一つの制御端子、多数のスプリング・フィールド、多数のシンク・フィールドを有する多数のトランジスター・セルを形成する;制御端子を互いに導通するようつなぐ;各トランジスター・セルにスプリング・コンタクト・フィールド、及び/或いは、シンク・コンタクト・フィールドを形成する;各トランジスター・セルのスプリング・フィールドとスプリング・コンタクト・フィールドを導通するようにつなぐ;各トランジスター・セルのシンク・フィールドをシンク・コンタクト・フィールドと導通するようにつなぐ;少なくとも一つのバンプを各スプリング・コンタクト・フィールドと各シンク・コンタクト・フィールドに形成する;配線基板を用意する;スプリング・コンタクト・フィールドのバンプを互いに導通するように配線基板上の配線路を介して接続する;そして、シンク・コンタクト・フィールドのバンプを互いに導通するように配線基板上の配線路を介して接続する。このようなバンプと配線基板上の配線路の配置により、ワイヤー・ボンディングが半導体表面に設けられることを低減できる。スプリング・フィールド、シンク・フィールド及び制御端子のバンプに対する本発明に係る配置は、アクティブなトランジスター領域とバンプ間の熱抵抗を低減できるものである。  (もっと読む)

(もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】本発明は、化合物半導体素子の動作に関係なく、リーク電流を防止することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置1は、2DEG310を有する第1の化合物半導体層31と、第1の化合物半導体層31上に配設され、キャリア供給層として機能する第2の化合物半導体層32と、2DEG310上に配設された第1の電極61と、2DEG310上において第1の電極61から離間して配設された第2の電極42と、を備えた化合物半導体素子10と、化合物半導体素子10の周囲を取り囲む領域の一部において2DEG310上に配設され、この2DEG310のキャリア濃度を低減させる外周電極62を有する外周領域11とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数に分割された接続部とこれらの接続部の間に形成された抵抗体とが、電極パッドにより良好に接続される半導体装置の製造方法を提供すること。

【解決手段】複数のFET12が化合物半導体基板11上に並列に形成され、ゲートパッド27が複数に分割された半導体装置の製造方法であって、化合物半導体基板11上に抵抗体22を形成する工程と、抵抗体22上にこの抵抗体22を保護する保護パターン23を形成する工程と、複数のFET12、抵抗体22および保護パターン23を含む化合物半導体基板11上に保護膜24を形成する工程と、複数のFET12の各電極13、14、15をそれぞれ接続する電極接続部17、18、21上および保護パターン23上の保護膜24をエッチングにより除去する工程と、エッチングにより除去した位置に電極パッド25、26、27を形成する工程と、を具備する。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗の上昇を抑制しつつ閾値電圧を大きくできる電界効果トランジスタを提供する。

【解決手段】キャリア走行層13である第1窒化物半導体層13と、第1窒化物半導体層13の上に設けられた、第1窒化物半導体層よりもバンドギャップエネルギーの大きい第2窒化物半導体層14と、第2窒化物半導体層14の上に順に設けられた、InGaN16層と、p型窒化物半導体層18と、ゲート電極22とを備える電界効果トランジスタであって、InGaN層16は、ゲート電極22直下の表面に第1の凹部19を有する。これにより、オン抵抗を一定に抑えつつ、閾値電圧を大きくすることができ、ノーマリオフ型のトランジスタが実現できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ハイサイド駆動部62からの駆動信号を受ける第1のスイッチング機能部と、ローサイド駆動部64からの駆動信号を受ける制御電極とを有する第2のスイッチング機能部とを備え、ハイサイド駆動部62は、ノーマリーオン型の電界効果トランジスタを含み、スイッチング制御信号の基準電圧を出力ノードの電位へシフトした駆動信号を出力し、第1のスイッチング機能部はノーマリーオン型の第1の電界効果トランジスタTr1を含み、第2のスイッチング機能部はノーマリーオン型の第2の電界効果トランジスタTr2を含み、ハイサイド駆動部62および第1の電界効果トランジスタTr1は第1の半導体チップ71に含まれている。

(もっと読む)

半導体装置

【課題】静電破壊対策においてペレットサイズに影響を与えず、かつレイアウトに影響されない構成とする。

【解決手段】FET領域200に形成されたFETと、周囲領域202において、基体表面に形成された第1の不純物拡散領域106aと、それぞれ第1の不純物拡散領域106aの一端107aおよび他端107b上に形成された第1のオーミックメタル端子114aおよび第2のオーミックメタル端子114dとを含むゲート抵抗107と、平面視において、ゲート抵抗107の一端107aとゲート電極122との間には、ドレイン不純物拡散領域106bおよびドレイン電極114bの組合せ、またはソース不純物拡散領域106cおよびソース電極114cの組合せの一方が存在し、当該組合せの一方は、ゲート抵抗107の一端107aと他端107bとを結ぶ直線を遮るように、FET領域200から延在して形成された遮断部134を含む。

(もっと読む)

101 - 120 / 230

[ Back to top ]