Fターム[5F102GV03]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | ボンディング、パッド構造 (230)

Fターム[5F102GV03]に分類される特許

81 - 100 / 230

半導体装置およびその製造方法

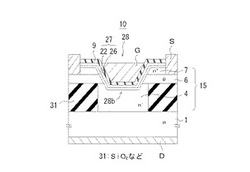

【課題】開口部にチャネルを備える縦型半導体装置において、高周波特性を向上することができる半導体装置およびその製造方法を提供する。

【解決手段】 n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を有し、開口部28は表層からn型GaN系ドリフト層内にまで届いており、該開口部を覆うように位置する電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、ドレイン電極Dと、再成長層上に位置するゲート電極Gとを備え、ソース電極を一方の電極とし、またドレイン電極を他方の電極としてコンデンサを構成するとみて、該コンデンサの容量を低下させる容量低下構造を備えることを特徴とする。

(もっと読む)

半導体装置及び電源装置

【課題】半導体装置において、抵抗が増大して変換効率が低下してしまうのを防止する。

【解決手段】半導体装置を、基板2上に形成されたGaN系半導体積層構造3を有する第1トランジスタQ1と、GaN系半導体積層構造を有する第2トランジスタQ2とを備え、第1トランジスタが、複数の第1フィンガ8AXを有する第1ゲート電極8Aと、複数の第1ドレイン電極9Aと、複数の第1ソース電極10Aとを備え、第2トランジスタが、複数の第2フィンガ8BXを有する第2ゲート電極8Bと、複数の第2ドレイン電極9Bと、複数の第2ソース電極10Bとを備え、複数の第1ドレイン電極の上方又は下方に接続されたドレインパッド15と、複数の第2ソース電極の上方又は下方に接続されたソースパッド25と、複数の第1ソース電極及び複数の第2ドレイン電極に接続された共通パッド35とを備えるものとする。

(もっと読む)

電界効果トランジスタ

【課題】発熱領域が集中して配置されていることによって熱抵抗が増大することを防止し、チップ面積を大きくすることなく発熱領域を分散させる電界効果トランジスタを提供する。

【解決手段】実施形態に係る電界効果トランジスタは、単位FETをゲートフィンガー電極複数本をまとめて一個のセル11とし、チップの長手方向にフィンガー電極を平行にして配置したものである。各セル11間の隙間には、ソースフィンガー電極13aを接続したバイアホール12付ソース電極配線13と、ゲートフィンガー電極14aを接続したゲート電極配線14と、が対称性を鑑みて配置される。また、各ゲート電極配線14は、ゲートバスライン17に接続される。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。トランジスタ及び配線を覆う形状に加工されたシート、テープ、又は基板を、トランジスタ及び配線を覆って半導体基板の上面上に貼り付ける。

(もっと読む)

半導体装置

【課題】ゲートパッド電極と裏面金属電極間のリーク電流を抑制し、ボンディング強度を向上させ、高性能化・高信頼化を図る。

【解決手段】基板10の第1表面上に配置され、それぞれ複数のフィンガーを有するゲート電極24・ソース電極20およびドレイン電極22およびオーム性電極層18と、ゲート電極・ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極GE1〜4・ソース端子電極SE1〜4およびドレイン端子電極DEと、オーム性電極層上に配置され、ゲート端子電極と接続するゲートパッド電極30と、オーム性電極層と基板との界面に形成された反応層を覆うように基板内に形成された第1導電型半導体層16と、第1導電型半導体層16を覆うように、基板内に形成され、第1導電型と反対導電型の第2導電型半導体層とを備える半導体装置1。

(もっと読む)

大面積シリコン基板及びその他の基板上の多層III族窒化物バッファの成長

【課題】半導体基板上に第1エピタキシャル層を形成し且つ該層をエッチングして複数の分離領域を形成することを包含する方法を提供する。

【解決手段】本方法は、エッチングした第1エピタキシャル層106a上に第2エピタキシャル層106bを形成することを含む。106a,b層は少なくとも1個のIII族窒化物を含み、106a,b層は一緒になって1個のバッファ106を形成する。本方法は、更に、該バッファ上に装置層108を形成し、且つ該装置層を使用して半導体装置を製造することを包含している。106b層は、実質的に106a領域上にのみ存在する106b領域を包含することが可能である。106b層は、又、106a領域及び該基板を被覆することが可能であり、且つ106b層はエッチングするか又はしない場合がある。該装置層は106b層を形成するために使用するのと同じ操作期間中に形成することが可能である。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。上面が開口した枠体を、トランジスタの周囲を取り囲んで、半導体基板の上面上に形成する。枠体上にテープを貼り付けることにより、枠体及びテープによってトランジスタ及び配線を覆う。

(もっと読む)

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

半導体装置

【課題】作製プロセスに起因する特性劣化を生ぜず、ボンディングパッドの電位変化による特性変化を受け難い小型化した半導体装置を提供する。

【解決手段】半導体装置10は、アクティブ領域12と、アクティブ領域12を覆う第1の絶縁層13と、第1の絶縁層13上に形成されるフローティング導体14と、第1の絶縁層13上およびフローティング導体14上に形成される第2の絶縁層15と、第2の絶縁層17上に形成されたボンディングパッド18と、アクティブ領域12とボンディングパッド18を電気的に接続する導通ビア19,20と、を有する。

(もっと読む)

窒化物半導体装置

【課題】活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、活性領域102Aを有する窒化物半導体層積層体102と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極131及び第2の電極132とを備えている。第1の電極の上に接して第1の電極配線151が形成され、第2の電極の上に第2の電極配線152が接して形成されている。第1の電極配線及び第2の電極配線を覆うように第2の絶縁膜が形成され、第2の絶縁膜の上に第1の金属層161が形成されている。第1の金属層は、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。

(もっと読む)

半導体装置

【課題】出力を大きくすることが可能な半導体装置を提供すること。

【解決手段】半導体基板10上に設けられ、ソースパッド12aと、ソースパッド12aと接続された一端から他端に向けて長さが小さくなる階段状の側部12cを有するソースフィンガー12bと、を含むソース電極12と、ドレインパッド14aと、ドレインパッド14aと接続された一端から他端に向けて長さが小さくなり、側部12cと対向する側部14cを有するドレインフィンガー14bと、を含むドレイン電極14と、ソースフィンガー12bの段差12dと、ドレインフィンガー14bの段差14dとの間に屈曲部16cを有し、ソースフィンガー12a及びドレインフィンガー14aに沿って屈曲するゲート電極16と、を具備し、側部12cの形状と側部14cの形状とは、ソースフィンガー12bの他端とドレインフィンガー14bの他端とを結ぶ線分9の中点に対して対称である半導体装置。

(もっと読む)

接合型電界効果トランジスタ

【課題】 従来のJ−FETでは、動作領域内のゲート領域(トップゲート領域)は、動作領域外周に設けられた深いゲート領域を介してのみ、半導体基板(バックゲート領域)と接続していた。このため動作領域の中央と外周ではゲート抵抗にばらつきが生じ、ゲート抵抗の増加によるノイズ電圧の増加や、不均一動作によるゲインの低下が問題であった。

【解決手段】 格子状のゲート領域(トップゲート領域)を有するJ−FETにおいて、行列状にソース領域と交互に配置されていたドレイン領域の一部を深いゲート領域に置き換え、動作領域内にも深いゲート領域を設ける。ドレイン領域を一部省くことで生じるドレイン電流の流れない無効領域をできる限り減らすため、ソース領域が配置されるセルについてドレイン電流が流れない方向のゲート領域を短くする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電位の位相差を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板と、基板上方に形成された電子走行層と、電子走行層上方に形成された電子供給層と、電子供給層上方に形成された複数のゲート電極5gと、複数のゲート電極5gが接続されたゲートパッド8gと、が設けられている。ゲート電極5gのゲート幅がゲートパッド8gから離間するほど小さくなっている。

(もっと読む)

ハイパワーGaNベースFET用のレイアウトデザイン

【課題】FETを提供する。

【解決手段】FETは、基板と、基板上に配置されたバッファ層と、バッファ層上に配置されたチャネル層と、チャネル層上に配置された障壁層とを含む。ソース、ゲート及びドレイン電極は障壁層上に配置されて長手方向に延伸する。チャネル及び障壁層の一部分は長手方向に延伸するメサ部を形成し、ソース及びドレイン電極がメサ部の縁を超えて延伸する。ゲート電極はメサ部の縁側壁に沿って延伸する。導電性ソース相互接続部は障壁層上に配置されソース電極に電気的に接続された第一の端部を有する。第一の誘電体層はバッファ層及びソース相互接続部上に配置される。ゲートビアは第一の誘電体層に形成される。導電性ゲートノードがバッファ層に沿って延伸して前記メサ部の側壁に沿って延伸するゲート電極の一部分に電気的に接続する。ゲートパッドはメサ部に隣接する第一の誘電体層上に配置される。

(もっと読む)

半導体装置

【課題】高周波モジュール中におけるスイッチング素子として用いられるHEMT素子を小型化する。

【解決手段】GaAsからなる基板1の主面上の素子分離部9で規定された活性領域内において、ゲート電極17は、1本で形成し、ソース電極13とドレイン電極14との間では紙面上下方向に延在し、それ以外の部分では左右方向に延在するようにパターニングすることにより、活性領域外に配置されるゲート電極17の割合を減じ、ゲートパッド17Aの面積を減じる。

(もっと読む)

半導体装置の製造方法

【課題】GaAsを材料として用いた基板の基板厚さのばらつきを抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】GaAs基板29上に、AlGaAsからなる基板厚制御層18を形成する工程と、基板厚制御層18上にGaAsからなるバッファ層17を形成する工程と、このバッファ層17上に電界効果トランジスタ16を形成する工程と、次亜塩素酸ナトリウム水溶液を用いて、GaAs基板29を、基板厚制御層18が露出するまで研磨する工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】 優れた縦方向耐圧を得た上で、安定して低いオン抵抗を確保することができる、半導体装置およびその製造方法を提供する。

【解決手段】n型ドリフト層4、p型層6、およびn型表層8、を含むGaN系積層体、に形成され、開口部28に露出するGaN系積層体を覆うチャネルを含む再成長層27が形成され、チャネルが電子走行層の電子供給層との界面に形成される二次元電子ガスであって、p型層6の厚みが、電子走行層22の厚みをdとして、d〜10dの範囲にあり、かつ、(p型層/n型表層)界面から該n型表層内へと、該p型層におけるp型不純物濃度から濃度が減少するp型不純物傾斜層7が設けられていることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

テラヘルツ波受信素子

【課題】テラヘルツ波を効率よく受信し、信号/雑音比を向上したテラヘルツ波受信素子を提供する。

【解決手段】第1の波長λ1のテラヘルツ波を受信するテラヘルツ波受信素子100であ

って、2以上の半導体層(バッファ層102aおよび電子供給層104a)のヘテロ接合により形成される2次元電子チャネル層103a、ゲート幅方向にλ1/2の長さを有するゲート電極111a、ドレイン電極113aおよびソース電極112aを有する第1のFET100aと、第1のFET100aのゲート電極111aのゲート幅方向における中央部と接続され、かつ、ゲート電極111aと直交するように配置されたゲート配線114aとを備える。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

81 - 100 / 230

[ Back to top ]