Fターム[5F102GV03]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | ボンディング、パッド構造 (230)

Fターム[5F102GV03]に分類される特許

21 - 40 / 230

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】耐圧をより向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体積層構造8と、基板1と化合物半導体積層構造8との間に形成された非晶質性絶縁膜2と、が設けられている。

(もっと読む)

半導体装置

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁耐圧が高く、オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、前記第1の半導体層の上に形成された第2の半導体層14と、前記第2の半導体層の上に形成された第3の半導体層15と、前記第3の半導体層の上に形成されたゲート電極21と、前記第2の半導体層に接して形成されたソース電極22及びドレイン電極23と、を有し、前記第3の半導体層には、半導体材料にp型不純物元素がドープされており、前記第3の半導体層は、前記ゲート電極の端部より、前記ドレイン電極が設けられている側に張出している張出領域を有していることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】特性の低下を抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、が含まれている。p型半導体層8に含まれるp型不純物として、少なくとも電子走行層3及び電子供給層5のいずれかを構成する元素と同種の元素が用いられている。

(もっと読む)

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

半導体装置

【課題】 本実施形態は、面積効率に優れた半導体装置を実現することを目的としている。

【解決手段】 本実施形態の半導体装置は、半導体基板と、半導体基板上に形成された電界効果トランジスタと、前記電界効果トランジスタの形成領域に隣接するダイオード形成領域とを備え、前記ダイオード形成領域は前記トランジスタの形成領域と前記半導体基板上で絶縁され、前記ダイオード形成領域内は櫛状に並んだアノード電極とカソード電極から形成され、前記アノード電極とカソード電極は、電界効果トランジスタを構成する櫛状にならんだゲート電極、ソース電極およびドレイン電極とは電極方向とは異なる方向となるように形成されることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

半導体装置

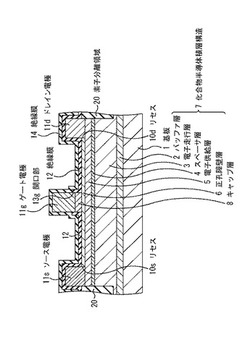

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】精密なエッチング制御を必要とすることなく、ビアホール構造を形成することを可能とするとともに、エッチング後の洗浄を容易にする。

【解決手段】半導体装置において、第1の基板11と、第1の基板表面に形成された素子領域12,13と、素子領域と接続され、第1の基板11上に形成された電極14,15,16と、第1の基板11と積層される第2の基板17と、第2の基板17を貫通し、電極上に配置されるビアホール18a,18b,18cと、ビアホール内に形成される金属層19a,19b,19cと、を備える。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層とオーミック電極とのコンタクト抵抗を低減できる窒化物半導体装置を提供する。

【解決手段】Si基板10上に形成されたアンドープGaN層1,アンドープAlGaN層2と、アンドープGaN層1,アンドープAlGaN層2上に形成されたTi/Al/TiNからなるオーミック電極(ソース電極11,ドレイン電極12)とを備える。上記オーミック電極中の酸素濃度を1×1016cm−3以上かつ1×1020cm−3以下とする。

(もっと読む)

21 - 40 / 230

[ Back to top ]