Fターム[5F102GV03]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | ボンディング、パッド構造 (230)

Fターム[5F102GV03]に分類される特許

121 - 140 / 230

半導体装置の製造方法

【課題】 半導体装置のビアホールにおける残渣物の残留を抑制することができ、かつ、半導体装置のデバイス特性不良、信頼性不良等を抑制することができる、半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、GaN系半導体層(11)が設けられたSiC基板(10)の第1主面の反対側の第2主面上にCuあるいはCu合金からなり部分的に開口を有するエッチングマスク(50)を形成する工程と、エッチングマスク(50)を利用したドライエッチングを実施し、底部の厚さ方向にGaN系半導体層(11)が残存したビアホールを形成する第1エッチング工程と、第1エッチング工程の後にエッチングマスク(50)を除去する除去工程と、除去工程の後に残存したGaN系半導体層(11)に対してドライエッチングを実施する第2エッチング工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、高周波高出力で使用可能な、化合物半導体高電子移動度トランジスタを提供する。

【解決手段】支持基板20の第1の主表面20a上に、チャネル層40及びバリア層50が積層されて構成される、化合物半導体高電子移動度トランジスタであって、ソース電極62が形成された領域を含む、支持基板の領域部分が金属部22であり、ドレイン電極64が形成された領域を含む、支持基板の他の領域部分がシリコン部24で構成される。

(もっと読む)

半導体装置

【課題】ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11上にGaN層12およびAlGaN層13がこの順で形成され、AlGaN層13上にドレイン電極14、ソース電極15およびゲート電極16が形成された半導体装置であって、ゲート電極16の下方には、SiC基板11を貫通するように第1の開口23が形成されている。さらに、GaN層12上に形成され、ソース電極15に接続されるソースパッド19の一部が、SiC基板11の裏面側から露出するように、第2の開口24が形成されている。そして、第1の開口23内にソースフィールドプレート電極25−1を形成すると同時に、第2の開口24から露出するソースパッド19に接触するようにSiC基板11の裏面に接地導体25−2を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型化とこれに伴う装置の特性の劣化の抑制とが同時に可能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

窒化物半導体装置

【課題】パッシベーション膜を形成した場合にも、界面リーク電流が抑制された窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101の上に形成された半導体層積層体102と、半導体層積層体102の上に互いに間隔をおいて形成された第1のオーミック電極131及びショットキー電極132と、半導体層積層体102の上を覆うパッシベーション膜141とを備えている。半導体層積層体102は、基板101の上に順次形成された第1の窒化物半導体層122、第2の窒化物半導体層123及びp型の第3の窒化物半導体層124を含む半導体層積層体102と有している。第3の窒化物半導体層141は、p型の不純物を含み第1のオーミック電極131とショットキー電極132との間に形成され且つショットキー電極132と接するように選択的に形成されている。

(もっと読む)

半導体装置

【課題】本発明は、絶縁領域において破壊が起こるのを防止できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、半導体基板と、前記半導体基板の上面側に設けられた不純物添加領域と、前記半導体基板の上面側において、イオン注入によって前記不純物添加領域の周囲に設けられた絶縁領域と、前記不純物添加領域上に設けられたゲート電極と、前記ゲート電極を挟むように前記不純物添加領域上に設けられた第1の電極及び第2の電極と、前記絶縁領域上に設けられ、前記ゲート電極に接続した第1のパッドと、前記絶縁領域上において前記不純物添加領域を挟んで前記第1のパッドと対向するように設けられ、前記第2の電極に接続した第2のパッドと、前記絶縁領域上において、前記第1の電極と前記第2のパッドの間に設けられた導体と、を備えることを特徴とするものである。

(もっと読む)

半導体装置及びその製造方法

【課題】過電圧に伴う破壊を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の一態様には、互いに並列に接続され、ゲート電極10、ソース電極9及びドレイン電極15を備えた複数の縦型トランジスタ32と、前記複数の縦型トランジスタ32を個別に取り囲むダイオード31と、が設けられている。前記ソース電極9に前記ダイオード31のアノード11が接続され、前記ドレイン電極15に前記ダイオードのカソード1が接続されている。

(もっと読む)

電力変換装置

【課題】電流コラプスを十分に緩和し、GaNトランジスタが本来有している低いオン抵抗を利用した高効率の電力変換装置を実現できるようにする。

【解決手段】電力変換装置は、電源が接続される入力端Vin1と、電源から供給された電力をスイッチングする第1のスイッチング素子10とを備えている。第1のスイッチング素子10は、基板11の上に形成された窒化物半導体からなる半導体層積層体13と、半導体層積層体13の上に形成されたゲート電極18、第1のオーミック電極16及び第2のオーミック電極17と、基板11の裏面に形成された裏面電極20とを有している。裏面電極20には第2のオーミック電極17との間の電位差が小さくなるように入力端Vin1に接続された電源から電位が供給される。第1のスイッチング素子10がオン状態の場合には、裏面電極20に正電圧のバイアスが印加される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、導電性バッファ層を用いることなく、煩雑なプロセスも必要なく、非常に高い深さ精度のドライエッチングも必要なく、また、結晶性を劣化させずに、効率良くホールを引き抜くことができるようにする。

【解決手段】半導体装置を、同一基板1上に形成され、(0001)面及び(000−1)面を有する窒化物半導体層4と、基板1と窒化物半導体層4との間に部分的に設けられた(0001)面形成層2と、(0001)面を有する窒化物半導体層4上に設けられたソース電極5、ドレイン電極6及びゲート電極7と、(000−1)面を有する窒化物半導体層4上に設けられたホール引き抜き電極8とを備えるものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

高周波半導体装置

【課題】任意の動作周波数に対して、最適な抵抗値を有する抵抗体をゲート端子電極間に選択配置可能であり、ループ発振を抑制する高周波半導体装置を提供する。

【解決手段】基板10の第1表面に配置され,それぞれ複数のフィンガーを有するゲートフィンガー電極24、ソースフィンガー電極20およびドレインフィンガー電極22と、ゲートフィンガー電極24、ソースフィンガー電極20およびドレインフィンガー電極22ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極、ソース端子電極およびドレイン端子電極とを有するFETセル40と、ゲート端子電極間に配置された抵抗体30とを備え、隣り合うFETセル40のゲート端子電極間の距離は、抵抗体30を配置する位置によって複数選択可能であり、ゲート端子電極は、抵抗体30の値が、パターンサイズの変更無しに、複数選択可能となる電極パターン形状を有する。

(もっと読む)

横型接合型電界効果トランジスタ

【課題】漏れ電流の発生を防止すると共に、十分な耐圧を実現することが可能な横型接合型電界効果トランジスタを提供する。

【解決手段】この発明に従った横型JFET10では、バッファ層11は、SiC基板1の主表面上に位置し、p型不純物を含む。チャネル層12は、バッファ層11上に位置し、バッファ層11におけるp型不純物の濃度より高い濃度のn型不純物を含む。n型のソース領域15およびドレイン領域16は、チャネル層12の表面層において互いに間隔を隔てて形成され、p型のゲート領域17は、チャネル層12の表面層においてソース領域15およびドレイン領域16の間に位置する。バリア領域13は、チャネル層12とバッファ層11との境界領域において、ゲート領域17の下に位置する領域に配置され、バッファ層11におけるp型不純物の濃度より高い濃度のp型不純物を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】所定の配線間距離を確保すると共に、配線間距離を確保するために形成される絶縁膜をパターニング等によって形成する際に、下層配線の損傷を防ぐ。

【解決手段】本発明に係る半導体装置は、半導体基板11と、半導体基板11上に形成された第1配線1と、半導体基板11上の第1配線1との交差部において、隙間9を介して第1配線1を跨ぐように形成された第2配線2と、交差部の第2配線2下において、少なくとも第1配線1を覆うように半導体基板11上に形成された保護膜8と、交差部の第2配線2下の保護膜8上において、保護膜8の端部よりも内側に形成され、交差部の第1配線1を覆うように島状に形成された絶縁膜3と、備えている。

(もっと読む)

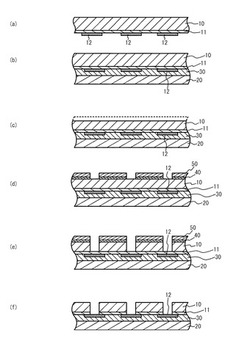

半導体装置およびその製造方法

【課題】ソース抵抗を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

基板10上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層12上に配置され、アルミニウム窒化ガリウム層18からなる活性領域AAと、活性領域上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、ゲート電極、ソース電極およびドレイン電極が延伸する方向の窒化物系化合物半導体層上に配置され、それぞれゲート電極、ソース電極およびドレイン電極に接続されたゲート端子電極GE1〜GE3、ソース端子電極SE1〜SE4およびドレイン端子電極DEと、ソース端子電極が配置される側の基板の端面に配置され、ソース端子電極と接続され、最外層のエッジが下地金属層よりも後退する3層以上の異なる多層金属を有する端面電極SC1〜SC4とを備え、ダイボンディング半田層がソース端子電極に到達するのを防止する。

(もっと読む)

帰還抵抗を有するフィールドプレートトランジスタ

実施形態は、これに限定されないが、ソース電極と、入力無線周波数(RF)信号を受信するゲート電極と、増幅されたRF信号を出力するドレイン電極と、を有する単位セルを含む装置とシステムを含む。フィールドプレートは前記ソース電極に連結され、帰還抵抗は前記フィールドプレートと前記ソース電極間に連結されてもよい。 (もっと読む)

複数のフィールドプレートを有する電界効果トランジスタ

実施形態には、これに限定されないが、電界効果トランジスタスイッチを含む装置とシステムが含まれる。電界効果トランジスタスイッチは、ゲート電極に連結され、ソース電極とドレイン電極から実質的に等距離に配置された第1のフィールドプレートを含んでいてもよい。また、該電界効果トランジスタスイッチは、前記第1のフィールドプレートに近接配置され、前記ソース電極と前記ドレイン電極から実質的に等距離に配置された第2のフィールドプレートを含んでいてもよい。前記第1および第2のフィールドプレートは、前記ソース電極とゲート電極間および前記ドレイン電極とゲート電極間の電界を低減するように構成されていてもよい。 (もっと読む)

電気的に絶縁された裏面を有するバンプ付き自己分離型GaNトランジスタチップ

【課題】本発明は、デバイスのシリコン基板を電気的に分離するためのAlNシード層を含むことにより、ヒートシンクと表面実装型デバイスの裏面との間の厚い電気絶縁体の必要性を取り除く。

【解決手段】シリコン基板と、化合物半導体材料と、前記シリコン基板と前記化合物半導体材料との間の絶縁材料と、電気的接続の手段及び不動態化材料を含む上面とを有し、前記不動態化材料は窒化シリコン、二酸化シリコン、又は両者の組み合わせである半導体デバイス。前記デバイスの側壁もまた前記デバイスの活性領域から電気的に絶縁されている。  (もっと読む)

(もっと読む)

テラヘルツ受信素子

【課題】高効率でテラヘルツ波を受信することが可能であるテラヘルツ受信素子を提供する。

【解決手段】本発明のテラヘルツ受信素子Aは、高抵抗基板1と、前記高抵抗基板1の第1の主面上に形成されているグランド面10と、前記高抵抗基板1の前記第1の主面に対向する第2の主面上に形成され、ヘテロ接合により形成されるチャネル層3を含む半導体層と、前記半導体層に形成され、前記チャネル層3とともに電界効果型トランジスタを形成するソース電極5、ゲート電極9及びドレイン電極6とを備え、前記半導体層は、前記ゲート電極9とショットキー接合されたストライプ状の凸部7を有し、前記ストライプ状の凸部7に含まれる複数の凸部それぞれは、前記ゲート電極9の下方において前記ソース電極5、前記ゲート電極9及び前記ドレイン電極6の並び方向に直交する。

(もっと読む)

テラヘルツ受信素子

【課題】さまざまな偏光特性を持つ電磁波、光波の存在下においても、テラヘルツ信号を正確に受信するテラヘルツ受信素子を提供する。

【解決手段】本発明のテラヘルツ受信素子は、2つの電界効果型トランジスタFET−A、FET−Bと、アンテナとしての2本のゲートワイヤ12、12’と、差分回路21とを有し、前記2本のゲートワイヤ12、12’のそれぞれは、対応する電界効果型トランジスタに電気的に接続され、2つの電界効果型トランジスタへの2つのゲートワイヤ12、12’の取り付け方向のなす角度は0°以外の一定の角度であり、差分回路21は、2つの電界効果型トランジスタのドレイン部から出力される2つの信号の差分を算出し、受信信号として出力する。

(もっと読む)

半導体装置

【課題】低オン抵抗と高耐圧とを同時に実現させることができる半導体装置を提供すること。

【解決手段】GaNからなる半導体基板12と、この半導体基板12の表面に形成されたn型拡散層11と、このn型拡散層11の表面の一部に形成されたn+型拡散層17と、n型拡散層11上に互いに離間して形成されたドレイン電極13及びソース電極14と、n+型拡散層17上に形成され、ドレイン電極13とソース電極14との間に形成されたゲート電極15と、ゲート電極15とドレイン電極13との間の半導体基板12に、深さ方向に延長形成され、内部が高抵抗体20で充填されたトレンチ19と、を具備する。

(もっと読む)

121 - 140 / 230

[ Back to top ]