Fターム[5F102GV03]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | ボンディング、パッド構造 (230)

Fターム[5F102GV03]に分類される特許

41 - 60 / 230

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

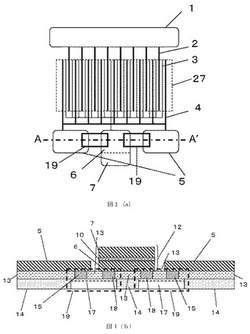

半導体素子の構造、半導体抵抗素子の製造方法およびFETスイッチ回路

【課題】薄膜抵抗又は基板抵抗によって数kΩから数十kΩの抵抗値を持つゲート抵抗のサイズが基板長さ、基板幅に比べて大きい。

【解決手段】能動層10を有する半導体基板11と、半導体基板の能動層10にオーミック接触するソース電極13及びドレイン電極14と、能動層10の上方に設けられたゲート電極15と、半導体基板11に設けられた非活性領域16と、非活性領域16上にゲート電極15の一部が引出されて接触する導体17と、非活性領域16上で直流電圧が印加されるパッド電極18と、パッド電極18及び導体17にオーミック接触し、非活性領域16に設けられたゲート抵抗領域19とを備え、ゲート抵抗領域19は半導体基板11へボロンイオンを注入することによって形成され、ボロンイオンの注入量によりゲート抵抗領域19上のシート抵抗値を高めたことを備えたことを特徴とする半導体素子の構造が提供される。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイス、及び伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを提供する。

【解決手段】予め歪みが加えられた拡張状態の弾性基板が与えられる。印刷可能な半導体構造の内面の少なくとも一部を、予め歪みが加えられた拡張状態の弾性基板の外面に対して結合される。半導体構造の内面を湾曲させることにより弾性基板を少なくとも部分的に緩和状態へと弛緩させる。湾曲した内面を有する半導体構造が弾性基板から他の基板、好ましくはフレキシブル基板へと転写される。

(もっと読む)

III−V族トランジスタとIV族ダイオードを含む積層複合デバイス

【課題】III−V族トランジスタとIV族ダイオードからなる積層複合デバイスを提供する。

【解決手段】積層複合デバイスはIV族ダイオードと該IV族ダイオードの上に積層されたIII−V族トランジスタとを備える。IV族ダイオードのカソードがIII−V族トランジスタのソースと接触され、IV族ダイオードのアノードがIII−V族トランジスタのゲートに結合されて前記複合デバイスパッケージの底面上の複合アノードを与え、III−V族トランジスタのドレインが複合デバイスパッケージの底面に対向する上面上の複合カソードを与える。

(もっと読む)

半導体装置

【課題】エアブリッジの強度を向上させる。

【解決手段】半導体層上に設けられ、互いに並列に配置された複数のソースフィンガー10と、半導体層上に設けられ、複数のソースフィンガー10と交互に配置された複数のドレインフィンガー12と、半導体層上に設けられ、ソースフィンガー10とドレインフィンガー12との間にそれぞれ配置された複数のゲートフィンガー14と、複数のゲートフィンガー14同士、複数のソースフィンガー10同士、および複数のドレインフィンガー12同士のいずれかを共通に接続するバスラインと、複数のソースフィンガー10、複数のドレインフィンガー12、および複数のゲートフィンガー14のいずれかに設けられ、バスライン上を跨ぐ複数の第1エアブリッジ24と、複数の第1エアブリッジ24同士の間を接続し、半導体層との間に空隙を有する第2エアブリッジ26と、を備える半導体装置。

(もっと読む)

半導体装置

【課題】横方向からのノイズに対するトランジスタ動作の影響を抑制する。

【解決手段】GaNを用いたHEMTが形成されたチップ30と、前記チップを搭載する導電性のステージ11と、前記ステージと前記HEMTのソースとに電気的に接続されたソースリード12と、前記HEMTのゲートに電気的に接続されたゲートリード14と、前記HEMTのドレインに電気的に接続されたドレインリード13と、を具備し、前記ソースリード、前記ドレインリードおよび前記ゲートリードの順に配列されている半導体装置。

(もっと読む)

III−V族トランジスタとIV族縦型トランジスタを含む積層複合デバイス

【課題】従来の共通基板上へのデバイスの並置構成は、電流通路の寄生のインダクタンス、抵抗、及びパッケージの放熱要件を増大し、製造コストも増大するため、III−窒化物又は他のIII−V族トランジスタをIV族ダイオードと一体化するコンパクトでコストエフェクティブなパッケージングを提供する。

【解決手段】積層複合デバイスはIV族縦型トランジスタ120と該IV族縦型トランジスタの上に積層されたIII−V族トランジスタ110とを備える。IV族縦型トランジスタのドレインがIII−V族トランジスタのソースと接触され、IV族縦型トランジスタのソースが前記積層複合デバイスの底面の複合ソースを与えるためにIII−V族トランジスタのゲートに結合され、III−V族トランジスタのドレインが積層複合デバイスの上面の複合ドレインを与える。IV族縦型トランジスタのゲートが前記積層複合デバイスの上面の複合ゲートを与える。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

半導体装置のデバイス実装構造

【課題】 GaNを用いる半導体装置の低消費電力および高速応答特性のメリットを生かすことのできるデバイス実装構造を実現する。

【解決手段】

ソースリード15とダイパッド14が一体成形されたリードフレームを用いて、当該ダイパッド上にGaNデバイス10を搭載する。そして、GaNデバイスのソース端子11を、ダイパッド14とワイヤボンディングして実装される。これにより、チップ裏面からのリーク電流を減らし、オン抵抗を低減するとともに、ゲート−ソース間のループ電流を減らし、ソース配線側の寄生インダクタンスを低減することで、ゲート−ソース間の寄生容量を介したゲート電圧の発振を抑制する。

(もっと読む)

半導体装置

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

パッケージ

【課題】電流容量が高く、かつ生じる応力が低減されてクラックの発生が抑制され、信頼性の高いパッケージを提供する。

【解決手段】パッケージ外壁16と、パッケージ外壁16を貫通する貫通孔と、貫通孔にはめ込まれた凸状フィードスルー25と、凸状フィードスルー25に固定され端子電極21bとを備え、端子電極21bは、相対的に線熱膨張率は低いが抵抗率が高い第1の金属層90と、相対的に線熱膨張率は高いが抵抗率が低い第2の金属層80a,80bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】製造工程の効率化とパッシベーション膜の剥離の抑制とが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、金を含む配線30a及び配線30bを形成する工程と、配線30a及び配線30bに接して、窒化シリコン膜32をプラズマ気相成長する工程と、窒化シリコン膜32の製膜レートよりも大きな製膜レートのもと、窒化シリコン膜32に接し、窒化シリコン膜32よりもシリコン組成比が小さい窒化シリコン膜22をプラズマ気相成長する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

MMIC用パッケージ

【課題】チップサイズの大きい高周波部品(MMIC)とパッケージ端子間を接続するインダクタンス成分を抑制し、高周波特性を改善したMMIC用パッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート200上に配置され、入力端子24aおよび出力端子24bを有するMMIC基板24と、導体ベースプレート200上に配置され、MMIC基板24を囲むセラミック枠体180と、セラミック枠体180上に配置されたパッケージ入力端子21aおよびパッケージ出力端子21bと、MMIC基板24とセラミック枠体180との間の導体ベースプレート200上に配置された結合用基板25と、結合用基板25上に配置された結合ライン25aとを備え、パッケージ入力端子21aと結合ライン25a間、および結合ライン25aと入力端子24a間とが接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】比較的簡易な構成で、化合物半導体素子の低抵抗伝送を達成すると共に、半導体素子の十分な高放熱性を低コストで実現する半導体装置を得る。

【解決手段】表面に接続電極11が形成された化合物半導体素子10と、表面に接続電極28a及び凹部21が形成された樹脂回路基板20と、凹部21内で化合物半導体素子10を固定する金属材料32,33とを有する半導体パッケージであり、化合物半導体素子10は、凹部21内において、接続電極11,28aが近接するように偏倚した位置に固定されており、接続電極11,28aがワイヤ接続されており、金属材料32は、化合物半導体素子10の底面から側面の少なくとも一部まで被覆する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

41 - 60 / 230

[ Back to top ]