Fターム[5F102GV03]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | ボンディング、パッド構造 (230)

Fターム[5F102GV03]に分類される特許

61 - 80 / 230

化合物半導体装置及びその製造方法

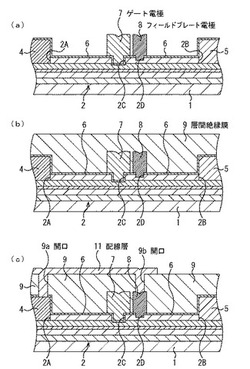

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

パッケージ

【課題】ベース面の反りの少ないパッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートとは異なる材料からなる金属壁16とを備え、導体ベースプレートは、対抗する1対の端面100a・100bが緩やかな弧を有し、金属壁も緩やかな弧を有しているので、接合時や基板実装時、キャップ半田付け時の反りの発生を抑制できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留りが高く信頼性の高いパッケージングされた半導体装置を提供する。

【解決手段】電極が形成された半導体チップと、前記電極に対応するリードと、前記電極と前記リードとを接続する金属配線と、前記金属配線と前記電極との接続部分及び前記金属配線と前記リードとの接続部分を覆う第1の樹脂部と、前記金属配線、前記第1の樹脂部及び前記半導体チップを覆う第2の樹脂部と、を有することを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】回路基板、リードフレームのステージなどの支持板上に半導体チップを実装する際に、半導体チップが移動や回転等の位置ずれを生じないようにする。

【解決手段】半導体装置の製造方法において、支持板2の半導体チップ実装領域2Aに、少なくとも外表面に金属を有する繊維状材料からなるシート5を載せ、半導体チップ実装領域2Aに、溶融金属を含む接合層3を形成し、半導体チップ実装領域2Aに、半導体チップ1を載せ、加熱することによって、溶融金属を含む接合層3によって半導体チップ1を半導体チップ実装領域2Aに接合する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】チャネル領域の低抵抗化を図りながら、ノーマリオフを実現する。

【解決手段】半導体装置を、キャリア走行層3及びキャリア供給層5を含む窒化物半導体積層構造と、窒化物半導体積層構造の上方に設けられ、活性化領域10と不活性領域10Aとを有するp型窒化物半導体層6と、p型窒化物半導体層の不活性領域上に設けられたn型窒化物半導体層7と、p型窒化物半導体層の活性化領域の上方に設けられたゲート電極13とを備えるものとする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】回路基板やリードフレームのステージなどの支持板上に半導体チップを実装する際に、半導体チップが移動や回転等の位置ずれを生じないようにする。

【解決手段】半導体装置の製造方法であって、支持板2の半導体チップ実装領域2A及び半導体チップ1の裏面の一方に、第1金属を含む層5及び第2金属を含む層6の一方を形成し、半導体チップ実装領域及び半導体チップの裏面の他方の、第1金属を含む層及び第2金属を含む層の一方が形成された領域の一部に相当する領域に、第1金属を含む層及び第2金属を含む層の他方を形成し、半導体チップ実装領域に半導体チップを位置合わせし、第1金属及び第2金属を含む合金を含む層9を形成して、半導体チップを半導体チップ実装領域に接合する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜を有する窒化物半導体を低コストで製造する。

【解決手段】基板10の上方に形成された半導体層22,23,24と、前記半導体層の一部を酸化することにより形成された絶縁膜30と、前記絶縁膜上に形成された電極41と、を有し、前記絶縁膜は、酸化ガリウムを含むもの、または、酸化ガリウム及び酸化インジウムを含むものにより形成されているものであることを特徴とする半導体装置。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】耐湿性及び耐電圧性を確保しながら、デバイス特性が劣化しないようにする。

【解決手段】半導体装置を、キャリア走行層及びキャリア供給層を含む窒化物半導体積層構造を備える半導体チップ1と、半導体チップの表面を覆い、カップリング剤を含有する第1樹脂層5と、第1樹脂層の表面を覆い、界面活性剤を含有する第2樹脂層6と、第1樹脂層及び第2樹脂層で覆われた半導体チップを封止する封止樹脂層7とを備えるものとする。

(もっと読む)

半導体装置

【課題】素子温度の上昇を抑制する半導体装置を提供する。

【解決手段】動作周波数fで動作可能な半導体装置であって、熱拡散率Dの基板と、基板上に形成され、ワイドギャップ半導体素子で横型素子の第1のトランジスタで構成される第1の素子ユニット12と、基板上に第1の素子ユニット12に隣接して形成され、第1のトランジスタと異なるタイミングで動作するワイドギャップ半導体素子で横型素子の第2のトランジスタで構成される第2の素子ユニット14とを備え、第1の素子ユニット12の重心と、第2の素子ユニット14の重心との距離が熱拡散長(D/πf)1/2の2倍以下であることを特徴とする半導体装置。

(もっと読む)

パッケージ

【課題】導体ベースプレートと金属外壁との熱膨張係数が異なることに伴う、銀ロウ付けする際の導体ベースプレートの反りを抑制したパッケージを提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートと接する面に複数の開放部を有する金属壁と、開放部を充填するブロックとを備えるパッケージ。

(もっと読む)

半導体装置

【課題】導体ベースプレート上に実装するSiCやダイヤモンドを基板とする高周波半導体チップの割れを防止する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された高周波半導体チップとを備え、高周波半導体チップは、四隅が面取りされている半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】半導体装置において、セルフターンオンが発生しないようにし、安定した動作を実現する。

【解決手段】半導体装置を、基板1と、基板の上方に設けられ、電子走行層6及び電子供給層7を含む半導体積層構造2と、半導体積層構造の上方に設けられたゲート電極3、ソース電極4及びドレイン電極5と、ゲート電極、ソース電極及びドレイン電極の上方に設けられ、ゲート電極、ソース電極及びドレイン電極のそれぞれに接続されたゲートパッド10、ソースパッド11及びドレインパッド12と、ゲートパッド、ソースパッド及びドレインパッドの下方に設けられた導電層1とを備えるものとし、ゲートパッドとソースパッドとの間の距離を、ゲートパッドとドレインパッドとの間の距離よりも小さくする。

(もっと読む)

高周波回路

【課題】最小ループと2セルループのオッドモード発振を共に抑制する高周波回路を提供する。

【解決手段】半導体基板上に並列に配列された複数のトランジスタと、第1の絶縁基板上に配置され、複数のトランジスタのゲート端子電極にそれぞれ接続された複数の入力整合回路と、第1の絶縁基板上に配置され、入力整合回路に隣接して配置された入力側第4発振抑制抵抗と、入力側第4発振抑制抵抗に直列接続された入力側第1キャパシタと、隣接する入力整合回路間を繋ぐ伝送線路上の点と入力側第1キャパシタ間に接続された入力側第1インダクタとを有する入力側発振抑制回路とを備え、入力側第1インダクタのインダクタンス値をL1、入力側第1キャパシタのキャパシタンス値をC1とすると、1/{2π(L1×C1)1/2}で表される入力側第1インダクタと入力側第1キャパシタの共振周波数が、2セルループの発振周波数fosc2に等しい高周波回路。

(もっと読む)

窒化物半導体素子および窒化物半導体パッケージ

【課題】GaN電子走行層の厚さを広い範囲で選択することができ、デバイス設計の自由度を高めることができる窒化物半導体素子、および耐圧および信頼性に優れる窒化物半導体素子パッケージを提供すること。

【解決手段】基板41上に、AlN層47、第1AlGaN層48(平均Al組成50%)および第2AlGaN層49(平均Al組成20%)からなるバッファ層44を形成する。バッファ層44上には、GaN電子走行層45およびAlGaN電子供給層46からなる素子動作層を形成する。これにより、HEMT素子3を構成する。

(もっと読む)

窒化物半導体装置

【課題】ゲート電極から染み出した金属がドレイン電極に到達することを抑制して、ドレイン−ゲート間の絶縁破壊を抑制する窒化物半導体装置を提供する。

【解決手段】ゲート電極5の直下に位置するAlGaN層22と、このAlGaN層22の直上に位置する絶縁膜30との間の界面Sに、ゲート電極5とドレイン電極1との間に位置するように、溝50を設けている。ゲート電極5から界面Sを伝ってドレイン電極1側へ染み出した金属を、溝50によって、堰き止めることができる。

(もっと読む)

窒化物半導体素子および窒化物半導体パッケージ

【課題】トランジスタ動作のオフ時におけるリーク電流を低減することができる窒化物半導体素子、およびリーク電流が少なく、信頼性に優れる窒化物半導体素子パッケージを提供すること。

【解決手段】基板41上に、AlN層47、第1AlGaN層48(平均Al組成50%)および第2AlGaN層49(平均Al組成20%)からなるバッファ層44を形成する。バッファ層44上には、GaN電子走行層45およびAlGaN電子供給層46からなる素子動作層を形成する。これにより、HEMT素子3を構成する。このHEMT素子3において、GaN電子走行層45の厚さ方向途中部に、BNとGaNとの混晶からなるBGaN部50を形成する。

(もっと読む)

61 - 80 / 230

[ Back to top ]