Fターム[5F102GV05]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097)

Fターム[5F102GV05]の下位に属するFターム

多層構造 (291)

SiO2膜 (488)

Si3N4膜 (770)

ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV05]に分類される特許

141 - 160 / 405

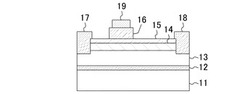

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

窒化物半導体装置

【課題】高電圧印加時にフィールドプレート構造端に集中する電界強度を緩和し、高耐圧で信頼性の高い窒化物半導体装置を提供する。

【解決手段】フィールドプレート構造を備えた窒化物半導体装置において、ゲート電極18に、オフ制御の制御電圧を印加するとき、フィールドプレート構造の傾斜面部直下の窒化物半導体層中13にはキャリアが存在しないようにする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

化合物半導体装置の製造方法

【課題】高い信頼性を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体層1上に、高融点金属を含む第1の導電膜3を形成する。第1の熱処理を行うことにより、第1の導電膜3と窒化物半導体層1とを反応させて高融点金属の窒化物層4を形成すると共に、窒化物半導体層1の表面に窒素空孔を生じさせる。第1の導電膜2上に、Alを含有する第2の導電膜3を形成する。第2の熱処理を行うことにより、第2の導電膜3中のAl原子を窒化物半導体層1の表面まで拡散させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数に分割された接続部とこれらの接続部の間に形成された抵抗体とが、電極パッドにより良好に接続される半導体装置の製造方法を提供すること。

【解決手段】複数のFET12が化合物半導体基板11上に並列に形成され、ゲートパッド27が複数に分割された半導体装置の製造方法であって、化合物半導体基板11上に抵抗体22を形成する工程と、抵抗体22上にこの抵抗体22を保護する保護パターン23を形成する工程と、複数のFET12、抵抗体22および保護パターン23を含む化合物半導体基板11上に保護膜24を形成する工程と、複数のFET12の各電極13、14、15をそれぞれ接続する電極接続部17、18、21上および保護パターン23上の保護膜24をエッチングにより除去する工程と、エッチングにより除去した位置に電極パッド25、26、27を形成する工程と、を具備する。

(もっと読む)

へテロ接合電界効果トランジスタ及びその製造方法

【課題】ゲートリーク電流の増大を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明の窒化物半導体からなるヘテロ接合電界効果トランジスタは、バリア層4と、バリア層4上に設けられたキャップ層5と、キャップ層5に下部を埋没するようにしてキャップ層5上に設けられたゲート電極10と、ゲート電極10の両側に離間して夫々設けられたソース電極9及びドレイン電極8と、を備える。ゲート電極10とドレイン電極8の間である第1領域及びゲート電極10とソース電極9の間である第2領域のうち、少なくとも第1領域のキャップ層5において少なくとも1箇所にトレンチが形成される。

(もっと読む)

半導体素子およびその製造方法

【課題】より高いブレークダウン電圧に適した半導体素子構造およびその製造方法を提供する。

【解決手段】半導体基板構造(100)は、半導体基板(1)と、半導体基板(1)の上部にGaNタイプの層スタック(20)とを備える。GaNタイプ層スタック(20)は、少なくとも1つのバッファ層(21,22)と、第1活性層(2)と、第2活性層(3)とを備え、第1活性層と第2活性層の界面において、能動素子領域が規定可能である。半導体基板(1)は、絶縁層(12)の上に存在しており、所定のパターンに従って溝(14)を規定するようにパターン化され、そのパターンは、こうした能動素子領域の下地となる少なくとも1つの溝(14)を含み、前記溝(14)は、絶縁層(12)から、GaNタイプ層スタック(20)の少なくとも1つのバッファ層(21,22)の中まで延びて、前記少なくとも1つのバッファ層(22)の範囲で過成長しており、第1および第2活性層(2,3)は、少なくとも能動素子領域の範囲で連続している。

(もっと読む)

接合型電界効果トランジスタおよびその製造方法

本願は、ドレイン(140)と、ゲート(160)と、ソース(130)と、を有し、ドレイン(140)およびソース(130)が、第1の型の半導体領域によって形成される、電界効果トランジスタに関する。一局面では、電界効果トランジスタはまた、ゲート(160)とドレイン(140)の中間のさらなるN+領域(410)等のさらにドープされた領域を含む。さらにドープされた領域は、電界効果トランジスタの中間ドレインとして見なすことができる。いくつかの実装では、さらにドープされた領域は、高濃度にドープすることができる。さらにドープされた領域によって、ドレイン(140)周囲の電界勾配を減少させることができる。  (もっと読む)

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリセス構造を採用してノーマリーオフ動作を可能とするも、バラツキの小さい安定した閾値を有し、十分な高耐圧を実現する信頼性の高い化合物半導体装置を実現する。

【解決手段】電子走行層3と電子供給層4との間にi−AlNからなる中間層5を形成し、キャップ構造7上のゲート電極の形成予定部位に中間層5をエッチングストッパとして用いて開口11aを形成した後、中間層5の開口11aに位置整合する部位に熱リン酸を用いたウェットエッチングにより開口11bを形成して、開口11a,11bからなる開口11をゲート絶縁膜12を介して下部が埋め込み、上部がキャップ構造7上方に突出するゲート電極13を形成する。

(もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】ノーマリオフでオン抵抗の低いHFETを実現すること。

【解決手段】HFET100は、第1キャリア走行層103上の互いに離間した2つの領域上に、2つに分離して形成されたノンドープのGaNからなる第2キャリア走行層104と、2つの分離した第2キャリア走行層104上にそれぞれ位置するAlGaNからなるキャリア供給層105を有している。第2キャリア走行層104とキャリア供給層105は、第1キャリア走行層103上に選択的に再成長させて形成した層である。第2キャリア走行層104とキャリア供給層105のヘテロ接合界面110は平坦性が高く、そのヘテロ接合界面110近傍は再成長に伴って混入した不純物はほとんど見られないため、2DEGの移動度を低下させることがなく、オン抵抗が低減されている。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】本発明は、耐圧特性を維持したままアクセス抵抗を低減して高速動作が可能な窒化物半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明による窒化物半導体装置は、窒化物半導体を用いたヘテロ接合電界効果型の半導体装置であって、基板1上に順次積層して形成されたチャネル層3およびバリア層4と、バリア層4上に離間して形成されたソース電極5およびドレイン電極6とを備え、ソース電極5およびドレイン電極6のそれぞれの下方であり、かつ、バリア層4の表面からチャネル層3の少なくとも一部までの領域に対して、不純物拡散を行うことによって不純物拡散領域22を設け、バンドギャップを変化させることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】

【解決手段】本発明は基板と、該基板上のGaNを含む第1層とAlGaNを含む第2層とを含む構成を含む半導体装置に関する。第1層上に第2層を堆積させ、第1層及び第2層は少なくとも部分的に基板を被覆する。また該構造はダイヤモンドを含む第3層を含む。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法及び通信装置

【課題】オン抵抗の上昇を抑制し、かつ、オフ容量を低減することができる電界効果トランジスタ、電界効果トランジスタの製造方法及び通信装置を提供する。

【解決手段】化合物半導体基板10の一面側に、バッファ層11、下部ドーピング層12、下部スペーサ層13、チャネル層14、上部スペーサ層15、上部ドーピング層16、拡散層17をこの順に積層し、拡散層17上の一部にゲート電極18、ソース電極19及びドレイン電極20を形成する。また、ゲート電極18とソース電極19及びドレイン電極20との間の領域にそれぞれ所定の間隔d2,d3を空けてp型半導体層21を形成すると共に、拡散層17のうちゲート電極18直下の部分にゲート領域23を形成する。

(もっと読む)

炭化ケイ素半導体構造体、デバイス及びその製造方法

【課題】炭化ケイ素(SiC)を含む半導体構造体(100)及びデバイスと、その製造方法を提供すること。

【解決手段】構造体(100)及びデバイスは、ベース又はシールド層(116)、チャネル(118)及び表面層(120)を備え、望ましくはすべてイオン注入によって形成される。その結果として本明細書に示す構造体及びデバイスは、ハードな「ノーマリオフ」デバイスであり、即ち約3V超の閾値電圧を示す。

(もっと読む)

ダイヤモンド薄膜およびダイヤモンド電界効果トランジスター

【課題】本発明の目的は、従来技術のデバイスのドレイン電流値が実用的には少なすぎ、試料を昇温すると、ある温度以上でドレイン電流が劇的に減少し、元に戻らず、デバイスが劣化するという問題を解決するダイヤモンド電界効果トランジスターおよびダイヤモンド多層膜。

【解決手段】ダイヤモンド上に水素を含む第1の表面層があり、その上にソース電極、ゲート電極、ドレイン電極が順に並んでおり、ソース電極−ゲート電極間、およびゲート電極−ドレイン電極間の上記ダイヤモンド結晶の第1の表面層上に、フッ素を含む保護層があることを特徴とするダイヤモンド電界効果トランジスター。

(もっと読む)

半導体装置及びその製造方法

【課題】過電圧に伴う破壊を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の一態様には、互いに並列に接続され、ゲート電極10、ソース電極9及びドレイン電極15を備えた複数の縦型トランジスタ32と、前記複数の縦型トランジスタ32を個別に取り囲むダイオード31と、が設けられている。前記ソース電極9に前記ダイオード31のアノード11が接続され、前記ドレイン電極15に前記ダイオードのカソード1が接続されている。

(もっと読む)

半導体装置

【課題】本発明は、絶縁領域において破壊が起こるのを防止できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、半導体基板と、前記半導体基板の上面側に設けられた不純物添加領域と、前記半導体基板の上面側において、イオン注入によって前記不純物添加領域の周囲に設けられた絶縁領域と、前記不純物添加領域上に設けられたゲート電極と、前記ゲート電極を挟むように前記不純物添加領域上に設けられた第1の電極及び第2の電極と、前記絶縁領域上に設けられ、前記ゲート電極に接続した第1のパッドと、前記絶縁領域上において前記不純物添加領域を挟んで前記第1のパッドと対向するように設けられ、前記第2の電極に接続した第2のパッドと、前記絶縁領域上において、前記第1の電極と前記第2のパッドの間に設けられた導体と、を備えることを特徴とするものである。

(もっと読む)

電子デバイス及びオーミック電極形成方法

【課題】低温短時間のアニールによっても、低いコンタクト抵抗を得ることのできるオーミック電極を備える電子デバイスを提供する。

【解決手段】電子デバイスは、ワイドバンドギャップ化合物半導体層16と、ワイドバンドギャップ化合物半導体層16上に形成されるオーミック電極であるソース電極18及びドレイン電極とを含む電子デバイスであって、オーミック電極は、密着層40、オーミック層42、及び、酸化防止層46が、ワイドバンドギャップ化合物半導体層16側からこの順に積層されて形成された電極であり、密着層40は、バナジウム(V)からなり、かつ、厚みが300Å以下であるようにする。

(もっと読む)

141 - 160 / 405

[ Back to top ]