Fターム[5F102GV05]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097)

Fターム[5F102GV05]の下位に属するFターム

多層構造 (291)

SiO2膜 (488)

Si3N4膜 (770)

ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV05]に分類される特許

81 - 100 / 405

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置の製造方法

【課題】特性が均一であって、歩留りの高い半導体装置の製造方法を提供する。

【解決手段】第1の半導体層12及び第2の半導体層13が順次形成されている半導体層の表面にレジストパターンを形成する工程と、前記レジストパターンの開口領域における前記第2の半導体層の一部または全部をドライエッチングにより除去しゲートリセス22を形成する工程と、前記レジストパターンを除去した後、ゲートリセスの底面及び側面に付着しているドライエッチング残渣23を除去する工程と、前記ドライエッチング残渣を除去した後、前記ゲートリセスの底面、側面及び前記半導体層上に絶縁膜31を形成する工程と、前記ゲートリセスが形成されている領域に前記絶縁膜を介しゲート電極を形成する工程と、前記半導体層上にソース電極及びドレイン電極を形成する工程と、を有する。

(もっと読む)

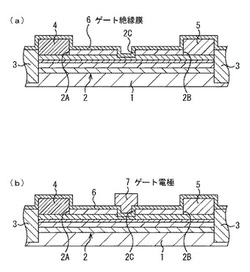

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜のダングリングボンドを確実に低減させて閾値電圧の変動を抑えて安定化させ、高いトランジスタ特性を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極7は、化合物半導体層2に形成された電極溝2C内に、ゲート絶縁膜6を介して一部が電極材料で埋め込まれて形成されており、ゲート絶縁膜6は、電極溝2C内において、少なくとも化合物半導体層2との界面に形成されたフッ素化合物を含有するAl−F化合物の複合層13aを有している。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】電流電圧のパルス特性を向上させて電流電圧のDC特性に近づける。

【解決手段】半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、ゲート絶縁膜上に設けられ、ゲート絶縁膜上におけるゲート電極の端部の少なくとも一部においてゲート電極と接するゲート境界膜と、を備え、ゲート境界膜およびゲート絶縁膜は、同種の絶縁材料を含む半導体装置を提供する。ゲート電極およびゲート境界膜上に設けられた絶縁性の保護膜を更に備え、保護膜は、ゲート境界膜およびゲート絶縁膜とは別種の絶縁材料を含んでよい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧が高く破壊等が生じにくい、信頼性の高い半導体装置を提供する。

【解決手段】基板上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層14と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスの底面は、中央部分23aが周辺部分23bに対し高い形状であることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層を加工することなく、比較的簡素な構成で確実なノーマリ・オフ動作を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2上にAlN等の第1の膜6及びAl2O3等の第2の膜7を順次に積層形成し、第2の膜7のゲート電極の形成予定部位に開口7aを形成し、開口7aをゲートメタルの一部で埋め込むように、ゲート電極8を形成し、ゲート電極のオフ時には、化合物半導体層2の電子走行層2bの2DEGがゲート電極8下の領域のみで消失する。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体62の上面からn型III族窒化物半導体64に到達する溝が形成されている場合、p型III族窒化物半導体の側面62aが露出する。p型III族窒化物半導体の露出面62aはn型化しやすく、露出面に沿ってリーク電流が流れやすい。

【解決手段】p型III族窒化物半導体62中に存在する正孔を露出面62aに誘導する正孔誘導手段を設ける。例えば、露出面62aを被覆する絶縁膜66に負電荷蓄積領域68を設ける。負電荷蓄積領域68が、p型III族窒化物半導体中に存在する正孔を露出面62aに誘導し、露出面がn型化して露出面に沿ってリーク電流が流れることを防止する。

(もっと読む)

半導体装置

【課題】J−FETのピンチオフ電圧のばらつき低減を図ること、及び低いピンチオフ電圧の実現を図ることが課題となる。

【解決手段】P型半導体基板5上にN型エピタキシャル層6を堆積する。前記N型エピタキシャル層6の表面にN+型ソース層3を形成する。前記N型エピタキシャル層6の表面に前記N+型ソース層3を取り囲んで1対のP+型ゲート層2a、2bを形成する。前記P+型ゲート層2bから離間した領域の前記N型エピタキシャル層6の表面にN+型ドレイン層1を形成する。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】本発明は、電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果型トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明のヘテロ接合電界効果型トランジスタは、バリア層4及びバリア層4上に形成されたキャップ層5を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして窒化物半導体層上に設けられたゲート電極10と、ゲート電極10の両側に離間して夫々設けられたドレイン電極8及びソース電極9とを備える。ゲート電極10のドレイン電極8側端面とソース電極9側端面のうち少なくともドレイン電極8側端面は、キャップ層5と少なくとも部分的に乖離しており、当該乖離部分が空隙である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ファインゲート構造を採用してゲート電極の微細化を図るも、ゲート電極の周辺における電界集中によるデバイス特性の変動・劣化を防止する、信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極8は、ファインゲート構造の幹状の下方部分8aと、下方部分8aの上端から当該上端よりも幅広に傘状(オーバーハング形状)に拡がる上方部分8bとが一体形成されており、下方部分8aは、下端を含む第1の部分8aaと、第1の部分8aa上の第2の部分8abとを有し、保護壁7は、第1の部分8aaの両側面のみを覆うように形成されている。

(もっと読む)

GaNベースの薄膜トランジスタの製造方法

【課題】電流特性と信頼性に優れ、閾値電圧が高いGaNベースの薄膜トランジスタを得ることができる製造方法を提供する。

【解決手段】GaNベースの薄膜トランジスタの製造方法は、n型GaNベースの半導体材を有する半導体エピタキシャル層を、基板上に形成する工程と、半導体エピタキシャル層上に絶縁体層を形成する工程と、絶縁体層上に、絶縁体層を部分的に露出するための開口部を有しているイオン注入マスクを形成する工程と、p型不純物を、開口部および絶縁体層を通してイオン注入して、n型GaNベースの半導体材の中にp型不純物がドーピングされた領域を形成し、その後、絶縁体層およびイオン注入マスクを除去する工程と、半導体エピタキシャル層上に誘電体層を形成する工程と、誘電体層を部分的に除去する工程と、ソース電極およびドレイン電極を形成する工程と、ゲート電極を形成する工程を含む。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】制御性の良い製造方法のみで形成することができる高周波数動作が可能なノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層4とショットキー接触する浮遊電極8を配置し、この浮遊電極8上に絶縁膜を介してゲート電極7を配置する。さらに、ソース電極5とドレイン電極6との間の電子供給層表面を珪素膜11で被覆する。そして、ゲート電極7に正バイアス印加し、浮遊電極8に電子を蓄積される。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 ゲート電極からソース及びドレインまでの領域を覆う絶縁膜が、寄生容量増大の要因になっている。

【解決手段】 半導体層を有する基板の上にゲート電極が形成されている。半導体層の上に、ゲート電極から相互に反対側に離れて、ソース電極及びドレイン電極が形成されている。ソース電極とドレイン電極との間の半導体層の上に、ソース電極及びドレイン電極から離れて配置されたゲート横絶縁膜が形成されている。ゲート横絶縁膜には、ゲート電極の下端が充填されたゲート用開口が設けられている。

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

【課題】窒化ガリウム材料デバイスおよびその形成方法を提供する。

【解決手段】該デバイスは、電極規定層24を包含する。電極規定層は典型的にはその内部に形成されたビア26を有し、該ビア内に電極18が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置

【課題】特性をさらに向上する半導体装置を提供する。

【解決手段】高電圧側電界効果トランジスタ20aの高電圧側ドレイン電極11aと、高電圧側ドレイン電極11aの一側方に間隔をおいて形成される高電圧側ゲート電極12aと、高電圧側ゲート電極12aの一側方に間隔をおいて形成され、高電圧側電界効果トランジスタ20aのソース電極であり、低電圧側電界効果トランジスタ21aのドレイン電極であるソース兼ドレイン電極13aと、ソース兼ドレイン電極13aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ゲート電極14aと、低電圧側ゲート電極14aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ソース電極15aとを有する。

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法

【課題】本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。

【解決手段】このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。

(もっと読む)

半導体装置の製造方法および半導体基板

【課題】所望のレジストパターンが形成可能な、インジウムおよび/またはアルミニウムを含む第1の層からなるフィールド領域を有する半導体装置の製造方法を提供する。

【解決手段】インジウムおよび/またはアルミニウムを含む第1の層からなるフィールド領域と、第1の層および第1の層とは異なる半導体層からなるメサ領域と、を備える半導体基板を用いた半導体装置の製造方法であって、フィールド領域表面に、半導体基板表面から半導体基板上に形成する電子ビーム露光用レジストへのインジウムおよびアルミニウムを含む成分の拡散を抑制する被覆層を形成する工程と、フィールド領域表面に被覆層が形成された半導体基板上に電子ビーム露光用レジストを塗布し、メサ領域の一部に電子ビームを露光し、現像することでメサ領域に開口部を有するレジストパターンを形成する工程と、メサ領域に開口部を有するレジストパターンを用いて半導体基板を修飾する工程とを有する製造方法。

(もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

【課題】窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。

【解決手段】パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。

(もっと読む)

81 - 100 / 405

[ Back to top ]