Fターム[5F102GV05]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097)

Fターム[5F102GV05]の下位に属するFターム

多層構造 (291)

SiO2膜 (488)

Si3N4膜 (770)

ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV05]に分類される特許

61 - 80 / 405

パッケージ

【課題】電流容量が高く、かつ生じる応力が低減されてクラックの発生が抑制され、信頼性の高いパッケージを提供する。

【解決手段】パッケージ外壁16と、パッケージ外壁16を貫通する貫通孔と、貫通孔にはめ込まれた凸状フィードスルー25と、凸状フィードスルー25に固定され端子電極21bとを備え、端子電極21bは、相対的に線熱膨張率は低いが抵抗率が高い第1の金属層90と、相対的に線熱膨張率は高いが抵抗率が低い第2の金属層80a,80bとを備える。

(もっと読む)

パッケージ

【課題】ベース面の反りの少ないパッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートとは異なる材料からなる金属壁16とを備え、導体ベースプレートは、対抗する1対の端面100a・100bが緩やかな弧を有し、金属壁も緩やかな弧を有しているので、接合時や基板実装時、キャップ半田付け時の反りの発生を抑制できる。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース18、ドレイン20、およびゲート22を含む。第1のスペーサ層26が、活性領域の上方でソースとゲートの間にあり、第2のスペーサ層28が、活性領域の上方でドレインとゲートの間にある。第1のスペーサ層上の第1のフィールドプレート30、及び第2のスペーサ層上の第2のフィールドプレート32が、ゲートに接続される。第3のスペーサ層34が、第1のスペーサ層、第2のスペーサ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、第3のフィールドプレート36が、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ

【課題】電子トラッピングによる、DC特性とRF特性の差を低減する。

【解決手段】トランジスタ10は、チャネル層を有する活性領域を含み、この活性領域と接触してソースおよびドレイン電極20,22が形成され、このソース電極とドレイン電極との間にあって活性領域と接触したゲート24が形成される。ゲートとドレイン電極との間およびゲートとソース電極との間の複数の活性領域の表面の少なくとも一部分上にスペーサ層28がある。このスペーサ層上にはフィールドプレート32があり、活性領域の上のスペーサ上をドレイン電極に向かって延びる。このフィールドプレートはさらに、活性領域の上のスペーサ層上をソース電極に向かって延びる。少なくとも1つの導電性経路34,36が、フィールドプレートをソース電極またはゲートに電気的に接続する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留りが高く信頼性の高いパッケージングされた半導体装置を提供する。

【解決手段】電極が形成された半導体チップと、前記電極に対応するリードと、前記電極と前記リードとを接続する金属配線と、前記金属配線と前記電極との接続部分及び前記金属配線と前記リードとの接続部分を覆う第1の樹脂部と、前記金属配線、前記第1の樹脂部及び前記半導体チップを覆う第2の樹脂部と、を有することを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリ・オフ動作に適したMIS型を採用するも、電流コラプス特性を大幅に向上させて、デバイス効率及び耐圧に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成されたゲート絶縁膜6と、ゲート電極7とを含み、ゲート電極7は、ゲート絶縁膜6上に形成されたゲート基部7aと、ゲート基部7a上に形成されたゲート傘部7bとを有しており、ゲート傘部7bの下面が化合物半導体積層構造2とショットキー接触する。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、トランジスタの特性を低下させることなく高い密度のドレイン電流が実現できるようにする。

【解決手段】主表面を(0001)面とした第1窒化物半導体からなるチャネル層101と、チャネル層101の上に形成された第1窒化物半導体より大きなバンドギャップエネルギーの窒化物半導体からなる第1障壁層102と、ゲート電極104が形成されたゲート形成領域121を挟んだソース形成領域122およびドレイン形成領域123の第1障壁層102の上に形成され、第2窒化物半導体より大きなバンドギャップエネルギーの第3窒化物半導体からなる第2障壁層105および第3障壁層106と、第2障壁層105および第3障壁層106の上に形成された第2窒化物半導体からなる第4障壁層107および第5障壁層108とを備える。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】耐湿性及び耐電圧性を確保しながら、デバイス特性が劣化しないようにする。

【解決手段】半導体装置を、キャリア走行層及びキャリア供給層を含む窒化物半導体積層構造を備える半導体チップ1と、半導体チップの表面を覆い、カップリング剤を含有する第1樹脂層5と、第1樹脂層の表面を覆い、界面活性剤を含有する第2樹脂層6と、第1樹脂層及び第2樹脂層で覆われた半導体チップを封止する封止樹脂層7とを備えるものとする。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】特性の安定化を達成できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第3半導体層5、第4半導体層6、第1電極10、第2電極8及び第3電極9を備える。第1半導体層3、第2半導体層4、第3半導体層5及び第4半導体層6は、窒化物半導体を含む。第2半導体層4は、第1半導体層3の禁制帯幅以上の禁制帯幅を有する。第3半導体層5は、GaNである。第4半導体層6は、第3半導体層5の上において一部に隙間を有して設けられ、第2半導体層4の禁制帯幅以上の禁制帯幅を有する。第1電極10は、第3半導体層5の上において第4半導体層6が設けられていない部分に設けられる。第2電極8及び第3電極9は、第4半導体層6の上において、第1電極10の一方側及び他方側にそれぞれ設けられ、第4半導体層6とオーミック接合している。

(もっと読む)

半導体装置の製造方法、および半導体装置

【課題】GaNを有する窒化物の上にマイクロ波プラズマを用いてゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】GaN層13,AlGaN層14aが積層されたFET構造と、フィールド酸化膜15とゲート電極20との間にかけて、形成されたゲート絶縁膜19bを備える。ゲート絶縁膜19bは、アルミナ24aとシリコン酸化膜24bから構成される二層構造とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部をp+型領域20にて埋め尽くすようにする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

多重フィールドプレートトランジスタ

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

半導体装置

【課題】導体ベースプレート上に実装するSiCやダイヤモンドを基板とする高周波半導体チップの割れを防止する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された高周波半導体チップとを備え、高周波半導体チップは、四隅が面取りされている半導体装置。

(もっと読む)

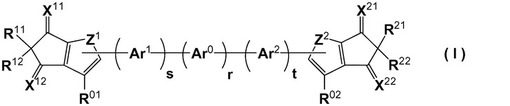

共役系化合物、並びにこれを用いた有機薄膜及び有機薄膜素子

【課題】電子輸送性に優れたn型半導体として利用可能であり、しかも溶剤への溶解性にも優れる共役系化合物の提供。

【解決手段】式(I)で表される共役系化合物。[式中、R01及びR02はアルカン骨格を含む1価の基。R11、R12、R21及びR22は水素原子、ハロゲン原子又は1価の基。X11、X12、X21及びX22は=O,=S又は=CA2(Aは水素原子、ハロゲン原子又は1価の基を示すが、その少なくとも1つは電子吸引性の基。)を示す。Z1及びZ2は−O−,−S−,−Se−,−Te−,−SO−等のいずれかの基を示す。Ar0、Ar1及びAr2は芳香族炭化水素基又は複素環基を示す。rは1〜6の整数、s及びtは0〜6の整数を示す。] (もっと読む)

(もっと読む)

61 - 80 / 405

[ Back to top ]