Fターム[5F102GV05]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097)

Fターム[5F102GV05]の下位に属するFターム

多層構造 (291)

SiO2膜 (488)

Si3N4膜 (770)

ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV05]に分類される特許

21 - 40 / 405

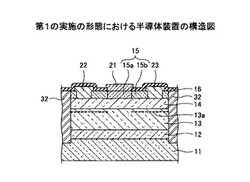

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

不純物濃度を選択的に減少させたIII−V族デバイス構造

【課題】HEMT及びその他の高速スイッチングデバイスにおいて、意図しない不純物のドープはを防ぎ高性能なデバイスを提供する。

【解決手段】半導体構造は、基板、基板上方の遷移体、及び遷移体上方に底面を有するIII−V族中間体を備える。半導体構造はさらに、III−V族中間体の頂面上方にIII−V族デバイス層を備える。III−V族中間体213は、前記底面211において高く、前記頂面213において低くなる形で連続的に減少された不純物濃度を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、デバイス特性の劣化(化学的・物理的変化)を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】本発明による化合物半導体装置では、化合物半導体層2上を均質な同一材料(ここではSiN)からなり誘電率が一様な第1の保護膜6が覆い、第1の保護膜6の開口6aの一端部分に酸素を含有する保護部、ここでは当該一端部分を覆う酸化膜である第2の保護膜7aが形成されており、開口6aを埋め込み第2の保護膜7aを包含するオーバーハング形状のゲート電極8が形成される。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】GaとSiとの反応を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、Si基板1と、Si基板1の表面に形成されたSi酸化層3と、Si酸化層3上に形成され、Si酸化層3の一部を露出する核形成層2と、Si酸化層3及び核形成層2上に形成された化合物半導体積層構造9と、が設けられている。

(もっと読む)

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

【課題】貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタを作製する。

【解決手段】ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極に臨む領域の半導体層へのダメージ層の形成を抑制して、ノーマリオフ動作を実現することができるヘテロ接合電界効果型トランジスタを備える半導体装置およびその製造方法を提供する。

【解決手段】チャネル層23とヘテロ接合を形成するバリア層24のうち、ゲート電極29に臨む領域を除く他の領域に、バリア層24の伝導帯から、チャネル層23とバリア層24とのヘテロ界面のバンド不連続量ΔEcと、バリア層24に発生する分極によるバリア層24のゲート電極29側とヘテロ界面側とのエネルギー差ΔEpとを足し合わせたエネルギー(ΔEc+ΔEp)までのエネルギー深さのバンドギャップ中に準位を形成する不純物をドーピングして、不純物ドーピング領域26を形成する。

(もっと読む)

半導体装置

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

ワイドバンドギャップ半導体デバイス

【課題】製造が容易であり、デバイス特性の変動を抑制できるワイドバンドギャップ半導体デバイスを得る。

【解決手段】SiC基板1上にAlN格子緩和層2、GaNチャネル層3、及びAlGaN電子供給層4が順に設けられている。これらは、1.42eVより広いバンドギャップを持つ半導体材料からなる。AlGaN電子供給層4に、トランジスタを含む活性領域9が設けられている。SiC基板1は、光学的な不純物又は格子欠陥により着色され、可視光領域の光を吸収する。従って、このデバイスは波長360nm〜830nmの可視光領域の光に対して不透明である。

(もっと読む)

集積されたダイオードを備える複合半導体装置

【課題】高電圧が印加されても、故障しにくい複合半導体装置を提供する。

【解決手段】複合半導体装置200はダイオード210の上に形成された遷移体220を含み、この遷移体220は2以上の半導体層を含む。複合半導体装置200は遷移体220の上に形成されたトランジスタ230も含む。ダイオード210は半導体貫通ビア、外部電気接続部又はその両方の組み合わせを用いてトランジスタ230の両端間に接続される。

(もっと読む)

電界効果トランジスタ

【課題】チャネルへの電子供給能力が改善されたIII−V族FETを提供する。

【解決手段】基板2の上には、ナローバンドギャップ材料のチャネル層4が形成される。チャネル層4の上のソース領域には、ワイドバンドギャップ材料のコンタクト層6が形成される。ソースコンタクト層6は、1×1019cm−3以上の濃度でドーピングされる。FET1は、ソースコンタクト層6によってアンドープのチャネル層4に直接キャリアが注入されるように構成される。

(もっと読む)

窒化物半導体装置

【課題】リードフレーム上に搭載された窒化物FETを備えスイッチング特性に優れた窒化物半導体装置を提供する。

【解決手段】窒化物FETと、複数のリードを含むリードフレームと、を備え、前記窒化物FETは少なくとも第1の主電極と第2の主電極と制御電極とを有し、前記リードフレームは、前記第1の主電極に接続される第1のリードと、前記第2の主電極に接続される第2のリード及び第3のリードと、前記制御電極に接続される第4のリードと、を有し、前記窒化物FETは、前記第3のリードと前記第4のリードとの間に印加される電圧に応じて前記第1のリードと前記第2のリードとの間に電流を流すことを特徴とする窒化物半導体装置。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

駆動回路および半導体集積回路

【課題】 高電子移動度トランジスタを用いて駆動回路を形成し、信頼性を低下させることなく、スイッチングトランジスタを高速に駆動する。

【解決手段】 駆動回路は、ドレインが第2ハイレベル電圧線に接続され、ソースが第1スイッチングトランジスタのゲートに接続される第1高電子移動度トランジスタと、ドレインが第1スイッチングトランジスタのゲートに接続される第2高電子移動度トランジスタと、ドレインが第2高電子移動度トランジスタのソースに接続され、ソースが接続ノードに接続される第1フィールドプレートと、第1および第2高電子移動度トランジスタを排他的にオンするために、第1および第2高電子移動度トランジスタのゲート電圧を生成し、第2高電子移動度トランジスタをオフするときに、第2高電子移動度トランジスタのゲートをロウレベル電圧線のロウレベル電圧に設定する制御部とを有している。

(もっと読む)

21 - 40 / 405

[ Back to top ]