Fターム[5F102GV05]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097)

Fターム[5F102GV05]の下位に属するFターム

多層構造 (291)

SiO2膜 (488)

Si3N4膜 (770)

ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV05]に分類される特許

41 - 60 / 405

パワー素子およびその製造方法

【課題】本発明は、ノーマリーオフ動作が可能なパワー素子およびその製造方法を提供する。

【解決手段】本発明のパワー素子は、第1窒化物層を形成した後ゲート電極下部に第2窒化物層をさらに形成することによってゲート電極に対応する部分には2次元の電子ガス層が形成されないため、ノーマリーオフ動作が可能である。これによって、本発明の一実施形態に係るパワー素子は、ゲートの電圧に応じて2次元の電子ガス層の生成を調整することができ、ノーマリーオフ動作が可能であるため、消費電力を減少させ得る。また、ゲート電極に対応する第2窒化物層を形成するため、第1窒化物層を形成した後ゲート電極に対応する部分のみを再成長させたり、ゲート電極に対応する部分を除いた残り部分をエッチングする方法を用いることによって、リセス工程を省略することができることから素子の再現性を確保することが化膿であり、工程を単純化させることができる。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

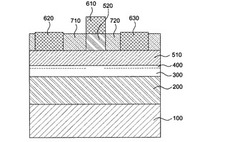

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置の製造方法

【課題】設計の自由度を損なわずに、高いオン特性とオフ特性を持つ半導体装置を容易に製造する。

【解決手段】可視光に対して透明な半導体基板1の表面にソース電極2及びドレイン電極3を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間に表側ゲート電極4を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間以外の領域に合わせマーク5を形成する。半導体基板1を透過して見える合わせマーク5に基づいて半導体基板1を位置合わせして、半導体基板1の裏面において表側ゲート電極4と対向する位置に裏側ゲート電極6を形成する。

(もっと読む)

スイッチング素子

【課題】 コラプス現象を効果的に抑制することを可能にしたスイッチング素子を提供する。

【解決手段】 スイッチング素子1aは、電子走行層12と、電子走行層12の上面に形成されてバンドギャップが電子走行層12より大きく電子走行層12とヘテロ接合する電子供給層13と、電子供給層13の上面に形成されてバンドギャップが電子供給層13より小さい再結合層17と、少なくとも一部が電子走行層12の上面に形成されるソース電極14及びドレイン電極15と、少なくとも一部が電子供給層13の上面に形成されて前ソース電極14及びドレイン電極15の間に配置されるゲート電極16と、を備える。スイッチング素子1aがオフ状態のとき、再結合層17で電子及び正孔が再結合する。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイス、及び伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを提供する。

【解決手段】予め歪みが加えられた拡張状態の弾性基板が与えられる。印刷可能な半導体構造の内面の少なくとも一部を、予め歪みが加えられた拡張状態の弾性基板の外面に対して結合される。半導体構造の内面を湾曲させることにより弾性基板を少なくとも部分的に緩和状態へと弛緩させる。湾曲した内面を有する半導体構造が弾性基板から他の基板、好ましくはフレキシブル基板へと転写される。

(もっと読む)

トランジスタ

【課題】耐圧特性に優れた高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】基板12上に形成された複数の活性半導体層16、18を含むHEMT10。ソース電極20、ドレイン電極22、およびゲート24は、複数の活性層16、18と電気的に接触して形成される。スペーサ層26は、複数の活性層16、18の表面の少なくとも一部の上に形成され、ゲート24を覆っている。フィールドプレート30が、スペーサ層26上に形成されて、ソース電極22に電気的に接続され、このフィールドプレート30はHEMT10内の最高動作電界を低減する。

(もっと読む)

半導体装置

【課題】電流コラプスを低減し、ドレイン電流を増大しながら、ゲートリーク電流を減少できるようにする。

【解決手段】半導体装置は、基板1と、基板1の上に形成されたIII族窒化物からなる半導体層2、3と、半導体層2、3の上に、それぞれ形成されたソース電極5、ゲート電極7及びドレイン電極6と、半導体層2、3の上に、ゲート電極7の下部及び半導体層2、3と接し、且つ、ソース電極5及びドレイン電極6と離間するように形成されたシリコンを含まない第1保護膜8と、半導体層2、3の上に、半導体層2、3と接し且つゲート電極7の下部と離間するように形成され、第1保護膜8と組成が異なり且つ窒素を含む第2保護膜9とを備えている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

低電圧デバイス保護付き高電圧複合半導体デバイス

【課題】低電圧デバイス保護付き高電圧複合半導体デバイスを提供する。

【解決手段】電圧保護されたデバイスを含複合半導体デバイスの1つの好適な実現では、ノーマリオフ複合半導体デバイス300が、第1出力キャパシタンス318を有するノーマリオンIII-窒化物パワートランジスタ310と、このノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイス320を具えて、このノーマリオフ複合半導体デバイスを形成し、このLVデバイスは第2出力キャパシタンス348を有する。第1出力キャパシタンス対第2出力キャパシタンスの比率を、ノーマリオンIII-窒化物パワートランジスタのドレイン電圧対LVデバイスの降伏電圧の比率に基づいて設定して、LVデバイスの電圧保護を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】電子移動度の低下が抑制され、かつ二次元電子ガスの閉じ込めが高められた半導体装置およびその製造方法を提供する。

【解決手段】AlaInbGa1-(a+b)N(0≦a,b≦1、0≦a+b≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが大きい第1の窒化物半導体層2、AlcIndGa1-(c+d)N(0≦c,d≦1、0≦c+d≦1)から成る第2の窒化物半導体層3、IneGa1-eN(0<e≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが小さいバックバリア層4、AlfIngGa1-(f+g)N(0≦f,g≦1、0≦f+g≦1)から成り、第2の窒化物半導体層3とバンドギャップが等しいチャネル層5、AlhIniGa1-(h+i)N(0≦h,i≦1、0≦h+i≦1)から成り、チャネル層5よりもバンドギャップが大きいバリア層6を、この順に基板1に積層する。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

重合体、この重合体を用いた有機薄膜及び有機薄膜素子

【課題】優れたホール輸送性を有する重合体を提供すること。

【解決手段】式(1)で表される構造単位及び式(2)で表される構造単位を有する重合体。 (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】オン抵抗が小さく、またオフ容量が低い、デュアルゲートを備えた電界効果トランジスタを提供する。

【解決手段】第1又は第2のゲート電極8は、ソース電極4側又は前記ドレイン電極5側に延びる第1のひさし部61と、第2又は第1のゲート電極8側に延びる第2のひさし部62とを有し、第2のひさし部62の長さが第1のひさし部61の長さより短い。

(もっと読む)

パッケージ

【課題】電流容量が高く、かつ生じる応力が低減されてクラックの発生が抑制され、信頼性の高いパッケージを提供する。

【解決手段】パッケージ外壁16と、パッケージ外壁16を貫通する貫通孔と、貫通孔にはめ込まれた凸状フィードスルー25と、凸状フィードスルー25に固定され端子電極21bとを備え、端子電極21bは、相対的に線熱膨張率は低いが抵抗率が高い第1の金属層90と、相対的に線熱膨張率は高いが抵抗率が低い第2の金属層80a,80bとを備える。

(もっと読む)

41 - 60 / 405

[ Back to top ]