Fターム[5F102HC17]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | エッチング (1,013) | オーバーエッチング、サイドエッチングの利用 (46)

Fターム[5F102HC17]に分類される特許

1 - 20 / 46

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

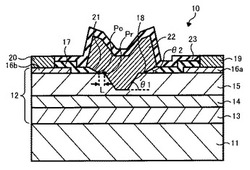

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、デバイス特性の劣化(化学的・物理的変化)を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】本発明による化合物半導体装置では、化合物半導体層2上を均質な同一材料(ここではSiN)からなり誘電率が一様な第1の保護膜6が覆い、第1の保護膜6の開口6aの一端部分に酸素を含有する保護部、ここでは当該一端部分を覆う酸化膜である第2の保護膜7aが形成されており、開口6aを埋め込み第2の保護膜7aを包含するオーバーハング形状のゲート電極8が形成される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】斜めイオン注入を行わなくても、外周耐圧構造を形成でき、かつ、高いドレイン耐圧が得られるようにする。

【解決手段】凹部16の底面に形成されたP型領域18と、トレンチ13内に配置されたP+型層15、および、凹部17の底面に形成されたP型領域19とによってP型リサーフ層20を構成することで電界緩和構造とする。P型リサーフ層20がトランジスタセル領域R1の周囲を囲むような構成とされることから、外周耐圧構造領域R2に延びる電界をさらにトランジスタセル領域R1の外周側に延ばすことが可能となり、ブレークダウン位置を凹部17の底面におけるN-型ドリフト層2にシフトできるため、電界緩和を行うことが可能となる。したがって、ドレイン耐圧を向上させることが可能となる。

(もっと読む)

半導体装置とその製造方法

【課題】 半導体装置を高耐圧化する技術を提供することを目的とする。

【解決手段】 半導体装置100は、p型の埋込み層26と、p型埋込み層26上に設けられており、ヘテロ接合面3が構成されている窒化物半導体のヘテロ接合層32を備えている。p型埋込み層26は、ソース電極10側からドレイン電極2側に向けて厚みが減少する厚み減少部24を有している。厚み減少部24では、ソース電極10側の減少開始点14からドレイン電極2側の減少終了点16までの長さ24bが、減少開始点14における厚み24aよりも長い。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】本発明は、電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果型トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明のヘテロ接合電界効果型トランジスタは、バリア層4及びバリア層4上に形成されたキャップ層5を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして窒化物半導体層上に設けられたゲート電極10と、ゲート電極10の両側に離間して夫々設けられたドレイン電極8及びソース電極9とを備える。ゲート電極10のドレイン電極8側端面とソース電極9側端面のうち少なくともドレイン電極8側端面は、キャップ層5と少なくとも部分的に乖離しており、当該乖離部分が空隙である。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、SBD、HEMT等のデバイスに逆方向電圧をかけたときの電極端部に生じる電界集中を緩和して電流コラプス、及び長期信頼性の問題を解決した半導体装置を提供する。

【解決手段】窒化物化合物半導体層を有する電子走行層11と、前記電子走行層11に形成された窒化物化合物半導体からなる電子供給層12と、前記電子供給層12上に形成された第1電極13と、前記電子供給層12上に前記第1電極13と離間して形成された第2電極14と、前記電子走行層11および前記電子供給層12を挟んで前記第1電極13に対向して形成された、前記第1電極13と同電位の第1導電体14と、前記電子走行層11および前記電子供給層12を挟んで前記第2電極14に対向して形成された、前記第2電極14と同電位の第2導電体16とを有する半導体装置1を提供する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート−ソース間の容量低減及びソース抵抗を低減させ、且つ耐圧向上、高出力化及び高周波化を、容易且つ確実に可能とする量産化に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極19を形成する際に、4層の電子線レジスト11〜14を用いてゲート開口17を形成し、ゲート開口17内に、キャップ層5の表面との接触面を含む幹状の下方部分19aと下方部分19aから傘状に拡がる上方部分19bとが一体形成されてなり、下方部分19aの接触面がドレイン電極7に比べてソース電極6に偏倚した位置に設けられており、上方部分19bの傘状の下端面のうちソース電極6側の部位がドレイン電極7側の部位よりもキャップ層5の表面からの高さが高いゲート電極19を形成する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置とその製造方法

【課題】メサ上に形成されるレジストを高精度にパターニングされ、メサ上に断線し難いゲート電極を有する半導体装置およびその製造方法を提供すること。

【解決手段】オーミック電極10を形成する前にゲート電極12を形成することで、オーミック電極10間の狭い領域にレジストパターンの開口部を設ける必要がなくなり、レジスト溜まりが生じにくい構造となっている。また、ゲート電極12をメサの平坦な領域にのみ形成し、その分チャネル層3のサイドエッチング量を大きくしてチャネル層幅がゲート電極幅よりも小さくされている。ゲート電極12を平坦な領域のみに形成することで、ゲート電極12の厚膜化とゲート電極形成用のレジスト塗布後膜厚の均一化を両立可能にしている。ゲート電極の断線が極めて少なく、ゲート電極形成工程におけるレジストパターニング精度が改善された、ウェハ面内の特性ばらつきの少ない半導体装置を実現している。

(もっと読む)

半導体装置およびその製造方法

【課題】SiCを素材として採用することで本来得られる特性をより確実に得ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】JFET1は、少なくとも上部表面14Aが炭化珪素からなるウェハ10と、上部表面14A上に形成されたゲートコンタクト電極21とを備える。ウェハ10は、上部表面14Aを含むように形成されたイオン注入領域である第1のp型領域16を含む。第1のp型領域16は、上部表面14Aを含むように配置されるベース領域16Aと、突出領域16Bとを含む。ベース領域16Aは、上部表面14Aに沿った方向における幅w1が、突出領域16Bの幅w2よりも広い。ゲートコンタクト電極21は、平面的に見てその全体が第1のp型領域16に重なるように、第1のp型領域16に接触して配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】リセス構造中に形成された電極を具備する半導体装置において、オン抵抗を低く、かつ信頼性を高くする。

【解決手段】図1(b)に示されるように、全面に第1の絶縁層103を形成する。次に、図1(c)に示されるように、フォトリソグラフィを行い、フォトレジストパターン104を形成する。次に、図1(d)に示されるように、第1の絶縁層103のドライエッチングを行う。次に、図1(e)に示されるように、半導体積層構造をエッチングする。次に、図1(f)に示されるように、この状態で第1の絶縁層103のウェットエッチングを行う。次に、図1(g)に示されるように、この状態で電極材料105を全面に形成する。次に、図1(h)に示されるように、フォトレジストパターン104を除去する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】安価な基板を用いて製造することができ、良好な特性を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】p型GaN層2と、p型GaN層2上に形成され、空乏化されたn型GaN層3と、n型GaN層3上に形成された厚さが30μm以上のアンドープのGaN層4と、が設けられている。更に、GaN層4上に形成された活性層5と、活性層5上に形成された電極層6と、が設けられている。これらの積層体は、サファイア基板を用いて形成されたものであり、積層体の形成後にサファイア基板が分離されている。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、RFデバイスの低抵抗化による高効率化を図り、高い生産性を得ることが可能な化合物半導体装置とその製造方法を提供する。

【解決手段】GaN層11上にAlGaN層12が形成されたAlGaN/GaN基板と、それぞれGaN層11とAlGaN層12の界面に形成される二次元キャリア層13を貫通してGaN層に到達し、その側面とAlGaN/GaN基板の基板面との角度が90±10°となる開口部に形成されるメタル層からなるソース電極14およびドレイン電極15とを備える。

(もっと読む)

電界効果トランジスタ、その製造方法、及び半導体装置

【課題】電圧ストレス前後でのしきい値電圧変動が少ない高信頼性の電界効果トランジスタ、その製造方法、及び半導体装置を提供すること

【解決手段】本発明にかかるJ−FET51は、半絶縁性GaAs基板1上に形成された第1導電型のチャネル層(Siドープn型AlGaAs電子供給層3、7、アンドープAlGaAsスペーサ層4、6、アンドープInGaAsチャネル層5)と、第1導電型のチャネル層上に形成された少なくとも1層以上の半導体層からなる上層半導体層と、上層半導体層に設けられたリセス内、又は上層半導体層の上に形成された第2導電型の半導体層(Cドープp+−GaAs層18)と、第2導電型の半導体層上に接触して設けられたゲート電極19と、上層半導体層の上に接触して設けられた窒化膜16と、窒化膜16上に形成され、窒化膜16よりも膜厚の厚い酸化膜17とを含むゲート絶縁膜と、を備えるものである。

(もっと読む)

半導体装置

【課題】窒化物系半導体機能層に生成される二次元キャリアガスチャネルにおいてキャリア密度及び電界をキャリア走行方向に変調する半導体装置を提供する。

【解決手段】半導体装置(HEMT)1において、第1の窒化物系半導体領域21上に第2の窒化物系半導体領域22を有する窒化物系半導体機能層2と、窒化物系半導体機能層2上に互いに離間されて配設された第1の主電極3及び第2の主電極4と、窒化物系半導体機能層2上の第1の主電極3と第2の主電極4との間に配設されたゲート電極5とを備え、第2の窒化物系半導体領域22の第1の主電極3側の膜厚に対して第2の主電極4側の膜厚が異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】高周波応答特性を低下させずにリーク電流を低減させることができ、しかもゲート長の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】電子供給層4にAlGaAs層4AとInGaP層4Bの積層構造を用い、半導体表面に形成する絶縁膜6にSiN膜6AとSiO2膜6Bの積層構造を用いる。絶縁膜6に電子供給層4を露出させる開口60を形成する際に、半導体と接触しているSiN膜6Aがサイドエッチングされることで、開口60の電子供給層4側の内周面61とゲート電極7との接触が回避され、しかもゲート電極7の周囲にInGaP層4Bのみを露出させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の周囲に形成される空洞と保護膜に形成されるホールとの境界部分の開口を封止しやすい構造を実現する。

【解決手段】半導体装置を、ゲート電極3と、高さが低い部分6Aと高さが高い部分6Bとを有する階段状の空間6をゲート電極3の周囲に有する保護膜4と、高さが低い部分6Aに接するように保護膜4に形成されたホール5とを備えるものとする。

(もっと読む)

1 - 20 / 46

[ Back to top ]