Fターム[5F103HH05]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 基板 (664) | 金属基板 (23)

Fターム[5F103HH05]に分類される特許

1 - 20 / 23

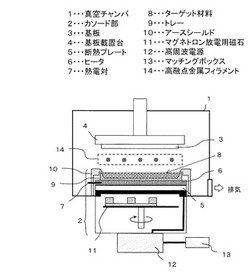

スパッタリング方法およびスパッタリング装置

【課題】粉末ターゲットを用いて、酸素の含有率の少ない高品質なシリコン薄膜を高速で成膜することができるスパッタリング方法及び装置を提供することを目的とする。

【解決手段】スパッタ成膜を行う前段階に、ターゲット材料8近傍に設置した高融点金属フィラメント14を加熱することで、真空チャンバ1内に導入したガスを分解し活性種を生成する。この活性種を用いて、ターゲット材料8表面の酸化膜の還元や真空チャンバ壁及び部材についた堆積膜の除去を行うことで、スパッタ成膜中の酸素量を低減させ、高品質なシリコン薄膜を形成する。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法、および表示装置

【課題】酸化物半導体を用いた、高信頼性で且つ低コストで製造できる薄膜トランジスタアレイ基板、その製造方法、表示装置を提供する。

【解決手段】

薄膜トランジスタアレイ基板は、基板と、前記基板上に形成された第1の水素拡散防止膜と、前記第1の水素拡散防止膜上に形成された、酸化物半導体層を有する複数の薄膜トランジスタと、を備え、前記第1の酸化物拡散防止膜が前記薄膜トランジスタの前記酸化物半導体層とほぼ同一の組成からなる。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

電界効果トランジスタ及び電界効果トランジスタの製造方法

【課題】MgとInとを主成分とする複合酸化物を活性層とし、かつ良好な電界効果移動度を示す電界効果トランジスタを提供すること。

【解決手段】ゲート電極3、ソース電極4及びドレイン電極5と、ドレイン電極5及びソース電極4が接合された活性層2と、活性層2及びゲート電極3の間にゲート絶縁膜6と、備え、活性層2がMgとInとを主成分とする複合酸化物であり、ゲート絶縁膜6がY2O3である電界効果トランジスタ1を使用する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】信頼性および再現性が優れるとともに、歩留まりが高く生産性が優れた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】薄膜トランジスタの製造方法は、基板上にゲート電極を形成する工程と、ゲート電極を覆って基板上に第1の絶縁膜を形成し、第1の絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第2の絶縁膜を形成して、第1の絶縁膜、酸化物半導体膜および第2の絶縁膜からなる積層体を得る工程と、積層体の第1の絶縁膜、酸化物半導体膜および第2の絶縁膜をパターニングして、それぞれゲート絶縁層、活性層およびチャネル保護層を形成する工程と、ソース電極およびドレイン電極を形成する工程とを有する。第1の絶縁膜、酸化物半導体膜および第2の絶縁膜は、大気に曝されることなく連続して形成される。

(もっと読む)

IGZO系アモルファス酸化物半導体膜の製造方法及びそれを用いた電界効果型トランジスタの製造方法

【課題】スパッタ法により、TFTの活性層として好適なキャリア密度を有し、且つ、電気的ストレス、及び熱に対して安定性の良好なIGZO系アモルファス酸化物半導体膜を製造する。

【解決手段】IGZO系アモルファス酸化物層を下記式(1)を満足する条件でスパッタ成膜した後に、下記式(2)を満足する条件でアニール処理することにより、IGZO系アモルファス酸化物からなる半導体膜を製造する。

1×10−5≦P(Pa)≦5×10−4 ・・・(1)、

100≦T(℃)≦300 ・・・(2)

(式中、Pは前記スパッタ成膜における背圧,Tは前記アニール処理におけるアニール温度)

(もっと読む)

IGZO系アモルファス酸化物薄膜の製造方法及びそれを用いた電界効果型トランジスタの製造方法

【課題】導電体領域から絶縁体領域までの範囲内で所望の電気抵抗値有し、且つ、電気的ストレスに対して安定性の良好なIGZO系アモルファス酸化物薄膜を製造する

【解決手段】IGZO系アモルファス酸化物薄膜を基板上にスパッタ成膜し、その後アニール処理してIGZO系アモルファス酸化物薄膜を製造する方法であって、成膜装置内の水分量とアニール処理の温度の組み合わせを変化させて、導電体領域から絶縁体領域の範囲内の任意の電気抵抗値を有するアモルファス酸化物薄膜を製造する。

(もっと読む)

ゲートバルブ、それを具備したフィルム製造装置、及び、それを用いたフィルム製造方法

【課題】外部リークをより少なくして真空状態を維持することができ、ロール交換時に巻き出し室や巻取り室を素早く大気圧状態に戻し、ロール交換後も素早く真空状態に戻すことができるフィルム製造装置を提供する。

【解決手段】フィルム製造装置1は、巻き出し手段6、巻き取り手段7、3つの反応室4A、4B、4C、フィルム搬送路5より構成され、フィルムが通過する少なくとも一の開口部を有する反応室内に配置され、かつ、開口部には、該フィルムを挟みながら封止することにより真空室を密封可能とする弁体を有するバルブ機構11〜16が具備されている。

(もっと読む)

基板上に単結晶層を作製する方法

【課題】基板上に単結晶材料の層を成長させる方法を提供する。

【解決手段】第1単結晶材料から形成された露出領域を有する基板を、プロセスチャンバ中に配置する工程と、拡散制限ガスの存在下で、基板に向かって、第2材料の中性種のビームを供給し、プロセスチャンバ中の圧力を1×10−6torrから1×10−4torrの間にし、第2材料の中性種を露出領域上に吸着され、これにより第1単結晶材料の上にこれと接触して第2材料の単結晶層を成長させる工程とを含み、拡散制限ガスは、非反応性ガスからなる。

(もっと読む)

多結晶シリコン膜の形成方法、多結晶シリコン膜の形成装置及び多結晶シリコン膜が形成された基板

【課題】良好な特性の多結晶シリコン膜を短時間に形成できる多結晶シリコン膜の形成方法、形成装置及びそれにより形成された多結晶シリコン膜が形成された基板を提供する。

【解決手段】シリコン蒸発源15の加熱によりシリコン微粒子を生成し、次に、シリコン微粒子を移送し、超音速フリージェットJの気流に乗せて真空チャンバー30中に噴出して、真空チャンバー30中に配置された基板33上に物理蒸着させ、シリコン微粒子からなる多結晶シリコン膜を形成する。

(もっと読む)

高品質化合物半導体材料を製造するためのナノ構造適応層及びHVPEを使用する成長法

【課題】品質に優れ、平坦で厚い化合物半導体を成長させるための方法を提供する。

【解決手段】HVPEを利用し、ナノ構造層を使用して高品質の平坦かつ厚い化合物半導体(15)を異種基板(10)上に成長させる。半導体材料のナノ構造(12)は、分子線エピタキシャル成長(MBE)、化学気相成長(CVD)、有機金属化学気相成長(MOCVD)又はハイドライド気相エピタキシャル成長(HVPE)によって基板(10)上に成長させることができる。化合物半導体の厚膜(15)又はウェハは、HVPEを使用したエピタキシャル横方向成長によってナノ構造(12)上に成長させることができる。

(もっと読む)

エピタキシャル薄膜の形成方法、半導体基板の製造方法、半導体素子、発光素子及び電子素子

【課題】装置コストが低く、形成される薄膜の結晶性が高くなるようなエピタキシャル薄膜の形成方法、半導体基板の製造方法、半導体素子、発光素子及び電子素子を提供すること。

【解決手段】ターゲットをパルス電圧によって間欠的にスパッタし、基板上に金属原子を間欠的に供給することにより、安定した格子位置の金属窒化物を基板上に成長させることができる。これにより、結晶性の極めて良好な半導体薄膜を形成することができる。加えて、本実施形態の一連の製造工程はスパッタ装置によって行うことが可能であるため、装置コストを低く抑えることができる。

(もっと読む)

窒素ガスを用いた亜鉛ターゲットの反応性スパッタにより形成される薄膜半導体材料

本発明は概して、半導体膜及びこの半導体膜の堆積に使用する反応性スパッタ法を含む。スパッタリングターゲットは純粋な亜鉛(すなわち、99.995原子百分率以上)を含み、アルミニウム(約1原子百分率〜約20原子百分率)又はその他のドープ金属でドープしてもよい。亜鉛ターゲットは、窒素及び酸素をチャンバに導入することにより反応的にスパッタされる。窒素の量は、酸素及びアルゴンガスの量よりはるかに多い。酸素の量は、窒素含有ガスを使用しない堆積で得られた測定値に基づく膜構造の転換点、膜透過率、DC電圧変化又は膜導電性を踏まえたものである。反応性スパッタは、室温前後から数百度にのぼる温度で行われる。堆積後、半導体膜をアニールすることにより、膜の移動度を更に改善してもよい。  (もっと読む)

(もっと読む)

半導体グレードシリコンのプラズマ溶射

pn接合を含む半導体構造を形成するために半導体グレードシリコンを溶射するよう構成されたプラズマ溶射ガン(10)は、カソード(16)またはアノード(22)またはプラズマに面する他の部品(28)または少なくとも表面部が高純度シリコンからなりシリコン粉末を運ぶ部品(34)などのシリコン部品を含む。シリコン粉末は、好ましくは10ミクロンよりも小さい。半導体ドーパントは溶射したシリコンに含まれてもよい。 (もっと読む)

発光装置及びその駆動方法

【課題】発光量が制御可能な発光装置及びその駆動方法を提供すること。

【解決手段】n型半導体層1及びこの上に形成されたソース電極4及びドレイン電極5と、p型半導体層2及びこの下に形成されたゲート電極3と、ソース電極4とドレイン電極5との間に交流電圧を印加する交流電源6と、ゲート電極3とソース電極4との間に直流電圧を印加する直流電源7とを有し、交流電圧によって、n型半導体層1に電子が所定量注入され、直流電圧によって、p型半導体層からn型半導体層に正孔を注入して、電子と正孔とを再結合させる。交流電圧は直流電圧によってバイアスされて印加される。基板上に下地絶縁層が形成され、この下地絶縁層上にゲート電極3、p型半導体層2、n型半導体層1がこの順に形成される。n型半導体層1がn型酸化亜鉛により、p型半導体層2がp型酸化亜鉛により形成され、下地絶縁層が酸化亜鉛により形成される。

(もっと読む)

半導体薄膜の製造方法、半導体薄膜の製造装置、光電変換素子の製造方法及び光電変換素子

【課題】 Ib族元素とIIIb族元素とSeを含むVIb族元素とからなるカルコパイライト構造の半導体薄膜半導体薄膜の製造及び光電変換素子の製造に際し、CIGS系薄膜等の半導体薄膜の製膜過程におけるセレン原料の浪費を防止することを課題とする。

【解決手段】 Ib族元素とIIIb族元素とSeを含むVIb族元素とからなるカルコパイライト構造の半導体薄膜の製造方法であって、上記半導体薄膜は製膜過程において、プラズマによってクラッキングされてラジカル化したセレンを用いたことを特徴とする半導体薄膜の製造方法。

(もっと読む)

有機半導体膜の製造方法

【課題】配向性が充分に高い有機半導体膜を簡便に製造できる有機半導体膜の製造方法を提供する。

【解決手段】本発明の有機半導体膜の製造方法は、有機半導体化合物Bを原料として用いた気相成長により、基板13の表面に有機半導体膜を形成させる有機半導体膜の製造方法であって、基板13と有機半導体化合物Bとを、隙間Nが形成されるように隣接させた状態で、圧力10−2〜106Paの雰囲気下で、有機半導体化合物を加熱する。

(もっと読む)

アモルファス酸化物半導体膜を用いた薄膜トランジスタの製造方法

【課題】 プロセスマージンが広く、特性に優れ、且つ信頼性の高い酸化物薄膜トランジスタを作成する。

【解決手段】 アモルファス酸化物半導体膜からなる活性層を備えた薄膜トランジスタの製造方法であって、

前記活性層を形成する工程は、

導入酸素分圧が1×10−3Pa以下の雰囲気中で前記酸化膜を形成する第1の工程と、

前記第1の工程後、酸化雰囲気中で熱処理を行う第2の工程と、

を含む。

(もっと読む)

薄膜トランジスタの製法

【課題】 酸化亜鉛(ZnO)を主成分とする酸化物を半導体薄膜層(活性層)として有する薄膜トランジスタにおいて、製造工程を大幅に低温化するとともに、半導体薄膜層と、該半導体薄膜層上に形成した界面制御型ゲート絶縁膜との界面の清浄化を達成することによって、プラスティック基板上に形成した液晶表示装置や有機エレクトロルミネッセンス素子(OLED)への応用を可能とした高性能薄膜トランジスタの製法の提供。

【解決手段】 酸化亜鉛ZnOを主成分とする酸化物からなる半導体薄膜と、シリコン系絶縁膜からなり該半導体薄膜に接するゲート絶縁膜を有する薄膜トランジスタの製法において、前記半導体薄膜の形成と前記ゲート絶縁膜の形成が真空中にて連続した工程で行われ、前記ゲート絶縁膜が、誘導結合方式プラズマ化学気相成長(ICP−CVD)法又は電子サイクロトロン共鳴化学気相成長(ECR−CVD)法により形成され、全製造工程が200℃以下の温度条件下にて行われることを特徴とする薄膜トランジスタの製法。

(もっと読む)

光起電装置の垂直製造

本発明は光起電薄膜太陽電池(310)を提供し、この電池(310)は垂直に向けたパレット(320)ベースの基材(310)を一続きの反応チャンバー(330、340)へ提供することによって製造され、その反応性チャンバー(330、340)では複数の層が順次このパレット(320)上で形成され得る。 (もっと読む)

1 - 20 / 23

[ Back to top ]