Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

101 - 120 / 732

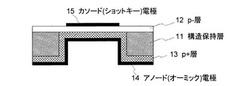

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】ダイヤモンド半導体からなるドリフト層と、半絶縁性ダイヤモンド層を有する構造保持材と、ダイヤモンド半導体からなるコンタクト層とを備えるダイヤモンド電子素子であって、前記構造保持材は、開口部を有し、前記ドリフト層の一方の面に積層されており、前記コンタクト層は、前記開口部内において、前記ドリフト層に直接積層されており、また、アノード電極は、前記開口部内の前記コンタクト層に設け、カソード電極は前記ドリフト層の他方の面に設けて、例えば、ショットキーバリアダイオードを実現する。単結晶ダイヤモンド基板の一方の基板面に欠陥層を形成した後、該基板面上に前記ドリフト層を成膜し、半絶縁性ダイヤモンド層を選択的に成長させて開口部を有する構造保持材を形成した後、前記基板はスマートカット法により素子部より分離する。

(もっと読む)

半導体装置の作製方法

【課題】マスク数が少なく、工程が簡略な半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜と、半導体膜と、不純物半導体膜と、導電膜と、をこの順に積層して形成し、導電膜を加工してソース電極及びドレイン電極を形成し、不純物半導体膜を離間させつつ半導体膜の上部を加工してソース領域及びドレイン領域と、ソース領域及びドレイン領域と重畳しない部分の上部が除去された半導体層と、を形成し、ゲート絶縁膜、半導体層、ソース領域及びドレイン領域、ソース電極及びドレイン電極上にパッシベーション膜を形成し、パッシベーション膜上にエッチングマスクを形成し、エッチングマスクにより、ソース電極またはドレイン電極に達する開口部を形成しつつ、少なくともパッシベーション膜と半導体層を島状に加工し、エッチングマスクを除去し、ゲート絶縁膜及びパッシベーション膜上に画素電極を形成する。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

半導体装置

【課題】本発明は、移動度が向上し、コンタクト抵抗が低減された半導体装置を提供する。

【解決手段】基板11上にゲート電極12、ゲート絶縁膜13、ソース・ドレイン電極14および有機半導体15がこの順に積層された半導体装置において、有機半導体層15は、第1の層15aと第1の層15aよりもグレインサイズの小さい第2の層15bとを備えており、第1の層15aがゲート絶縁膜13側に配置されていることを特徴とする半導体装置である。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

正孔注入輸送層形成用遷移金属含有ナノ粒子及びその製造方法

【課題】製造プロセスが容易でありながら、長寿命を達成可能なデバイスを提供可能な、正孔注入輸送層形成用遷移金属含有ナノ粒子を提供する。

【解決手段】少なくとも遷移金属酸化物を含む遷移金属化合物及び遷移金属と保護剤とを含むか、又は、少なくとも遷移金属酸化物を含む遷移金属化合物と保護剤とを含む遷移金属含有ナノ粒子であって、前記遷移金属含有ナノ粒子は、粒子表面に当該表面を保護する保護剤が付着してなり、当該保護剤が、有機基の末端に前記遷移金属及び遷移金属化合物の少なくとも1つと連結する作用を生じる連結基を1分子中に1つ有する構造であって、当該有機基が特定の構造であり、且つ、当該連結基が特定の官能基である。

(もっと読む)

正孔注入輸送層形成用材料、及びその製造方法

【課題】製造プロセスが容易でありながら、長寿命を達成可能なデバイスを提供する。

【解決手段】モリブデン錯体の反応生成物又はタングステン錯体の反応生成物であり、モリブデン錯体又はタングステン錯体が、カルボニル基及び水酸基の少なくとも1つを有する有機溶媒と酸化還元反応して得られたモリブデン又はタングステン含有有機−無機複合酸化物である、正孔注入輸送層形成用材料を用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性が良好な半導体装置及びその作製方法を提供する。

【解決手段】絶縁層上に形成された酸化物半導体層と、酸化物半導体層の一部と重なるソース電極層及びドレイン電極層と、酸化物半導体層の一部と接するゲート絶縁層と、ゲート絶縁層上にゲート電極層と、を有するトランジスタにおいて、ソース電極層と酸化物半導体層、及びドレイン電極層と酸化物半導体層のそれぞれの間にn型の導電型を有するバッファ層を形成することで、寄生抵抗を低減させ、トランジスタのオン電流特性を向上させる。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

有機薄膜半導体装置及びその製造方法

【課題】製造プロセスを簡便なものとしつつ、高移動度、低コンタクト抵抗、低閾電圧及び低サブシュレッシュホールド値を同時に実現する高性能の有機薄膜半導体装置及びその製造方法を提供すること。

【解決手段】本発明の有機薄膜半導体装置は、ボトムコンタクト型であって、前記電極の側面のうち、少なくとも前記絶縁層に接する位置に、前記有機半導体層側から前記絶縁層側に向けて幅広となるテーパ状の勾配を有する電極端部が形成され、前記電極端部の前記絶縁層の層方向に対する前記勾配の傾きで表わされる立ち上がり角度が、下記式(1)で決定される前記有機半導体層を形成する有機分子の成長許容角度θmax(度)以下であることを特徴とする有機薄膜半導体装置。

θmax=tan−1(e/d) ・・・(1)

ただし、前記式(1)において、dは、前記有機分子の結晶粒の厚みを示し、eは、前記有機分子1層分の厚みを示す。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、および電子機器

【課題】基板やゲート絶縁膜の露出表面と、ソース電極およびドレイン電極の露出表面とに、良好で均一な膜質の半導体薄膜を設けることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1aは、有機材料または酸化物材料またはシリコン系材料からなるゲート絶縁膜(絶縁層)15上に、導電性酸化物材料からなる酸化物材料層17-aとこの上部の金属材料層17-bとからなるソース電極およびドレイン電極が設けられたものである。そしてゲート絶縁膜(絶縁層)15とソース電極17sおよびドレイン電極17dとにおける酸化物材料層17-aとの露出面が、自己組織化膜19で覆われており、この自己組織化膜19で覆われた上部のソース電極17s−ドレイン電極17d間にわたって半導体薄膜21が設けられている。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

配線構造体、半導体素子、配線基板、表示用パネル及び表示装置

【課題】 酸化物電極との良好な接続を行うことや、絶縁膜等との界面で生じる相互拡散を抑制することができ、かつ製造工程の低コスト化を図ることができる配線構造体、それを用いた半導体素子、配線基板、表示用パネル及び表示装置を提供する。

【解決手段】 アルミニウム層、銅層及び銅合金層からなる群より選択される少なくとも1つの層と、アルミニウム合金層とを含む2層以上の積層体であり、該アルミニウム合金層が表層に配置されている配線構造体である。これにより、液晶表示装置等において、酸化物電極と配線との接続部で酸化膜が形成されず、良好な接続を行うことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体装置

【課題】SOI構造の単結晶半導体層(SiGe層/歪みSi層/SiGe層)上のMISFETの提供

【解決手段】半導体基板1に選択的に設けられた第1のトレンチの下部側面及び底面に絶縁膜3が設けられ、側面絶縁膜3間の底面絶縁膜3上に空孔4が設けられ、空孔4及び側面絶縁膜3上には単結晶半導体層が設けられ、半導体層は絶縁膜2が埋め込まれた第2のトレンチにより、島状に絶縁分離され、歪みSi層6直上にはゲート酸化膜11を介してゲート電極12が設けられ、半導体層には、ゲート電極12に自己整合してn型ソースドレイン領域(8、9)が、ゲート電極12の側壁のサイドウォール13に自己整合して、n+型ソースドレイン領域(7、10)がそれぞれ設けられ、ゲート電極12(配線図示せず)及びn+型ソースドレイン領域にはバリアメタル16を有する導電プラグ17を介してバリアメタル19を有する配線20が接続されているMISFET。

(もっと読む)

半導体装置、表示装置、および電子機器

【課題】ソース電極/ドレイン電極と有機半導体層との接触が強固なトップコンタクト構造において、有機半導体層の膜質を確保しつつチャネル領域に対するコンタクト抵抗(注入抵抗)の低減を図る。

【解決手段】基板11上のゲート電極13と、ゲート電極13を覆うゲート絶縁膜15と、ゲート電極13の幅の範囲内でゲート絶縁膜15を介してゲート電極13の上部に重ねて配置された有機半導体層17と、ゲート電極13を幅方向に挟んだ状態で有機半導体層17上において端部が対向配置されたソース電極19sおよびドレイン電極19dとを備えた半導体装置1。

(もっと読む)

半導体膜の作製方法、半導体装置の作製方法、及び光電変換装置の作製方法

【課題】抵抗率の低い不純物元素を有する非晶質半導体を形成する。また、電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】プラズマCVD法により不純物元素を有する非晶質半導体を形成する方法において、パッシェンの法則で最小放電開始電圧を満たす圧力及び電極間隔において、パルス変調した放電開始電圧を電極に印加することより、抵抗率の低い不純物元素を有する非晶質半導体を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

101 - 120 / 732

[ Back to top ]