Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

181 - 200 / 732

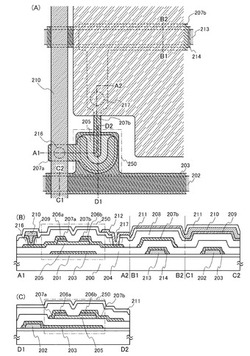

半導体装置及び半導体装置の作製方法

【課題】表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

半導体装置

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】ゲート電極層と、ゲート電極層上の膜厚100nm以上350nm以下のゲート絶縁層と、ゲート絶縁層上の酸化物半導体層と、酸化物半導体層上のソース電極層及びドレイン電極層と、酸化物半導体層を含む薄膜トランジスタと、ソース電極層及びドレイン電極層上に酸化物半導体層の一部と接する酸化シリコン層とを有し、薄膜トランジスタは温度85℃で、12時間、ゲート電極層に30V、又は−30Vの電圧を印加する測定において、測定前と測定後の薄膜トランジスタのしきい値電圧の値の差が1V以下である半導体装置とする。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トランジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一とする。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層のうち、酸化物半導体層と接する一層を薄いインジウム層または薄いインジウム合金層とする。なお、酸化物半導体層は、インジウムを含む。二層目以降のソース電極層またはドレイン電極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置、および電子機器

【課題】移動度の高い低分子系の有機半導体材料を用いた構成にも適用可能で、かつトランジスタ特性が良好でありながらもソース/ドレイン電極と有機半導体層との間の接続抵抗が小さく高性能な薄膜トランジスタを提供する。

【解決手段】疎水性のゲート絶縁膜15で覆われた基板11上に、一対の親水化パターン19を設け、この上部にカーボンナノチューブを用いて構成されたソース電極21sおよびドレイン電極21dが選択的に設けられている。ソース電極21s−ドレイン電極21d間には、有機半導体層23が設けられている。有機半導体層23は、ペンタセンからなる。

(もっと読む)

表示装置、および電子機器

【課題】画素にメモリを有する画素を備えた表示装置を提供する。

【解決手段】画素に、少なくとも、表示素子、容量素子、インバータおよびスイッチを設ける。容量素子に保持された信号と、インバータから出力される信号とを用いて、スイッチを制御することにより、表示素子に電圧が供給されるようにする。インバータおよびスイッチを同じ極性を持つトランジスタで構成することができる。また、画素を構成する半導体層を透光性を有する材料で形成してもよい。また、ゲート電極、ドレイン電極および容量電極を透光性を有する導電層を用いて形成してもよい。このように透光性材料で画素を形成することで、メモリが配置された画素を有していながら、その表示装置を透過型にすることができる。

(もっと読む)

トランジスタ及び表示装置

【課題】電気特性が良好で信頼性の高い薄膜トランジスタをスイッチング素子として用いて信頼性の高い表示装置を作製することを課題の一つとする。

【解決手段】非晶質の酸化物半導体を用いたボトムゲート型の薄膜トランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層と金属材料で形成されるソース電極層及びドレイン電極層のそれぞれの間には、結晶領域を有する酸化物導電層が形成されている。これにより、酸化物半導体層とソース電極層及びドレイン電極層間の接触抵抗を低減することができ、電気特性が良好な薄膜トランジスタ及び、それを用いた信頼性の高い表示装置を提供することができる。

(もっと読む)

配線構造およびそれを備えた表示装置

【課題】銅配線層の接着性を改善するとともに、銅配線層の抵抗値が大きくなることを抑制する配線構造を提供する。

【解決手段】配線構造10では、ガラス基板11上に、チタンからなる接着層12と、酸化銅からなるバリア層13と、純銅からなる銅配線層14とが順に積層されている。接着層12は、銅配線層14をガラス基板11に確実に接着させて、銅配線層14がガラス基板11から剥がれるのを防止する。バリア層13は、配線構造10を熱処理したときに、接着層12を構成するチタン原子が銅配線層14内に拡散しないようにして、銅配線層14の抵抗値が大きくならないようにする。このため、銅配線層14は、熱処理された後も、比抵抗を小さな値に保つことができるので、信号の遅延を防止できる。

(もっと読む)

発光装置及び発光装置の作製方法

【課題】発光装置の信頼性を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路用トランジスタを含む駆動回路部と、画素用トランジスタを含む画素部とを有する発光装置であり、駆動回路用トランジスタ及び画素用トランジスタは、酸化物絶縁層と一部接する酸化物半導体層を含む逆スタガ型のトランジスタである。画素部において酸化物絶縁層上にカラーフィルタ層と発光素子が設けられ、駆動回路用トランジスタにおいて、酸化物絶縁層上にゲート電極層及び酸化物半導体層と重なる導電層が設けられる。なお、ゲート電極層、ソース電極層及びドレイン電極層は金属導電膜を用いる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置、および電子機器

【課題】有機半導体層とソース電極/ドレイン電極との間のコンタクト抵抗を図りながらも微細化プロセスの適用が可能でかつ良好な特性を有する薄膜トランジスタを提供する。

【解決手段】トップコンタクト・ボトムゲート構造の薄膜トランジスタにおいて、有機半導体層17とソース電極21s/ドレイン電極21dとの間に、有機半導体材料と共にアクセプタ性材料またはドナー性材料を含有するコンタクト層19を設けた。有機半導体層17の導電型がp型である場合には、コンタクト層19にはアクセプタ性材料が含有されている。コンタクト層19は、有機半導体層17と同一のパターン形状を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 ソース・ドレイン電極の加工にドライエッチングを用いてトップコンタクト型TFTを形成する際のTFT特性バラツキの増大、歩留まりの低下、さらにはTFTオン電流の低減を抑制することにある。

【解決手段】 薄膜トランジスタの製造方法において、金属酸化物半導体から成る導電層上に金属酸化物半導体から成る犠牲層を形成し、前記犠牲層上に金属膜を形成し、前記金属膜をドライエッチングにより加工し、前記ドライエッチングにより露出した前記犠牲層へウェットエッチングを行なう。

(もっと読む)

発光装置およびその作製方法

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複数種の薄膜トランジスタを備えた発光装置を提供することを課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャネルストップ型を用い、画素用薄膜トランジスタと電気的に接続する発光素子と重なる位置にカラーフィルタ層を薄膜トランジスタと発光素子の間に設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】基板側から順に、Al合金膜と、当該Al合金膜と直接接続する薄膜トランジスタの酸化物半導体層と、を有し、TiやMoなどの高融点金属を省略してAl合金膜を酸化物半導体層と直接接続しても低コンタクト抵抗を実現できる新規な表示装置用Al合金膜を有する配線構造を提供する。

【解決手段】上記配線構造において、半導体層は酸化物半導体からなり、Al合金膜は、Niおよび/またはCoを含むものである。

(もっと読む)

半導体装置及びその作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5ラ1010dyn/cm2 〜5ラ1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】基板側から順に、絶縁膜と、Cu合金膜と、薄膜トランジスタの酸化物半導体層と、を備えた配線構造であって、TiやMoなどのバリアメタル層を省略してCu合金膜を、基板および/または絶縁膜と電気的に直接接続しても、これらとの密着性に優れており、しかもCu系材料の特徴である低電気抵抗、並びに酸化物半導体層および/または画素電極を構成する透明導電膜との低いコンタクト抵抗を実現できる新規な表示装置用Cu合金膜を有する配線構造を提供する。

【解決手段】本発明の配線構造において、Cu合金膜は、Mn、Ni、Zn、Al、Ti、Mg、Ca、W、およびNbよりなる群から選択される少なくとも1種の元素を含有している。上記Cu合金膜は、基板および/または絶縁性、並びに半導体層と直接接続されている。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、半導体層と例えばソース電極やドレイン電極を構成するAl系膜とを安定して直接接続させることが可能であるとともに、ウェットプロセスで用いる電解質液中で、半導体層とAl系膜との間でガルバニック腐食が生じにくく、Al系膜の剥離を抑制することのできる配線構造を提供する。

【解決手段】基板1の上に、基板1側から順に、薄膜トランジスタの半導体層4と、半導体層4と直接接続するAl合金膜6と、を備えた配線構造であって、半導体層4は酸化物半導体からなり、Al合金膜6は、Niおよび/またはCoを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 酸化物半導体においてはイオン注入法による拡散層形成が難しいため、バルクシリコンMOSトランジスタや多結晶シリコンTFTのようなイオン注入法を用いた自己整合プロセスを組むことができない。本願では、リフトオフを用いる場合のような不都合の生じない自己整合プロセスを酸化物半導体において実現することを課題とする。

【解決手段】 裏面露光により製造される薄膜トランジスタ(TFT)において、チャネル層として酸化物半導体を用い、基板上の電極をマスクとして、基板の裏面側から導電膜上のネガレジストを露光し、ネガレジストの露光部分を残し前記ネガレジストを除去し、露光部分をエッチングマスクとする導電膜のエッチングにより、電極を加工する。

(もっと読む)

181 - 200 / 732

[ Back to top ]